Fターム[5F140BG31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644)

Fターム[5F140BG31]の下位に属するFターム

イオン注入 (445)

Fターム[5F140BG31]に分類される特許

81 - 100 / 199

半導体装置の製造方法

【課題】半導体装置の製造コストを低減する。

【解決手段】半導体装置の製造方法は、高誘電率膜が形成された基板を処理室内に搬入するステップと、前記処理室に接続されたプラズマユニットによるプラズマによって活性化した窒素原子を含むガスを前記処理室内に供給して前記高誘電率膜に対してプラズマ窒化処理を施すステップと、前記処理室内に成膜ガスを供給して前記プラズマ窒化処理後の高誘電率膜上に電極膜を形成するステップと、前記電極膜形成後の基板を前記処理室内から搬出するステップと、前記プラズマユニットによるプラズマによって活性化したクリーニングガスを前記処理室内に供給して前記処理室内をクリーニングするステップと、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 中耐圧半導体素子と小耐圧半導体素子が混載された半導体装置を製造する方法を提供する。

【解決方法】 中耐圧PMOS12のウェル浅層82、86、90にN型不純物を注入する工程では、ウェル浅層82、86、90が分割して形成されているので、第1ドリフト領域84と第2ドリフト領域88にN型不純物が注入されない。ウェル深層94にN型不純物を注入する工程では、注入エネルギーを指定して不純物を注入することで、第1ドリフト領域84と第2ドリフト領域88にN型不純物が注入されない。これにより第1ドリフト領域84と第2ドリフト領域88に注入するP型不純物濃度をウェル浅層82、86、90とウェル深層94のN型不純物濃度より薄くすることができる。また、ウェル浅層82、86、90のN型不純物濃度を濃く設定することができ、小耐圧PMOS10のウェル領域60と同時に不純物を注入することができる。

(もっと読む)

半導体装置

【課題】最も外側の溝部の下端部の外側部分近傍に電界集中が発生するのを抑制することが可能な半導体装置を提供する。

【解決手段】このパワーMOSFET(半導体装置)100は、ドレイン領域2と、ドレインドリフト領域3と、ドレイン領域2の引き出し部15と、ドレインドリフト領域3上に形成されたベース領域9と、ベース領域9上に形成されたソース領域10と、ソース領域10およびベース領域9と一方側面61aが隣接するように形成された溝部6a内に、ゲート絶縁膜7を介して形成されたゲート電極8と、溝部6aと引き出し部15との間において、溝部6aの他方側面62aと隣接するように形成されるとともに、溝部6aの下端部63aよりも下方に延びるように形成された不純物領域11とを備えている。

(もっと読む)

MOS型半導体装置およびMOS型半導体装置の製造方法

【課題】従来の同一サイズのMOS型半導体装置と比較してゲート耐圧およびソース−ドレイン間耐圧を向上させることができるMOS型半導体装置およびその製造方法を提供する

【解決手段】半導体基板と、半導体基板上にゲート酸化膜を介して形成されたゲート電極と、半導体基板の内部においてゲート酸化膜下方のチャンネル領域を挟む位置に設けられ半導体基板の導電型とは異なる導電型の不純物を含む1対の低濃度不純物拡散領域と、低濃度不純物拡散領域の各々の内部にあって且つゲート電極のゲート長方向においてチャンネル領域から離間しており低濃度不純物拡散領域と同一の導電型であり且つ低濃度不純物拡散領域よりも高濃度の不純物を含む1対の高濃度不純物拡散領域と、を有するMOS型半導体装置であって、ゲート酸化膜は、ゲート電極のゲート長方向両端部に他の部分よりも膜厚の厚い高膜厚部を有し、高濃度不純物拡散領域のチャンネル領域を挟んで向かい合う端部の各々が高膜厚部の直下に位置している。

(もっと読む)

半導体装置の製造方法、半導体装置および半導体層の形成方法

【課題】半導体上にモフォロジの良好な半導体層を選択的にエピタキシャル成長させる。

【解決手段】リセスド・ソース・ドレイン型pMOSFETを形成する際、STIを形成したSi基板上にゲート絶縁膜を介してゲート電極を形成し(ステップS1)、サイドウォールを形成した後(ステップS2)、その両側のSi基板に部分的にリセスを形成する(ステップS3)。そして、そのSi基板のリセス内に、下層部の方が上層部よりも、サイドウォールやSTIに対する成長選択性が低くなるような条件を用いて、下層部と上層部をエピタキシャル成長させ、SiGe層を形成する(ステップS4,S5)。これにより、Si基板のリセス内に、サイドウォール等に対する成長選択性を確保しつつ、モフォロジの劣化が抑えられたSiGe層を形成することが可能になる。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、表面にバッファ層が形成された基板と、エピタキシャル成長によってバッファ層上に形成された、所定の導電型を有する電界緩和層と、電界緩和層上の一部領域に形成された、所定の導電型とは反対の導電型を有する半導体層と、半導体層の中または表面に形成された、所定の導電型と同一の導電型を有するコンタクト層と、コンタクト層上に形成されたソース電極と、電界緩和層上に形成されたドレイン電極と、半導体層上に該半導体層の端面と重畳するように形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体層の端面と重畳するように形成されたゲート電極と、を備え、半導体層の端面近傍に形成されるチャネルと電界緩和層とが電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】拡散層領域を細く形成する場合でも、拡散層領域の縮みによるコンタクト抵抗の増大を抑えることを可能とした半導体装置の製造方法を提供する。

【解決手段】素子分離領域によって分離された拡散層領域5を形成する際に、2重露光技術を用いて拡散層領域5を2段階に分けて形成する。これにより、拡散層領域5を細く形成する場合でも、拡散層領域5の長手方向の両端における縮みを抑制することができ、拡散層領域5の長手方向における両端と、コンタクトホール12に埋め込まれたコンタクトプラグ13との接続面積を確保しながら、コンタクト抵抗の上昇を抑えることが可能である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】P型MOSトランジスタにおいて優れたNBTI信頼性が得られ、また、簡易な工程で製造することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】N型MOSトランジスタ4aとP型MOSトランジスタ4bを有する半導体装置において、P型MOSトランジスタ4bのゲート電極6bを、P型ドーパントを含有するポリシリコンを主材料とし、少なくともゲート絶縁膜5との界面近傍にN型ドーパントを含有するように構成する。このような半導体装置は、ゲート絶縁膜5が形成されたNMOSトランジスタ形成領域2a及びP型MOSトランジスタ形成領域2bに、ゲート電極となるポリシリコン層を、N型ドーパントを含有する第1ポリシリコン層とドーパントを実質的に含まない第2ポリシリコン層のスタック構造で形成し、各領域に、それぞれ、N型ドーパント、P型ドーパントをイオン注入する工程を用いて製造できる。

(もっと読む)

半導体装置

【課題】複数のフィンと、これらフィン側面の半導体層を有しつつ、隣接する他の素子への接触を防止しうる半導体装置を提供する。

【解決手段】本発明の実施の形態による半導体装置1は、半導体基板2と、半導体基板2上に所定の間隔を置いて互いに略平行に配置された複数のフィン3a、3b、3cと、複数のフィン3a、3b、3cの各々の両側面をゲート絶縁膜7を介して挟むように形成されたゲート電極4と、複数のフィン3a、3b、3cの少なくとも一部の側面上に形成される半導体層としてのエピタキシャル層9と、を有し、エピタキシャル層9は、複数のフィン3a、3b、3cのうちの両端に位置する2つのフィン3a、3cの外側側面上に位置する領域における厚さが、前記外側側面の反対側の側面上に位置する領域における厚さよりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】STI法を用いて形成した素子分離領域の幅が狭く、かつ溝ゲート構造を有する半導体デバイスを製造するにあたり、絶縁体中に存在するボイドによるゲート電極間のショートを防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板をパターニングして素子分離用溝を形成する工程と、素子分離用溝に絶縁体を埋め込んで素子分離領域を形成する工程と、CMP法により表面を平坦化して、フィールド形成用絶縁膜を露出させる工程と、絶縁体の上部を除去する工程と、フィールド形成用絶縁膜を除去する工程と、素子分離領域が形成された半導体基板をパターニングして、ゲート電極を形成する領域にゲート溝を形成する工程と、絶縁体の内部に存在しているボイドの上部を開口させる工程と、ゲート溝内にゲート電極を形成する工程とを有する方法で半導体装置を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】界面準位を低減し、特性変動及びリーク電流の少ない半導体製造装置及びその製造方法を提供する。

【解決手段】半導体基板1上に拡散層4を形成し、拡散層4内の上部にソース拡散領域10a及びドレイン拡散領域を形成し、拡散層4の上に、ゲート絶縁膜5を介してゲート電極8を形成し、ゲート電極8の上に保護膜13を形成し、保護膜13を覆うように絶縁層14を形成し、絶縁層14内に、保護膜13を介してゲート電極8の側面に多結晶シリコンプラグ15を形成し、その下方はゲート絶縁膜5及びゲート絶縁膜5と接している部分の保護膜13を貫通して、ソース拡散領域10aまたはドレイン拡散領域にそれぞれ連結させ、保護膜13中にフッ素を注入し、フッ素をゲート絶縁膜15と拡散層4との間のシリコン‐絶縁膜界面まで拡散させることを特徴とする。

(もっと読む)

半導体装置

【課題】素子特性のばらつきが抑制されたMOS型素子を含む半導体装置を提供すること。

【解決手段】基板の半導体領域に埋め込まれた素子分離絶縁膜と、前記素子分離絶縁膜によって素子分離され、上部が前記素子分離絶縁膜の表面よりも上に突出し、前記半導体領域の半導体層と、この半導体層にソース・ドレイン領域、ゲート絶縁膜およびゲート電極が形成され、かつ、前記ゲート電極がチャネル幅方向に平行な面の断面において前記素子分離絶縁膜上に形成されてなるMOS型素子とを具備してなり、前記ゲート電極下の前記半導体層の上面位置が、前記ゲート電極下の前記素子分離絶縁膜の上面位置よりも、20nm以上高いことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】素子の更なる微細化が進行することがあっても、シリサイドの突き抜けによる接合リークが発生することを防止する。

【解決手段】MISトランジスタを備えた半導体装置であって、MISトランジスタは、半導体基板100上における活性領域100aに形成されたゲート絶縁膜102と、ゲート絶縁膜102上に形成されたゲート電極103と、ゲート電極103の側面上に形成されたサイドウォール105と、活性領域100aにおけるサイドウォール105の側方下に位置する領域に形成されたソース・ドレイン領域106と、ソース・ドレイン領域106の上部にサイドウォール105と隣接して形成された第1のシリサイド層108aと、ソース・ドレイン領域106の上部に第1のシリサイド層108aと隣接して形成され、第1のシリサイド層108aの膜厚よりも厚い膜厚を有する第2のシリサイド層112Bとを備えている。

(もっと読む)

半導体装置及びコンデンサ

【課題】La2O3の強い吸湿性を改善し、高い耐湿性及び安定性を有する半導体装置及びコンデンサを提供する。

【解決手段】高誘電率絶縁膜12が(La1−xMx)2O3(0<x≦0.3、MはSc、Y、Hf、Ti、Ta、Al、Nbの群から選ばれる1又は2以上の金属)で表記される組成からなることにより、吸湿性が改善し、安定性が向上する。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

ポリシリコン層及び層構造のパターニング方法

【課題】金属或いは金属シリサイド層を多結晶シリコン層の上に含む層構造のパターニング方法において、ドーピング物質が全析出面にわたって均質に分布され、その表面性質及び隣接の層との接着性ができるだけ良くなる方法を提供する。さらに、高い選択性と、大きな均質性とをもって、かつエッチングされる全ての層にわたって真っ直ぐにエッチングされた側面部を形成するようにパターニングする方法を提供する。

【解決手段】ドーピング化合物がプロセスガスとしてポリシリコンの化学気相蒸着の際に添加され、そのプロセスガスへの供給が気相蒸着の終了近くで停止され、その結果非ドープのシリコンからなる境界層が析出される。このパターニング法は、少なくとも3段階のエッチングプロセスを含み、第一の段階ではフッ素を含むガスが、第二の段階では塩素を含むガスが、第三の段階では臭素を含むガスがエッチングのために使用される。

(もっと読む)

半導体装置

【課題】円柱型構造のトランジスタの特性を向上させる。

【解決手段】導電層の形成された基板において前記導電層上に形成された柱状半導体と、前記柱状半導体の周囲に形成された絶縁層と、前記絶縁層の周囲に形成された一つのトランジスタのゲート電極を有しており、ゲート電極は、仕事関数の異なる少なくとも2層以上の導電膜の積層構造により構成されていることを特徴とする半導体装置を提供することにより、上記課題を解決する。

(もっと読む)

埋込方法、半導体素子製造方法および半導体素子

【課題】メサ形状である第1の材料層の周囲に第2の材料を空隙なく平坦に埋め込むことができる埋込方法、半導体素子製造方法、および、メサ形状である第1の半導体層の周囲に第2の半導体が空隙なく平坦に埋め込まれた半導体素子を提供すること。

【解決手段】本発明にかかる埋込方法は、基板上に形成された第1の材料層上にエッチングマスクを形成するマスク形成工程と、エッチングマスク周縁が所定幅分突出するように第1の材料層をメサ形状にドライエッチングするエッチング工程と、エッチング工程後に第2の材料によってメサ形状周囲を選択的に埋め込む埋込工程と、エッチングマスクを除去するマスク除去工程と、を含むことを特徴とする。

(もっと読む)

多重拡散防止膜を備える半導体素子

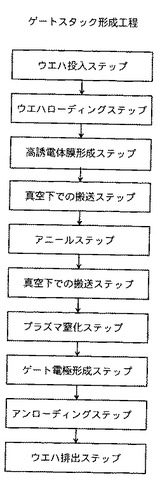

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子を提供すること。

【解決手段】第1導電層(211)と、第1導電層(211)上に形成され、且つ金属シリサイド膜(212A)及び窒素含有の金属膜(212B)の順に積層された第1拡散防止膜と、該第1拡散防止膜上の少なくとも窒素含有の金属シリサイド膜(212D)を含む第2拡散防止膜と、該第2拡散防止膜上の第2導電層(213)とを備える。

(もっと読む)

半導体装置

【課題】ソース−ドレイン間の耐圧を確保しつつ、その間隔の微細化を可能にした半導体装置を提供する。

【解決手段】半導体装置は、P型シリコン基板1上に形成したN型エピタキシャルシリコン層5および両者の界面に埋設したN型埋込拡散層3からなる半導体基板と、N型エピタキシャルシリコン層5の主表面SからN型埋込拡散層3に達するトレンチ17と、トレンチ17内の側面を被覆するシリコン酸化膜18と、このシリコン酸化膜18を介してトレンチ17内を埋め込むとともにN型埋込拡散層3に接続する引き出し層19と、同主表面Sに設けたトレンチ9と、このトレンチ9内にシリコン酸化膜10aを介して設けたゲート電極11と、トレンチ9の両側面に設けたN型ソース拡散層13と、同主表面Sにおいてトレンチ17とN型ソース拡散層13との間に設けたトレンチ17aと、このトレンチ17a内に充填したシリコン酸化膜18aと、を備える。

(もっと読む)

81 - 100 / 199

[ Back to top ]