Fターム[5F140BG31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644)

Fターム[5F140BG31]の下位に属するFターム

イオン注入 (445)

Fターム[5F140BG31]に分類される特許

21 - 40 / 199

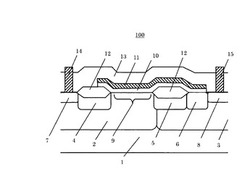

半導体装置

【課題】高耐圧で大きな電流駆動能力をもつLOCOSオフセット型MOS型電界効果トランジスタを提供する。

【解決手段】LOCOSオフセット型MOS型電界効果トランジスタのドレイン側のオフセット領域に、LOCOS酸化膜を伴うN型第1低濃度ドレインオフセット領域5と、LOCOS酸化膜を伴わないN型第2低濃度ドレインオフセット領域6を設け、共にゲート電極で覆うように設けたので、N型第1低濃度ドレインオフセット領域5でオフセット領域にかかる電界を緩和し高耐圧を得て、N型第2低濃度ドレインオフセット領域6でオフセット領域のキャリアを増加させ大きな電流駆動能力を得ることができる。

(もっと読む)

リセスゲート構造を有する絶縁ゲート型炭化珪素ラテラル電界効果トランジスタ

【課題】短チャネル化を可能とし、オン抵抗と寄生容量の低減を図った絶縁ゲート型炭化珪素ラテラル電界効果トランジスタを提供する。

【解決手段】ドリフト領域(5)表面の一部に電界緩和領域(9)を設け、ソース領域(3)とドリフト領域(5)との間に凹部(リセス)(8)を形成したリセスゲート構造を有し、凹部(リセス)(8)底面の両端部近傍にソース領域(3)、ドリフト領域(5)の薄い領域(3a、5a)を設ける。

(もっと読む)

リセスゲート型炭化珪素電界効果トランジスタおよびその製造方法

【課題】短ゲート(チャネル)化しても短チャネル効果を抑制し、オン抵抗の低いSiC MISFETを得る。

【解決手段】一導電型のSiC半導体領域(2)内にソース、ドレイン領域(3、4)を形成し、ソース、ドレイン領域で挟まれたSiC半導体領域部分に形成され、ソース、ドレイン領域に接する二つの側面と両側面を接続する底面とからなる所定深さの凹部(リセス)(5)を形成し、凹部底面の両端近傍に隣接するソース、ドレイン領域の一部(3a、4a)を他の部分より薄くしたSiC MISFET。

(もっと読む)

半導体装置を製作する方法

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を製作する方法を提供する。

【解決手段】複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

半導体装置

【課題】MOSトランジスタの高耐圧化、オン抵抗の低減、HCI耐性の向上、及びデザインルールの縮小を実現する。

【解決手段】MOSトランジスタのドレインは、チャネル長方向で一端がP型低濃度ウェル3内に配置され、他端がP型ウェル5内に配置されたN型低濃度ドレイン7と、低濃度ウェル3上の低濃度ドレイン7内に低濃度ドレイン7の端部とは間隔をもって配置されたN型高濃度ドレイン9からなる。ソースは、チャネル長方向で一端が低濃度ドレイン7とは間隔をもって低濃度ウェル3内に配置され、他端がウェル5内に配置されたN型高濃度ソース11と、低濃度ウェル3内で高濃度ソース11に隣接し、低濃度ドレイン7とは間隔をもって配置されたN型低濃度ソース13からなる。ゲート電極19は、高濃度ドレイン9−低濃度ソース13間の低濃度ウェル3上及び低濃度ドレイン7上に高濃度ドレイン9とは間隔をもって配置されている。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法

【課題】デュアルゲート不純物ドーピング方法及びこれを用いたデュアルゲート形成方法を提供する。

【解決手段】デュアルゲート不純物ドーピング方法は、第1領域及び第2領域を有する半導体基板上のゲート導電膜に第1導電型の不純物イオンをドープする段階であって、ゲート導電膜の下部よりも上部における不純物ドーピング濃度がより高い濃度勾配でドープする段階と、第2領域のゲート導電膜をオープンさせるマスクを用いて第2領域のゲート導電膜に第2導電型の不純物イオンをドープする段階と、熱処理を行い、第1導電型及び第2導電型の不純物イオンを拡散させる段階と、を含む。

(もっと読む)

電界効果トランジスタ

【課題】大電流を安定して継続的に流すことができる電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ10は、III族窒化物半導体から成る半導体活性層13の表面領域に形成されたソース18s及びドレイン18dと、半導体活性層13上にゲート酸化膜14を介して形成されたゲート電極15と、ゲート電極15とドレイン18dの間の半導体活性層13上に形成されたパッシべーション膜20とを備える。電界効果トランジスタ10では、パッシベーション膜20を構成する二酸化シリコンの膜質が、ゲート酸化膜14を構成する二酸化シリコンの膜質よりも密度が粗である。

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子サイズの拡大を伴うことなくゲート−ドレイン間(又はゲートソース間)耐圧を確保できる半導体装置とその製造方法を提供する。

【解決手段】基板表面のドレイン側又はソース側の少なくとも一方にLOCOS膜を形成する工程と、基板表面に、LOCOS膜に接続されたゲート酸化膜を形成する工程と、ゲート酸化膜とLOCOS膜を覆う導電膜の形成工程と、導電膜の端部がLOCOS膜の上に位置するように導電膜をエッチングするゲート電極の形成工程と、ゲート電極の端部とエッチング端面が揃うようにLOCOS膜とゲート酸化膜をエッチングして、基板表面のLOCOS膜を除去した部分に凹部を形成する工程と、ゲート電極の側壁を覆い、その底面が凹部の底面と接するようにサイドウォールスペーサを形成する工程と、基板表面のゲート電極とサイドウォールスペーサを挟む位置に不純物を添加して、ドレイン及びソース領域の形成工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

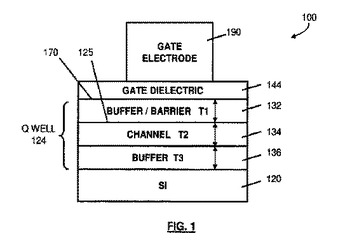

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の同一サイズの半導体装置と比較してゲート耐圧を向上させるとともに、素子分離層をバーズビークを含まない構造とすることにより素子分割領域の面積を縮小し、素子の微細化を図ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板表面に素子形成領域から素子分割領域に亘って延在するLOCOS膜を形成する。素子形成領域内の半導体基板上にLOCOS膜に接続されたゲート酸化膜を形成する。LOCOS膜およびゲート酸化膜を覆うように導電膜を形成する。導電膜を部分的にエッチングしてゲート酸化膜およびLOCOS膜の一部を覆うゲート電極を形成する。導電膜のエッチングによって露出したLOCOS膜を部分的にエッチングしてLOCOS膜を素子分離層とゲート酸化膜の端部を構成する高膜厚部とに分割する。LOCOS膜のエッチングによって露出した半導体基板の表面にイオン注入を行ってゲート電極を挟む位置にドレイン領域およびソース領域を形成する。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介して保護ダイオードおよびゲート電極と接続する。非重畳領域下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減でき、ソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。非重畳領域下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、ゲートパッド部から保護ダイオードまでの距離が、ソースパッド部から保護ダイオードまでの距離より小さくなる位置に保護ダイオードを配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方にはトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、ソース電極層を基板水平方向に流れる電流の経路において、素子領域内で抵抗の偏りが発生する問題もあった。

【解決手段】電極構造を2層とし、2層目のゲート電極層(ゲートパッド部)の下方にトランジスタセルおよび1層目のソース電極層を配置する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介してゲート電極と接続する。ゲートパッド部下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減できる。またソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

電界効果トランジスタ、メモリセル、および電界効果トランジスタの製造方法

【課題】洗浄工程で活性領域が倒れたり、変形したりするのを防いだ電界効果トランジスタを提供する。

【解決手段】半導体基板の表面に、FETの動作時にチャネルが発生する部位を含む4つの柱状活性領域を有し、各々の柱状活性領域は梁フィールド酸化膜8により分離され、各々の柱状活性領域の側面に接するようにゲート絶縁膜10を介してゲート電極11aおよび11bが設けられ、柱状活性領域の上面にはドレイン電極に相当する上部拡散層14dと、シリコン基板1の表面にソース電極に相当する下部拡散層9a、9b、9cおよび9dとが設けられた構成である。

(もっと読む)

半導体装置およびその製造方法

【課題】高駆動能力をもった厚いゲート膜を有する高耐圧MOSトランジスタを有する半導体装置を提供する。

【解決手段】高耐圧を有するLOCOSオフセットMOS型トランジスタにおいて、第2導電型高濃度ソース領域4と第2導電型高濃度ドレイン領域5を形成する際に、ポリシリコンゲート電極をマスクにしてゲート酸化膜を除去しても、チャネル形成領域7上のゲート酸化膜6はエッチングされないように、ソース側にもソースフィールド酸化膜14を設け、第2導電型高濃度ソースフィールド領域13の距離を最適化したことで、高駆動能力をもった厚いゲート膜を有する高耐圧MOSトランジスタを得ることが出来る。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

21 - 40 / 199

[ Back to top ]