Fターム[5F140BG31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 不純物の導入 (644)

Fターム[5F140BG31]の下位に属するFターム

イオン注入 (445)

Fターム[5F140BG31]に分類される特許

41 - 60 / 199

半導体デバイス

【課題】特徴サイズの小さいMOSトランジスタとその製造方法を提供する。

【解決手段】本発明は、ショートチャネルの影響を低減し、薄くドープしたドレイン領域(LDD構造)を有さない。MOSトランジスタのゲート長さは1.25μm以下である。本発明のMOSトランジスタはゲート酸化物層を含み、この層は基板との間で平面状でかつストレスのないインタフェースを形成する。その結果、ホットキャリアの発生およびホットキャリアの悪影響が回避できる。LDD構造を省略したために、製造プロセスの複雑さが低下し、ソース−ドレインの直列抵抗が減り、その結果駆動電流と切り換え速度が改善された。

(もっと読む)

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧を要求されるMOSトランジスタおよびその製造方法を提供する。

【解決手段】LOCOS酸化膜を用いたオフセットMOSトランジスタにおいて、高耐圧が要求されるドレイン拡散層周辺のLOCOS酸化膜をエッチングし、LOCOS酸化膜が薄くなった領域の下方の半導体基板表面領域にまでドレイン拡散層を形成することによって、ドレイン拡散層端部がオフセット拡散層によってカバーされるため、ドレイン拡散層下部の領域で発生する電界集中を緩和することができ、50V以上の電圧下においても安全に動作しうるMOSトランジスタとなる。

(もっと読む)

半導体装置及びその製造方法

【課題】横型絶縁ゲートトランジスタ素子を備え、オン抵抗の増加を抑制しつつ体格を小型化することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体層に構成されたLDMOS素子と、半導体層の主表面上に形成された絶縁膜を同一表面から貫通するコンタクプラグとしての、ソース領域とベースコンタクト領域とに接続された第1コンタクトプラグと、を備えた半導体装置であって、ベースコンタクト領域が、半導体層の主表面に略垂直な方向においてソース領域よりも主表面に対して下方で、半導体層の主表面に沿う方向においてソース領域と少なくとも一部が重なる位置に形成されている。そして、第1コンタクトプラグが、絶縁膜及びソース領域を貫通しつつベースコンタクト領域まで延設されている。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

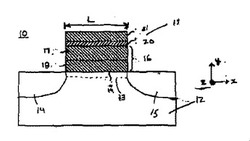

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】電子移動度が高く、リーク電流が小さく、オン抵抗が低い電界効果トランジスタおよび電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有する電界効果トランジスタであって、基板上に形成したp型窒化化合物半導体層と、ソース電極およびドレイン電極下部に位置し、イオン注入により形成されたn型コンタクト領域と、前記p型窒化化合物半導体層上にエピタキシャル成長によって積層されるとともに、一端部がドレイン電極側のn型コンタクト領域に隣接し、他の一端部がゲート電極の前記ドレイン電極側にオーバーラップするように形成され、前記n型コンタクト領域よりもキャリア濃度が低いn型窒化化合物半導体からなる電界緩和層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 空乏化が抑制されたゲート電極を備え、特性のばらつきが小さく十分な駆動能力を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における活性領域1a上に形成された第1のゲート絶縁膜5aと、第1のゲート絶縁膜5a上に形成され、第1導電型の不純物を含む多結晶シリコン膜からなる第1のゲート電極6aとを備えている。第1のゲート電極6aに含まれる第1導電型の不純物は、第1のゲート電極6aにおける第1のゲート絶縁膜5aとの界面部分に第1の濃度ピークを有し、且つ、第1のゲート電極6aの上面部分に第2の濃度ピークを有し、第1の濃度ピークは、第2の濃度ピークよりも濃度が大きい。

(もっと読む)

半導体装置

【課題】オン抵抗と耐圧のトレードオフを改善した半導体装置を提供することにある。

【解決手段】ソースドレイン方向に複数のトレンチをストライプ状に形成し、そのトレンチの側面および底面ならびにトレンチに挟まれた領域の上面にチャネル領域を形成する半導体装置とする。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間をCuプラグによって電気的に接続する構成において、Cuプラグとの電気的接続の信頼性が高く、リーク電流が少ない半導体装置、およびその製造方法を提供することを目的とする。

【解決手段】本発明における半導体装置100は、拡散層43およびゲート電極42を形成した半導体基板1と、半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5を貫通し、拡散層43およびゲート電極42上に形成されたコンタクトホール61と、コンタクトホール61の内面に形成されたTiバリアメタル層62と、バリアメタル層62上に形成されたW、Co、Ru、Ptのいずれかを含むシード層63と、シード層63上であってコンタクトホール61を充填するように形成されたCuプラグ64と、Cuプラグ64上に形成された配線層7と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】接触抵抗の増加が抑制されたピラー形状の縦型MOSトランジスタを用いた半導体装置を提供する

【解決手段】基部1aと複数のピラー部1Aとを有するシリコン基板1と、基部1aに設けられた一方のソースドレイン領域6と、ピラー部1Aの側面1bを覆うゲート絶縁膜4と、ゲート絶縁膜4を介してピラー部1Aの側面1bを覆うゲート電極5と、ピラー部1Aの上部に設けられた他方のソースドレイン領域12と、他方のソースドレイン領域12と接続されるコンタクトプラグ9とを備え、ピラー部1Aの上面1cの全面にコンタクトプラグ9が接続されていることを特徴とする半導体装置10。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧特性と電流増幅特性とに優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】電界緩和領域として機能するRESURF領域110を備えたRESURF−MOSFET100において、RESURF領域110と、ソース用コンタクトとして機能するn+型コンタクト領域104sと、ドレイン用コンタクトとして機能するn+型コンタクト領域104dとのうち少なくとも1つに、n型の導電性を有する原子と窒素原子とを不純物として含ませる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧を要求されるMOSトランジスタを含む半導体装置およびその製造方法を提供する。

【解決手段】LOCOSオフセットMOSトランジスタにおいて、LOCOS酸化膜の一部をエッチングした領域にドレイン拡散層を形成することにより、オフセット拡散層によってドレイン拡散層下部の電界集中が発生する領域がカバーされた50V以上の電圧下においても保証しうる高耐圧MOSトランジスタを含む半導体装置を提供することが可能となる。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、表面にp型不純物を注入したn型半導体層を順次積層し、熱処理により同時に拡散してp型ウェル領域とする。これにより、所望の耐圧を確保するのに十分な不純物濃度が所望の深さまで略均一なp型ウェル領域を得ることができる。

(もっと読む)

半導体装置及び半導体装置の製造方法並びにデータ処理システム

【課題】動作特性の制御が容易で微細化に有利なトランジスタを有する半導体装置およびその製造方法並びにデータ処理システムを提供する。

【解決手段】活性領域K内に設けられたトレンチ100と、トレンチ100と第1素子分離領域S1との間の活性領域Kに形成されたフィン型チャネル領域185と、第1素子分離領域S1に埋設され、第1ゲート絶縁膜141を介してフィン型チャネル185と接する第1ゲート電極151と、トレンチ100に埋設され、第2ゲート絶縁膜191を介してフィン型チャネル185と接する第2ゲート電極225と、フィン型チャネル185と接続され、活性領域K内において第2ゲート電極225を挟んでトレンチ100の両側に位置するソース/ドレイン拡散領域241とを具備してなるトレンチゲート型MOSトランジスタTrを有する半導体装置1を採用する。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

半導体装置の製造方法

【課題】バッチ式の反応炉を用いた場合でも、安定した特性を得ることができる半導体装置の製造方法を提供する。

【解決手段】供給ラインに原料ガスを流し始める(ステップS2)。供給ラインからMFCを通過した原料ガスは排気ラインに流れ、炉内供給ラインには流れない。その後、MFCを流れる原料ガスの流量が安定したかを判定する(ステップS3)。例えば、流量の変動幅が所定の範囲内に収まっているか判定する。流量が安定すると、バルブV1を開くと共に、バルブV2を閉じる(ステップS4)。この結果、供給ラインからMFCを通過した原料ガスは排気ラインに流れなくなり、炉内供給ラインに流れるようになる。続いて、所定時間が経過したかを判定する(ステップS5)。この所定時間は、形成しようとしているSiGe層の成長に必要とされる時間である。所定時間が経過すると、バルブV1を閉じると共に、バルブV2を開く(ステップS6)。

(もっと読む)

41 - 60 / 199

[ Back to top ]