Fターム[5F140BG33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248)

Fターム[5F140BG33]の下位に属するFターム

シリサイド化 (1,065)

Fターム[5F140BG33]に分類される特許

141 - 160 / 183

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層によりエクステンション層およびソース・ドレイン層が形成された半導体装置において、合金層と半導体基板間に生じる接合リークを防止して、信頼性を向上させた半導体装置およびその製造方法を提供する。

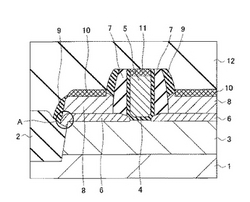

【解決手段】半導体基板1には、活性領域を区画する素子分離絶縁膜2が形成されており、活性領域における半導体基板1上にゲート絶縁膜4を介してゲート電極5が形成されている。ゲート電極5の両側における半導体基板1上には、エピタキシャル成長層により形成された2つのエクステンション層6と、2つのソース・ドレイン層8が積層されている。ソース・ドレイン層8における素子分離絶縁膜2側の端部には、当該端部における合金層の形成を防止する保護層9が形成されている。保護層9から露出したソース・ドレイン層8には、合金層10が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の端部近傍領域に自己整合的にオーバーラップし、電界緩和層として働く、低濃度拡散層を有する高耐圧MOSトランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 第1のN−低濃度拡散層105と、ゲート電極端部126を画定する熱酸化膜106とは、共に、シリコン窒化膜103からなるパターンをマスクとして自己整合的に形成され、更に、第1のN−低濃度拡散層105に隣接する第2のN−低濃度拡散層109は、ゲート電極108をマスクとして自己整合的に形成される。結果、電界緩和層として働く第1のN−低濃度拡散層105と、ポリシリコンゲート電極108の端部近傍領域に位置する熱酸化膜106とは、水平方向位置でみて、互いに自己整合的にオーバーラップしている。ポリシリコンゲート電極108の端部近傍領域にオーバーラップし、電界緩和層として働く第1のN−低濃度拡散層105が、ゲート電極端部126に自己整合的に形成される。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜へのダメージを抑制してゲートリーク電流を低減させ、且つp型ポリシリコンに近い仕事関数のゲート電極を有する半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上にゲート絶縁膜3を形成し、ゲート絶縁膜3上に450℃以下の温度でCVD法によりTiN膜4を形成し、このTiN膜4をエッチングしてゲート電極5を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗で耐熱性を有し、閾値変動もないCMOSデバイスを提案する。

【解決手段】本発明の例に関わる半導体装置は、N型半導体層3と、N型半導体層3上に形成される第1ゲート絶縁層10と、第1ゲート絶縁層10上に形成され、金属の炭素化合物を含む第1ゲート電極12とを有するPチャネルMISトランジスタ、及び、P型半導体層2と、P型半導体層2上に形成される第2ゲート絶縁層10と、第2ゲート絶縁層10上に形成される第2ゲート電極11とを有するNチャネルMISトランジスタを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 簡便な方法で製造することができ、しきい値電圧が適正な範囲に設定された半導体装置を提供する。

【解決手段】 第一の発明の半導体装置は、相補型であり、半導体基板、p型半導体装置およびn型半導体装置を具備する。p型半導体装置は、半導体基板上のn型半導体層と、n型半導体層上面に形成され、n型半導体層上面から下方に向けてp型ドーパントが補誤差関数で分布するp型ドーパント拡散領域と、p型ドーパント拡散領域上に形成され、Hfを含む第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、p型半導体化合物を有する第1のゲート電極と、p型ドーパント拡散領域をゲート長方向に挟み、p型ドーパント拡散領域に比して深くn型半導体層上面に形成された第1のソース・ドレイン領域と、を備えることを特徴とする。

(もっと読む)

半導体装置を製造する方法

基板を用意する工程であって、この基板に形成される誘電体層と、この誘電体層に形成され金属含有ゲート電極層と、を有するゲートスタックを含む当該基板を用意する工程;プラズマ中でプロセスガスから低エネルギー励起ドーパント種を生成する工程;および、前記ゲートスタックにドーパントを取り込むため、前記ゲートスタックを前記励起ドーパント種に晒す工程;を含む、半導体装置の製造工程におけるゲートスタックを処理する方法。この方法は、ゲートスタックの仕事関数を調整するために利用することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 隣接するゲート電極を狭ピッチで配置できる上、埋め込みによりシリコン基板面上での微細化を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 シリコン半導体基板1上に形成された隣り合うトランジスタのゲート電極と、トランジスタ間に金属層を埋め込んでなり、各ゲート電極9,10の端部がゲート絶縁膜8を介して金属層の端面に重なるように配置された埋め込み金属層7と、各ゲート電極の他端部側に形成されたLDD領域16,17とを備える。

(もっと読む)

互いに重ねて堆積させた金属層の積層体中に形成されたゲート電極を含むMOSトランジスタを備える半導体デバイスの製造方法

互いに重ねて堆積させたいくつかの金属層(8,9,13;8,12,13)として形成したゲート電極(15,16)を有するMOSトランジスタを備える半導体デバイスの製造方法。この方法では、シリコン本体(1)に、ゲート誘電体層(7)を備えるシリコン活性領域(4,5)およびこれらの領域を互いに絶縁するフィールド分離領域(6)を形成する。次いで、第1の金属層(8)を堆積させ、活性領域(4)の一部の位置でその層中に局所的に窒素を導入する。次いで、第1の金属層上に第2の金属層(13)を堆積させ、その後それらの金属層中にゲート電極をエッチングする。第1の金属層中に窒素を導入する前に、第1の金属層上に窒素透過性の第3の金属補助層(9)を堆積させる。したがって、その下にあるゲート電極に損傷を与える危険なく、第1の金属層を窒化することができる。金属の仕事関数を実質的に変えることが可能であるとともに、NMOSおよびPMOSを備える半導体デバイスが実現される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 N型ポリメタルゲート電極とP型ポリメタルゲート電極の界面抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板101上にシリコン膜を形成する工程と、シリコン膜の領域PにP型不純物を、領域NにN型不純物をこの順にイオン注入する工程と、シリコン膜上にシリサイド膜106及び金属膜をこの順で形成する工程と、シリコン膜、シリサイド膜106及び金属膜をパターニングして領域PにP型ポリメタルゲート電極を、領域NにN型ポリメタルゲート電極を形成する工程とを備え、P型不純物のイオン注入後、N型不純物のイオン注入前に第1の熱処理を行ってP型不純物を活性化させ領域Pのシリコン膜をポリシリコン膜103Pとし、N型不純物のイオン注入後、第2の熱処理を行い、N型不純物を活性化させ領域Nのシリコン膜をポリシリコン膜103nにすると共にシリサイド膜106に含まれたガスを除去する。

(もっと読む)

半導体装置及びその製造方法

半導体基板(101)上にゲート絶縁膜(102)を介して形成されたゲート電極(103)に不純物を導入し、ゲート電極(103)に対してレーザ光照射を行って、導入した不純物をゲート電極(103)のゲート絶縁膜(102)との界面まで拡散させるようにして、ゲート電極(103)の空乏化を抑制する。  (もっと読む)

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

絶縁ゲート電界効果トランジスタ

【課題】ゲート長が微細化された場合でも、ショートチャネル効果によるしきい値電圧のロールオフの抑制と、ゲートコーナー部におけるチャネルの高抵抗化の抑制とを両立させる。

【解決手段】ゲート絶縁膜17を介してゲート電極19と対向し、内部にチャネル層が形成される半導体基板のチャネル形成領域と、当該チャネル形成領域と逆の導電型を有し、チャネル形成領域に各々接し互いに離れて形成されているソース・ドレイン領域10と、を有する。チャネル形成領域とゲート絶縁膜17との界面を深さの基準面としたときに、ソース領域(ソース・ドレイン領域10)とチャネル層との接続箇所に最も近いソース領域の基板深部側の端部Aにおいて、ソース領域とチャネル形成領域との間に形成されている空乏層とソース領域内の空間電荷の中性領域とが成す界面が、基準面からチャネル層の最大深さの2倍までの深さ範囲内に位置する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】0.15μm世代以下のMISFETの高速動作を実現することのできる技術を提供する。

【解決手段】ゲート電極10nおよびサイドウォールスペーサ15をマスクとして、基板1の法線方向からn型不純物をイオン注入し、ソース、ドレイン拡散領域11bを形成した後、基板1の法線方向に対して所定の角度を有する斜め打ち込みでn型不純物をイオン注入し、基板1の表面から深さ20〜40nm程度の位置にソース、ドレイン拡張領域11aよりも相対的に不純物濃度の高いn型半導体領域16を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ホウ素及びリンを含むシリコン層を最下層に有するゲート電極の端部の尖りが抑制された半導体装置及びその製造方法を提供する。これによってゲート電流の増加を抑制し、CMOSデバイスのNBTI劣化を抑制する。

【解決手段】 半導体装置10は、シリコン基板11と、シリコン基板11上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成され、ホウ素及びリンを含むポリシリコン層18bを最下層に有するゲート電極17とを備える。ポリシリコン層18b中のホウ素の最大濃度と最小濃度との比が100以下である。

(もっと読む)

半導体装置とその製造方法

【課題】 酸素イオン注入工程とアニール工程を半導体装置の製造方法に応用し

、半導体装置のコストパフォーマンスを著しく向上させた半導体装置とその製造

方法の提供。

【解決手段】 ゲート酸化膜厚の異なる複数のMOSFETおよび素子分離領域を酸素

インプラを用いた新しい製造方法で構築し、パフォーマンスに優れた半導体集積

回路装置を構成する。

(もっと読む)

深く炭素がドーピングされた領域並びに隆起したドナーがドーピングされたソース及びドレインを特徴とする歪みnMOSトランジスタ

本発明に係る複数の実施例は、炭素がドーピングされた領域、及び隆起したソース/ドレイン領域を有することで、nMOSトランジスタチャネル中に引っ張り応力を供する。

(もっと読む)

(もっと読む)

応力蓄積絶縁膜の製造方法及び半導体装置

【課題】 応力蓄積絶縁膜の製造方法及び半導体装置に関し、高圧縮応力蓄積絶縁膜の剥がれに対する耐性を高める。

【解決手段】 少なくともSiを主成分とする半導体基板1上にSiソースガスとして、Si原子1個当たりのSi−H結合の数が1以下のアルキルシラン、アルコキシシラン、或いはアルキルシロキサンのいずれかを用いて、圧縮応力5が1GPa以上になるSiソースガス分圧及び印加電力の条件下で応力蓄積絶縁膜4を成膜する。

(もっと読む)

半導体素子およびその製造方法

【課題】素子の微細化が可能でスイッチング性能の高い立体構造を有する電界効果型トランジスタである半導体素子を提供する。

【解決手段】ソース領域と、前記ソース領域の上部に配置された半導体機能層と及び、前記半導体機能層の上部に配置されたドレイン領域とを備え、前記半導体機能層は、前記ソース領域に対してほぼ垂直に配列した、複数の柱状あるいは円筒状の半導体物質からなる第1の部材と、前記第1の部材を取り囲み、前記ソース領域と絶縁体を介して配置された第2の部材から構成され、前記第2の部材はゲート領域と、絶縁体領域とから構成されており、前記第1の部材の平均直径が1nm以上30nm以下であり、前記第1の部材の平均間隔が3nm以上50nm以下であり、前記半導体層の酸素を除く主成分がシリコン、またはゲルマニウム、またはシリコンとゲルマニウムの混合物のいずれかである半導体素子を用いる。

(もっと読む)

半導体装置の製造方法および半導体製造装置

シリコンウエハ101上のゲート酸化膜102上に、ポリシリコンを成膜して、ポリシリコン電極層103(第一電極層)を形成する。このポリシリコン電極層103上に、タングステン層105(第二電極層)を形成する。なお、タングステン層105を形成する前に、予め導電性のバリア層104をポリシリコン電極層103の上に形成しておく。その後、窒化シリコン層106をエッチングマスクとして、エッチング処理を行う。そして、剥き出しとなったポリシリコン層103の露出面に、プラズマ酸化処理により、酸化絶縁膜107を形成する。これにより、タングステン層105を酸化させずに、ポリシリコン電極層103に対して選択的な酸化処理を行うことができる。  (もっと読む)

(もっと読む)

141 - 160 / 183

[ Back to top ]