Fターム[5F140BG33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248)

Fターム[5F140BG33]の下位に属するFターム

シリサイド化 (1,065)

Fターム[5F140BG33]に分類される特許

41 - 60 / 183

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

成膜装置及び成膜方法

【課題】 ドーパントの活性化率の高いシリコンゲルマニウム膜を成膜するにあたり、シリコンゲルマニウム膜のマイグレーションを抑えること。

【解決手段】 反応容器内に処理ガスを供給すると共に処理雰囲気の温度を所定の温度に設定して基板上にシリコンゲルマニウム膜を成膜する工程(P4)と、次いで反応容器内に水素ガスを供給してシリコンゲルマニウム膜をアニールする工程(P5)と、その後、反応容器内を真空排気し続いてパージガスによりパージする工程を1回行うかまたは複数回繰り返す工程(P6)と、しかる後に基板を反応容器内から搬出する工程(P7)と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度の向上を実現し得る半導体装置及びその製造方法を提供する。

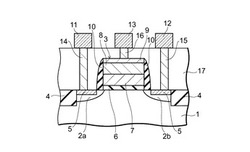

【解決手段】半導体基板10に形成されたチャネル領域44上にゲート絶縁膜18を介して形成されたゲート電極20bと、ゲート電極の側壁部分に形成されたサイドウォール絶縁膜26と、ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層38と、ソース/ドレイン拡散層に埋め込まれ、半導体基板と格子定数が異なる半導体層52とを有し、半導体層は、半導体基板のうちのサイドウォール絶縁膜の下方領域に食い込むように形成された第1の突出部54と、半導体基板のうちのサイドウォール絶縁膜の直下の部分に食い込むように形成された第2の突出部56とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成する際に、ゲート絶縁膜に金属原子が注入されることを抑制し、ゲートリーク電流の増加や閾値電圧の不安定化等を防止する。

【解決手段】MOSトランジスタを備える半導体装置の製造方法である。半導体基板11上にゲート絶縁膜12を形成する。ゲート絶縁膜12上に金属原子を複数個含むクラスタのイオン13を堆積させ、ゲート電極14の少なくとも最下層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ゲート酸化膜のフラットバンド電圧のマイナス側へのシフトを抑制した半導体装置の製造方法を提供する。

【解決手段】第1導電型のシリコンカーバイド基板20を準備する工程と、シリコンカーバイド基板に、成膜温度を第1温度として水蒸気及び酸素を含有する雰囲気下で成膜して第1酸化膜32を形成する工程と、第1酸化膜上に、乾燥酸素を含有する雰囲気下で第1温度よりも低温である第2温度で熱処理を行って第2酸化膜34を形成して、第1酸化膜及び第2酸化膜により構成されるゲート酸化膜30を完成させる工程と、ゲート酸化膜上に、ポリシリコンのゲート電極40を形成する工程とを具える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Hf−O系絶縁膜上に、TaCx膜を用いたメタルゲート電極を備えたMISトランジスタの実効仕事関数を制御する。

【解決手段】SOI基板1のシリコン層1c側よりゲート絶縁膜2を形成する。次いで、ゲート絶縁膜2上に室温スパッタ法によってTaCx膜を堆積し、このTaCx膜から構成されるメタルゲート電極3を形成する。次いで、メタルゲート電極3上にアモルファス状態のシリコン膜を形成した後、メタルゲート電極3に熱処理を施す。次いで、前記シリコン膜を除去した後、メタルゲート電極3に酸素を添加する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜にHfを含むMOSトランジスタの特性のばらつきを抑制するために、Hf密度の面内ばらつきを少なくすることが必要である。

【解決手段】 半導体基板上に、熱酸化により酸化シリコンまたは酸窒化シリコンを含む絶縁膜(40)を形成する。絶縁膜の上にHfを含むガス(45)を供給して、絶縁膜の上にHf原子(41)を堆積させる。Hf原子が堆積している絶縁膜を、酸素雰囲気中(46)で熱処理する。酸素雰囲気中で熱処理した後、絶縁膜の上に、ゲート電極(50P,50N)を形成する。ゲート電極の両側に、ソース領域及びドレイン領域(52P,52N)を形成する。

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

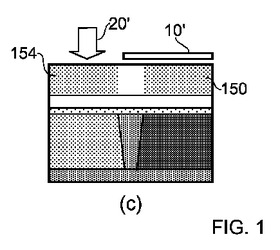

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板上方に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜とシリコンを含むゲート電極との間に、炭素を含むキャップ層を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

半導体材料及び金属材料を含む化合物のゲルマニウム酸化物層を介した基板内における選択的形成

【課題】基板がシリコン基板の場合に全体的にシリサイド化されるゲート(即ち、金属シリサイドから形成されるゲート)を得ることが可能な技術を提供する。

【解決手段】金属材料及び半導体材料からなる化合物から形成される領域16が、基板の表面の所定の部分にわたって3nm乃至5nmの厚さを有するゲルマニウム酸化物層を予め形成するとともに、表面1aの残りの部分にシリコン酸化物層12を予め形成することによって、半導体材料から形成される基板1に選択的に製作される。酸化物層上には金属層14が堆積される。金属材料は、その酸化物がゲルマニウム酸化物よりも熱力学的に安定し且つシリコン酸化物よりも熱力学的に安定しないように選択される。その後、熱アニーリングが行われることにより、前記金属材料によるゲルマニウム酸化物の還元が得られた後、基板1の表面1aの前記部分の高さで化合物が形成される。その後、金属層14が除去される。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

半導体装置の製造方法

【課題】 ソース/ドレイン領域にシリコン層を成長する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上にゲート絶縁層,ポリシリコン層の積層を形成する工程と、前記ポリシリコン層の表面に第1の加速エネルギでp型不純物を高濃度にドープする工程と、前記ポリシリコン層,ゲート絶縁層をパターニングし,ゲート電極を形成すると共に,その両側に基板シリコン表面を露出する工程と,前記露出した基板シリコン表面に前記第1の加速エネルギより高い第2の加速エネルギでp型不純物を深くイオン注入する工程と、シリコン層を、前記ポリシリコン層表面上には成長させず、前記基板シリコン表面上にのみ成長する工程と、

を有する。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

半導体装置とその製造方法

【課題】微細MOSFETのゲート絶縁膜に高誘電率膜を用いた場合でも、使い易いゲート閾値電圧をもった半導体装置(特に、PチャネルMOSFET)とその製造方法を実現する。

【解決手段】ゲート電極/アルミニウムを含みシリコン酸化膜より大きな比誘電率をもった高誘電率絶縁膜/シリコン酸化膜/シリコン基板とし、熱処理によってシリコン酸化膜、あるいはシリコン酸化膜とシリコン基板との界面にアルミニウム原子あるいはアルミニウムイオンを拡散させた拡散層を設ける。高誘電率絶縁膜としては、比率が2:8から8:2の酸化ハフニウムと酸化アルミニウムの積層膜あるいは混合膜とし、熱処理は、500から1000℃で、1から100秒程度の熱処理とする。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

41 - 60 / 183

[ Back to top ]