Fターム[5F140BG33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248)

Fターム[5F140BG33]の下位に属するFターム

シリサイド化 (1,065)

Fターム[5F140BG33]に分類される特許

61 - 80 / 183

半導体装置の製造方法及び半導体装置

【課題】不純物を混ぜなくても立方晶(cubic)、正方晶(tetragonal)又は斜方晶(orthorhombic)のハフニウム酸化物を形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1上にHfO2膜3を形成する工程と、HfO2膜3上にゲート電極膜5を形成する工程と、HfO2膜3及びゲート電極膜5が形成されたシリコン基板1に熱処理を施して、HfO2膜3を結晶化する工程と、を含む。熱処理温度は例えば800℃である。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、表面にバッファ層が形成された基板と、エピタキシャル成長によってバッファ層上に形成された、所定の導電型を有する電界緩和層と、電界緩和層上の一部領域に形成された、所定の導電型とは反対の導電型を有する半導体層と、半導体層の中または表面に形成された、所定の導電型と同一の導電型を有するコンタクト層と、コンタクト層上に形成されたソース電極と、電界緩和層上に形成されたドレイン電極と、半導体層上に該半導体層の端面と重畳するように形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体層の端面と重畳するように形成されたゲート電極と、を備え、半導体層の端面近傍に形成されるチャネルと電界緩和層とが電気的に接続する。

(もっと読む)

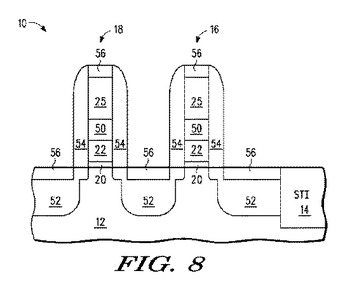

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】本発明はフィントランジスタを含む半導体素子及びその製造方法に関する。

【解決手段】半導体素子は、素子分離構造を備えた半導体基板に画成されたフィン型活性領域と、フィン型活性領域の上部に形成されたリセスと、フィン型活性領域の上部に形成され、前記リセスを埋め込むシリコンゲルマニウム層を含むゲート電極とを含む。

(もっと読む)

絶縁ゲート型半導体装置及びその製造方法

【課題】 絶縁ゲート型半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板1と、半導体基板1上に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜2と、ゲート絶縁膜2上に形成された1原子層乃至2原子層の厚さの多結晶Ge層或いは多結晶Si1-x Gex (x>0.5)層からなるキャップ層3と、キャップ層3上に形成された多結晶シリコンを含むゲート電極4とを有する。

(もっと読む)

半導体素子の製造方法

【課題】導電膜と金属膜の積層構造のゲート電極膜を形成する時、界面の粗度を均一にすることにより、比抵抗を減少させる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上にゲート絶縁膜102、導電膜104及び金属膜106を形成する段階、導電膜及び金属膜の界面105にイオン注入領域を形成するためにイオン注入工程を行う段階、イオン注入された半導体基板にフラッシュ熱処理工程を行う段階及び金属膜、導電膜及びゲート絶縁膜をパターニングする段階を含む半導体素子の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】高速かつ低消費電力、高記憶密度な半導体装置の製造方法を提供する。

【解決手段】半導体基板中のp型およびn型ウェル上にLa、Al、Oからなる第1および第2非晶質絶縁膜をそれぞれ形成し、第1、第2非晶質絶縁膜上に、その酸化物標準生成エンタルピーの絶対値が第2非晶質絶縁膜の酸化物標準生成エンタルピーの絶対値よりも小さい第1ゲート電極を形成し、その後形成された構造体全体を酸素雰囲気で熱処理し、その後、第1ゲート電極上に金属膜を形成し、第1ゲート電極と金属膜を固相反応させ、第2ゲート電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコンから構成される導電パターンの下から上までの幅を均一化すること。

【解決手段】半導体基板1上に絶縁膜5を介して第1シリコン膜6を形成し、第1シリコン膜6に高濃度で一導電型不純物を導入し、第1シリコン膜6上に第2シリコン膜9を形成し、第2シリコン膜9上に所定パターンのマスク10mを形成した後、マスク10mから露出する領域で、第1シリコン膜6が露出しない深さまで第1条件により第2シリコン膜9をエッチングし、ついで第1条件に比べて半導体基板1の垂直方向へのエッチング成分の高い第2条件によって第2シリコン膜9の残りと第1シリコン膜6を絶縁膜5が露出しない深さまでエッチングし、さらに第2条件に比べて絶縁膜に対する第1シリコン膜6のエッチング選択比が大きな第3条件により第1シリコン膜6の残りをエッチングする工程とを有している。

(もっと読む)

半導体装置

【課題】トランジスタのサイズによらない普遍的な引っ張り歪みをnチャネル型MOSトランジスタに印加できる半導体装置を提供する。

【解決手段】nチャネル型MOSトランジスタのゲート絶縁膜として、高誘電率絶縁膜を使用し、この高誘電率絶縁膜を半導体基板上に界面層を介さず直接形成することにより、チャネル領域に引張り歪を与える。チャネル領域に圧縮歪を有するpチャネル型MOSトランジスタと組み合わせることにより、相補型の高性能半導体装置を構成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置およびその製造方法は高誘電体をゲート絶縁膜として有し、かつ、適正な閾値電圧を有する。

【解決手段】半導体装置は、半導体基板101と、半導体基板上に設けられ、シリコン酸化膜よりも比誘電率の高い高誘電体から成るゲート絶縁膜108,109と、ゲート絶縁膜上に設けられたアルミニウム層を含むN型FET用の第1のゲート電極110aと、ゲート絶縁膜上に設けられ、NiXSiY(X>Y)から成るP型FET用の第2のゲート電極110bとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を少ない工程数で形成することができる、半導体装置の製造方法を提供する。

【解決手段】基板上に、ゲート絶縁膜を介してシリコン層を形成する工程と、第1のゲート電極および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極を覆う層間膜を形成する工程と、前記第1および第2のゲート電極の前記シリコン層上に被シリサイド化金属からなる第1の金属膜を形成する工程と、前記第1の金属膜を構成する前記被シリサイド化金属のシリサイドである第1のシリサイドが形成されるように熱処理を行う第1の熱処理工程と、前記第1のゲート電極の前記第1の熱処理の行われたシリコン層上に、選択的に酸化膜を形成する工程と、前記第1の熱処理が行われたシリコン層上に、被シリサイド化金属からなる第2の金属膜を形成して、さらに熱処理する第2の熱処理工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

電界効果型半導体装置及びその製造方法

【課題】 電界効果型半導体装置及びその製造方法に関し、ゲート絶縁膜にダメージを与えることなく、少なくとも窒素を含有するとともにシリコンを主成分とする膜を組成制御性良く構成する。

【解決手段】 シリコンと、シリコンに対して5〜30原子数%の窒素を含有する導電膜をゲート電極3の少なくとも一部として用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極上に積層するポリサイド層、バリアメタル層、メタル層、絶縁膜ハードマスクの膜剥がれを抑制する効果を発揮させた半導体装置およびその製造方法を提供することを目的とする。

【解決手段】トレンチゲート型のMOSトランジスタTr1、Tr2を備えた半導体装置の製造方法であって、半導体基板1の表面にトレンチ12、13を形成してからゲート絶縁膜20を形成する工程と、前記半導体基板1上にゲート電極8用のポリシリコン層を形成する工程と、前記トレンチ12、13上に位置する前記ポリシリコン層の上面に生じた凹部を除くための水素雰囲気中アニールを行なう工程と、前記ポリシリコン層を選択的に除去することによりトレンチ12、13上のポリシリコン層を残してこれをゲート電極8とする工程とを具備してなることを特徴とする半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】研磨工程などを削減するとともに素子分離領域の上に微細なゲートスペースパターンを有する。

【解決手段】半導体装置は、半導体基板100と、素子分離絶縁膜101と、第1および第2電極107a,107bと、ゲート絶縁膜パターン104と、側壁絶縁膜108とを備えている。素子分離絶縁膜101は半導体基板100の上に設けられており、第1および第2電極107a,107bはゲート絶縁膜パターン104を挟むようにして素子分離絶縁膜101の上に設けられている。側壁絶縁膜108は、第1および第2電極107a,107bの側面のうちゲート絶縁膜パターン104に接している部分以外の部分に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易なNi−FUSI/SiONあるいはHigh−kゲート絶縁膜構造および低いしきい値電圧Vthを有するCMISを備えた半導体装置およびその製造方法を提供することを可能にする。

【解決手段】基板1中に互いに絶縁分離されたp型半導体領域2とn型半導体領域3を形成する工程と、p型およびn型半導体領域上に第1および第2ゲート絶縁膜5,15をそれぞれ形成する工程と、第1ゲート絶縁膜上にNi/Si<31/12となる組成の第1ニッケルシリサイド6bを形成するとともに第2ゲート絶縁膜上にNi/Si≧31/12となる組成の第2ニッケルシリサイド16を形成する工程と、第1ニッケルシリサイド中にアルミニウムを拡散させ、第1ニッケルシリサイドと第1ゲート絶縁膜との界面にアルミニウム6aを偏析させる工程と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層への不純物拡散を抑制し、シリコン層中に不純物を十分行き渡ることのできる半導体装置、及びその製造方法を提供する。

【解決手段】半導体基板上に、ゲート酸化膜を介して形成されたゲート電極を備える半導体装置において、前記ゲート電極は、前記ゲート酸化膜に接して形成されたシリコン層と、前記シリコン層上に積層された金属を含有する金属含有層と、を有し、前記シリコン層は、前記ゲート酸化膜側に設けられ、第1導電型の不純物がドープされている第1シリコン層と、前記第1シリコン層上に積層され、前記第1導電型の不純物がドープされていない第2シリコン層と、を有すること。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】混晶層中のGe濃度およびC濃度の許容範囲内で、チャネル領域に十分に応力を印加することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】Si基板1上にダミーゲート電極3を形成する。次に、ダミーゲート電極3をマスクにしたリセスエッチングにより、リセス領域7を形成する。次いで、リセス領域7の表面に、SiGe層からなる混晶層8をエピタキシャル成長させる。続いて、ダミーゲート電極3を覆う状態で、混晶層8上に、層間絶縁膜12を形成し、ダミーゲート電極3の表面が露出するまで、層間絶縁膜12を除去する。ダミーゲート電極3を除去することで、層間絶縁膜12にSi基板1を露出する凹部13を形成する。その後、凹部13内にゲート絶縁膜14を介してゲート電極15を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

ゲート構造を有する半導体素子及びその製造方法

【課題】ゲートコンタクト抵抗値及びシート抵抗値を同時に低くし得る中間構造物を有するゲート構造及びゲート構造を有する半導体素子、並びにそれらの製造方法を提供すること。

【解決手段】本発明の半導体素子は、上面及び下面を有する基板21と、基板21の上面近くに形成され、ゲート絶縁膜22、ゲート絶縁膜22上に形成された第1電極23、第1電極23上に形成された中間構造物24、及び中間構造物24上に形成された第2電極25を含むゲート構造とを備え、中間構造物24が、チタン(Ti)を含む第1Ti膜101と、タングステン及びシリコンを含み、第1Ti膜上に形成された第2W膜24Dとを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

61 - 80 / 183

[ Back to top ]