Fターム[5F140BG33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248)

Fターム[5F140BG33]の下位に属するFターム

シリサイド化 (1,065)

Fターム[5F140BG33]に分類される特許

161 - 180 / 183

半導体装置の製造方法

【課題】 トランジスタのソースおよびドレイン層上に形成されたシリサイド膜がソースおよびドレイン層の接合部を突き抜けることを抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコンを有する半導体基板10の主面上に半導体領域Sと絶縁体領域Iとを形成し、半導体領域および絶縁体領域上にシリコンを主成分とする半導体膜90を堆積し、シリコンと反応することによってシリサイド膜を形成する金属膜100を半導体膜上に堆積し、半導体基板を熱処理することによって半導体領域では金属膜と半導体膜および該半導体膜の下の半導体領域のシリコンとを反応させて第1のシリサイド膜110を形成し、絶縁体領域では金属膜と半導体膜のシリコンとを反応させて第2のシリサイド膜120を形成し、第1のシリサイド膜および第2のシリサイド膜におけるシリコンと金属との組成の相違に基づいて、第2のシリサイド膜を選択的に除去する。

(もっと読む)

半導体装置、その製造方法、および情報処理装置

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1910は、素子分離領域101と活性領域102とを有する半導体基板100と、活性領域102上にゲート絶縁膜103を介して設けられ、側壁の少なくとも一部がゲート電極側壁絶縁膜105で覆われたゲート電極104と、ゲート電極104の両側にゲート電極側壁絶縁膜105を介してそれぞれ設けられたソース領域106およびドレイン領域106とを備えている。ソース領域106およびドレイン領域106の少なくとも一方は、コンタクト配線と接触するための第2の面を有し、第2の面は、第1の面AA’に対して傾いており、第2の面は、素子分離領域の表面と80度以下の角度で交差する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板4上にシリコン酸化膜5を介して例えばゲ−ト電極2を形成するに際し、このゲ−ト電極2を複数の多結晶シリコン層6の積層体で構成する。ゲ−ト電極2の部分は、非晶質層の堆積工程とこの非晶質材料の結晶化(再結晶化)工程とを有する薄膜の製造方法により形成する。この際、1回に成膜する非晶質層の厚さが不良事象に応じて決定される臨界応力値によって規定される厚み以下であるように非晶質層の堆積を複数回に分割して行い、各非晶質層の堆積工程後毎に非晶質材料を結晶化させ、かつ非晶質層堆積工程と非晶質材料結晶化工程を繰り返すことにより必要な膜厚の多結晶層6の積層構造体を得る。

【解決手段】 半導体装置の電気特性の劣化と、層間剥離,層内での割れ等の不良を防止し、かつ多結晶材料層の積層により、所望厚さで小粒径の多結晶層が得られる。

(もっと読む)

ドープされたチタン酸ボディを有するMOS(Metal−Oxide−Semiconductor)デバイス

単結晶のチタン酸ストロンチウム又はチタン酸バリウム(10)のボディを有するMOS(Metal-Oxide-Semiconductor)デバイスが提供され、ボディは、絶縁領域に隣接するドープされた半導体領域(24)を備えている。ボディは、絶縁領域により、半導体領域から分離した、ドープされた導通領域を、さらに備えていてもよい。様々な手法でドープされた場合の単結晶チタン酸ストロンチウムの材料特性は、MOSスタックの絶縁構成部、導通構成部、及び、半導体構成部を提供するために、用いられる。有利なことに、単一のボディを用いることにより、スタック構成部の間のインターフェースレイヤの存在を回避することができ、電界効果トランジスタなどのMOSデバイスの特性を改善する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 多結晶Si膜と高誘電率絶縁膜との界面特性を簡単な手段を適用することで改善し、高誘電率ゲート絶縁膜を用いたMOS−FETに於ける閾値電圧Vthがシフトする問題を解消しようとする。

【解決手段】 SiO2 に比較して高い誘電率の材料、例えばHfO2 からなるゲート絶縁膜3GをもつMOS−FETを製造する工程に於いて、ゲート電極用の多結晶Si膜3を成膜後のゲート加工前の状態で高誘電率絶縁膜2と多結晶Si膜3との界面特性を改善する為に酸化雰囲気中で熱処理を行う工程が含まれてなることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】 基板バイアス電圧を印加することなく、正確且つ確実な低温動作を実現する構成を有する電界効果トランジスタを提供する。

【解決手段】 本発明の実施の一形態に係る電界効果トランジスタは、300K以下の温度条件で動作することが想定された電界効果トランジスタであって、4.05未満の仕事関数WFnを有するゲート電極材により形成されたゲート電極を備えているnチャネル電界効果トランジスタを含むものである。また、本発明の実施の一形態に係る電界効果トランジスタは、5.17を超える仕事関数WFpを有するゲート電極材により形成されたゲート電極を備えているpチャネル電界効果トランジスタを含み得るものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、高誘電体材料膜を選択的に容易にエッチングできるようにすること。

【解決手段】シリコン基板104の上に、少なくとも高誘電体材料膜106を含む絶縁膜106,111を形成し、絶縁膜106,111上にゲート電極層109を形成し、ゲート電極層109をパターニングしてゲート電極109を形成し、ゲート電極109以外の高誘電体材料膜106を、フッ素化合物を含む強酸水溶液で除去する半導体装置の製造方法。

(もっと読む)

分離ウェルを用いるMOSバラクタ

【課題】 向上した調節能力と高い品質係数Qとを有するバラクタ及びその製造方法を提供すること。

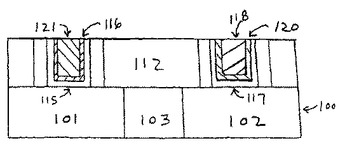

【解決手段】 本発明は、向上した調節能力と高い品質係数Qとを有するバラクタ22、及び、バラクタ22を製造する方法を提供する。本発明の方法は、従来のCMOS処理スキーム又はBiCMOS処理スキームに組み込むことができる。この方法は、第1の導電型の半導体基板12と、該基板12の上部領域11の下方に配置された、第2の導電型のサブコレクタ14又は分離ウェル(すなわち、ドープ領域)とを含む構造体であって、該第1の導電型は、第2の導電型とは異なる構造体を準備するステップを含む。次に、複数の分離領域16が、基板12の上部領域11内に形成され、次いで、ウェル領域が、基板12の上部領域11内に形成される。場合によっては、本発明のプロセスのこの時点で、ドープ領域14が形成される。ウェル領域は、第2の導電型の外側ウェル領域20A及び20Cと、第1の導電型の内側ウェル領域20Bとを含む。ウェル領域の各々のウェルは、分離領域16によって上面で分離される。次に、内側ウェル領域20Bの上方に、少なくとも第1の導電型のゲート導体26を有する電界効果トランジスタが形成される。

(もっと読む)

ボイドのないゲート電極を具備したトランジスタの製造方法

【課題】 ボイドのないゲート電極を具備したトランジスタの製造方法を提供する。

【解決手段】 半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜の上部にゲート電極用ポリシリコン膜を蒸着する。次いで、前記ポリシリコン膜にp型不純物をイオン注入し、前記ポリシリコン膜の所定厚さほどを化学機械的研磨方法で除去する。

(もっと読む)

半導体装置

【課題】 低抵抗でゲート空乏化が起こらず、高温において安定であるとともに、仕事関数が制御されたゲート電極を有するCMISデバイスを提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するp型MISトランジスタと、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するn型MISトランジスタとを具備するCMISデバイスである。前記p型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に第1の金属を有し、前記n型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に、前記第1の金属のホウ化物を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

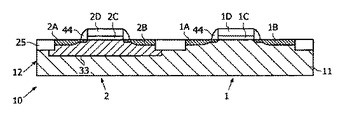

本発明は、それぞれ金属及びさらなる元素の両方を含む化合物の第1及び第2の導電材料を有するゲート領域(1D,2D)を持つNMOST1及びPMOST2を備えるCMOS装置(10)に関する。本発明によれば第1及び第2の導電材料は共に前記金属としてモリブデンとタングステンとを含む群から選択される金属を含む化合物を有し、前記第1の導電材料は前記さらなる元素として酸素を有し、前記第2の導電材料は前記さらなる元素としてカルコゲナイドを有する。本発明はこのような装置の魅力的な製造方法を提供する。  (もっと読む)

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

ゲート誘電体と、アルミナイドを含む金属ゲート電極とを有する半導体デバイスについて示した。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 電気的特性に優れた半導体装置を提供する。また、低温でゲートリーク電流量を小さくすることのできる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1の上には、第1の絶縁膜5と、窒素を含む第2の絶縁膜6とからなるゲート絶縁膜が形成されている。また、ゲート絶縁膜の上にはゲート電極8が形成されている。そして、ゲート絶縁膜およびゲート電極8の側壁部には、第2の絶縁膜6に含まれる窒素濃度よりも高濃度の窒素を含むシリコン酸窒化膜11が形成されており、第2の絶縁膜6とシリコン酸窒化膜11が接触するゲート電極8の下端部付近での窒素濃度は周囲の窒素濃度よりも高くなっている。第2の絶縁膜6は5atm%〜20atm%の濃度の窒素を含むことが好ましく、シリコン酸窒化膜11は、第2の絶縁膜6に含まれる窒素濃度の1.1倍〜2.0倍の窒素を含むことが好ましい。

(もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極材料膜形成時に形成されたゲート電極材料膜/高誘電率ゲート絶縁膜の界面における寄生低誘電率界面層を還元し、ゲート絶縁膜の薄膜化を実現する。

【解決手段】 シリコン基板1上に下部界面層4としてのシリコン酸窒化膜4を形成し、その上に高誘電率ゲート電極5としてのHfアルミネート膜を形成する。Hfアルミネート膜5上にゲート電極材料膜7としてのポリシリコン膜をLPCVD法により570℃以上の温度で形成する。その後、ゲートドーパント9を注入する前に、950℃以上1050℃未満の温度で熱処理(PGA処理)8を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 メタルゲート及びhigh-kゲート絶縁膜を有するCMOSにおいて、nMOS及びpMOSトランジスタの低しきい値化を実現する。

【解決手段】 n型MISFET形成領域11のゲート絶縁膜3aはHfO2膜であり、メタルゲート電極4aは、TiN膜と、ゲート絶縁膜との界面に生成されたにゲート電極に含まれるIV族遷移金属と酸素を含むがシリコンは含まない界面層とからなり、その仕事関数はn型MISFETのゲート電極材料に適した4.0〜4.2eVである。p型MISFET形成領域12のゲート絶縁膜3bはHfSiO2/HfO2であり、メタルゲート電極4bはTiNと、ゲート絶縁膜との界面に形成されたにゲート電極に含まれるIV族遷移金属と酸素および金属的シリコン(Si0)からなる界面層とからなり、その仕事関数は、p型MISFETのゲート電極材料に適した4.9eVとなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を有する半導体装置の閾値電圧を高精度に制御する。

【解決手段】 シリコン基板1上層にp型ウェル3を形成する。p型ウェル3の極表層に砒素イオン4を注入し、熱処理を行うことによりp型低濃度層5を形成する。基板1上にHfAlOx膜7とポリシリコン膜8を積層する。ポリシリコン膜8をパターニングしてゲート電極8aを形成する。ゲート電極8aをマスクとして砒素イオン10を注入してn型エクステンション領域10aを形成した後、ゲート電極8a側壁にサイドウォール13を形成する。サイドウォール13及びゲート電極8aをマスクとして砒素イオン14を注入してn型ソース/ドレイン領域15aを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

161 - 180 / 183

[ Back to top ]