Fターム[5F140BG36]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844)

Fターム[5F140BG36]の下位に属するFターム

Fターム[5F140BG36]に分類される特許

121 - 140 / 306

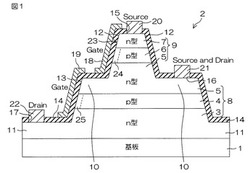

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

垂直チャネルトランジスタの製造方法及び半導体素子のピラー製造方法

【課題】エッチング工程を利用しなくとも、垂直チャネルとして作用するピラーを安定的に構築できる垂直チャネルトランジスタの製造方法を提供すること。

【解決手段】本発明の垂直チャネルトランジスタの製造方法は、基板上に犠牲膜22を形成するステップと、犠牲膜22にコンタクトホール23を形成するステップと、コンタクトホール23を埋め込み、犠牲膜22の表面上まで横方向に延長されたピラーを形成するステップと、犠牲膜22を除去するステップと、ピラーの露出した側壁と基板の露出した部分との上にゲート絶縁膜29を形成するステップと、少なくともピラーの露出した側壁上に形成されたゲート絶縁膜29の一部を取り囲むゲート電極30を形成するステップとを含むことを特徴とする。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

ストレッサ層を有するデュアル仕事関数デバイスおよびその製造方法

【課題】高誘電率ゲート誘電体を有するMOSFETトランジスタの製造方法の提供。

【解決手段】デュアル仕事関数半導体デバイスの製造方法であって、第1領域と第2領域とを有する基板を提供する工程と、第1領域と第2領域とを覆うようにゲート誘電体2を形成する工程と、該ゲート誘電体2を覆うように金属ゲート層3を形成する工程であって、歪を導入することにより変調可能な(堆積したままの)第1仕事関数を有する金属ゲート層3を形成する工程と、第1領域の上の金属ゲート層3の(堆積したままの)第1仕事関数に、第1の予め決められた仕事関数シフト(ΔWF1)を導入するように第1歪を選択し、第1領域の上の金属ゲート層3を覆うように第1歪導電層4を選択的に形成して、第1歪導電層が金属ゲート層に選択された第1歪を働かせる工程とを含む方法を提供する。この方法により得られるデュアル仕事関数半導体デバイスも記載される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】 金属ゲート電極への熱負荷を低減可能であるとともに、高誘電率ゲート絶縁膜に対する高温での熱処理が可能である半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に高誘電率ゲート絶縁膜及びダミーゲート電極を形成する工程と、少なくとも高誘電率ゲート絶縁膜及びダミーゲート電極をマスクとして半導体基板上にソース及びドレイン領域を形成する工程と、半導体基板上に層間絶縁膜を形成してその一部を除去することでダミーゲート電極上方を露出させる工程と、高誘電率ゲート絶縁膜上のダミーゲート電極を除去して溝を形成する工程と、溝の内部を被覆又は埋め込むように高誘電率ゲート絶縁膜上に金属ゲート電極を形成する工程と、を有する。

(もっと読む)

フィン型トランジスタ

【課題】フィン内部のチャネル部に垂直応力を与える事が可能なフィン型トランジスタを提供する。

【解決手段】基板と、前記基板上に形成される複数の半導体フィンと、前記半導体フィン内のチャネル領域を覆い金属または導電性を持つ化合物や、ポリシリコンで形成されるゲート電極と、前記ゲート電極の内部に含まれその両側に存在する前記半導体フィンに対し応力源となるよう格子定数の異なる材料や密度の異なるアモルファスシリコン、または線膨張係数の異なる材料で形成される埋め込み部材とを備える。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

MIS型FET及びその製造方法

【課題】動作時のゲート電極底端部において発生する電界集中を低減させた、製造歩留り及び信頼性の高いMIS型FET得る。

【解決手段】下地20上にエッチングレートの異なる二層構造のゲート絶縁膜を有し、ゲート絶縁膜に加工形成されたゲートコンタクトホールの底部側面及び底部が下地側に凸形状の曲面である。このゲート絶縁膜は、下地側から下層の第1ゲート絶縁膜30と第1ゲート絶縁膜のエッチングレートより大なるエッチングレートを有する上層の第2ゲート絶縁膜32から成る窒化シリコン膜である。

(もっと読む)

半導体装置およびその製造方法

【課題】高速高周波動作に適した信頼性の高い半導体装置を得ること。

【解決手段】シリコン基板11の表面層に拡張ドレイン領域12とウェル領域13を形成し、拡張ドレイン領域12上に絶縁層20を形成する。その絶縁層20の側壁に犠牲スペーサー領域を形成し、犠牲スペーサー領域をマスクとしてウェル領域13の表面層に自己整合的に窒素を注入し熱処理を行う。犠牲スペーサー領域を除去した後に熱酸化を行ってゲート酸化膜21,22を形成する。窒素が注入された部分のシリコンの酸化速度は、窒素が注入されていない部分のシリコンの酸化速度と同じか、それよりも低下する。窒素は、絶縁層20の側壁の犠牲スペーサー領域の下には注入されないので、厚い絶縁層20に接続する部分のゲート酸化膜21の厚さが、それ以外の部分のゲート酸化膜22の厚さと同じか、それよりも厚くなる。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル拡散層における不純物濃度プロファイルを急峻で且つ浅接合化することによって短チャネル効果を抑制すると共に、十分な活性化濃度を有する低抵抗なチャネル拡散層によって高駆動力を維持する微細デバイスを実現できるようにする。

【解決手段】MIS型トランジスタは、MIS型の半導体基板100の主面に形成されたゲート絶縁膜101と、該ゲート絶縁膜101の上に形成されたゲート電極102と、半導体基板100におけるゲート電極102の下方に形成されたP型のチャネル拡散層103とを有している。チャネル拡散層103は不純物として炭素を含んでいる。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ動作を実現することができるとともに、所望のゲート閾値電圧を実現することができる、窒化物半導体素子(HEMT)を提供すること。

【解決手段】このHEMTは、真性GaN層3およびn型AlGaN層4が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2は、ストライプ状の線状部10と、島状の合流部11とを備えている。複数本の線状部10は、隣接する線状部10との間に形成されたストライプ状のトレンチ6によって、互いに分離されている。線状部10においてトレンチ6内に露出した積層境界7には、ゲート絶縁膜12を介してゲート電極13が対向している。また、n型AlGaN層4には、ソース側合流部11Sおよびドレイン側合流部11Dにおいて、ソース電極14およびドレイン電極15がそれぞれ接触形成されている。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】チャネルが形成される部分における分極電荷の発生を抑えると共に、ブレークダウンの発生を抑制できる、窒化物半導体素子およびその製造方法を提供すること。

【解決手段】電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が積層された窒化物半導体積層構造部2を備えている。窒化物半導体積層構造部2には、ドレイントレンチ6が形成されることにより、メサ積層部8が形成されている。メサ積層部8の壁面9は、n型GaN層5の頂面5aとの境界付近に位置する上側端部11と、n型GaN層3の上面3aとの境界付近に位置する下側端部12と、上側端部11と下側端部12との間に位置する中央部10とを有している。より具体的には、壁面9は、全体として傾斜角度の異なる複数の平面形状の傾斜部分17〜27を有している。そして、この壁面9には、ゲート絶縁膜15を挟んで、ゲート電極16が対向配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート長を増加させずにゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11上の絶縁膜12に形成されたゲート形成溝13の内部にゲート絶縁膜16を介してゲート電極17が形成され、前記ゲート電極17の一方側の前記半導体基板11にソース領域14が形成され、他方側の前記半導体基板11にドレイン領域15が形成された半導体装置1において、前記ゲート電極17は、前記ゲート形成溝13内から前記絶縁膜12表面より突出して形成されたゲート電極本体部30と、前記ゲート電極本体部30の前記絶縁膜12表面より突出した部分の側壁に形成された導電性のサイドウォール18とを有することを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】 動作時のオン抵抗を充分に小さくすることが可能な高耐圧のFET及びその製造方法を提供することを目的とする。

【解決手段】 p型GaNチャネル層16がその上下をn型GaNソース層18及びn型GaNドレイン層14によって挟まれた積層構造をメサ形状に加工してその側面に傾斜面を形成し、この傾斜面におけるp型GaNチャネル層16の傾斜した側面上にSiO2 ゲート絶縁膜24を介してゲート電極40Ga、40Gbを設けている。即ち、p型GaNチャネル層16の傾斜した側面をチャネル領域としている。このため、そのチャネル長をp型GaNチャネル層16の厚さによって制御することが可能となり、容易かつ高精度に短チャネル長化を達成することができる。

(もっと読む)

121 - 140 / 306

[ Back to top ]