Fターム[5F140BG40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | ゲート電極の形状を形成する方法 (2,844) | 研磨、CMP (298)

Fターム[5F140BG40]に分類される特許

281 - 298 / 298

半導体装置及びその製造方法

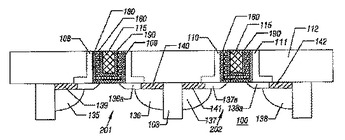

【課題】短チャネル効果を抑制できる構造であり、しきい値電圧を制御でき、電流駆動力に優れ、高速動作が可能なマルチフィンFETを有する半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置の1態様は、半導体基板上に設けられたソース領域及びドレイン領域と、前記ソース領域及びドレイン領域を接続する複数のフィンと、前記半導体基板の上方に設けられ、前記各フィンの一方の側面側に設けられた第1のゲート電極と、前記半導体基板の上方に設けられ、前記フィンに対して前記第1のゲート電極と対向して前記各フィンの他方の側面側に設けられ、前記第1のゲート電極と分離された第2のゲート電極と、前記各々の第1のゲート電極に接続する複数の第1のパッド電極と、前記複数の第1のパッド電極を接続する第1の配線と、前記各々の第2のゲート電極に接続する複数の第2のパッド電極と、前記複数の第2のパッド電極を接続する第2の配線とを具備する。

(もっと読む)

FETにおける埋め込みバイアス・ウェル

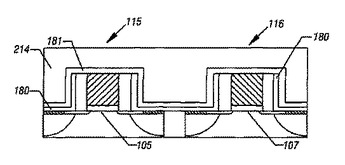

【課題】 リーク電流及び接合キャパシタンスを除去又は減少させるために、半導体デバイスにおける新規な構造体を提供する。

【解決手段】 半導体装置の構造体及び該構造体を製造するための方法が開示される。半導体構造体は、第1及び第2のソース/ドレイン領域、該第1及び第2のソース/ドレイン領域の間に配置されたチャネル領域、該チャネル領域と物理的に接する埋め込みウェル領域、該埋め込みウェル領域と該第1のソース/ドレイン領域との間に配置され、かつ、該埋め込みウェル領域と該第2のソース/ドレイン領域との間に配置される埋め込みバリア領域とを含み、該埋め込みバリア領域が、該埋め込みウェル領域と該第1のソース/ドレイン領域との間のリーク電流及びドーパント拡散、並びに該埋め込みウェル領域と該第2のソース/ドレイン領域との間のリーク電流及びドーパント拡散を防止する。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、安定した処理が可能で、且つゲートショートしない、ダマシンゲート構造を有する半導体装置の製造方法を提供することを目的としている。

【解決手段】 本発明は、エッチングストッパー膜に用いたシリコン窒化膜を触媒CVD(Catalytic−CVD)法により、基板温度250〜400℃、触媒体温度1600〜2000℃で成膜する。これによって、シリコン窒化膜中の水素・塩素などの不純物を低減し、HF系のウェットエッチレートを熱酸化膜の1/4以下に抑えることにより、ゲート溝上部に露出したエッチングストッパー膜表面のエッチング量を抑えることができる。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

半導体装置

【課題】 高誘電率ゲート絶縁膜やメタルゲート電極を採用する場合に、仕事関数の変動を抑えて閾値電圧の変動量を低く抑えることができるようにし、ゲートリーク電流の増大を抑えて、信頼性の低下を招かないようにする。

【解決手段】 半導体装置を、ゲート電極1がメタルゲート電極であるか、又は、ゲート絶縁膜4が高誘電率ゲート絶縁膜である場合に、ゲート電極1とゲート絶縁膜4との間に、ゲート電極1側から順に、シリコン酸化膜2、シリコン窒化膜3を備えるものとする。

(もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

ゲート誘電体と、アルミナイドを含む金属ゲート電極とを有する半導体デバイスについて示した。  (もっと読む)

(もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

半導体装置の製造方法

【課題】 ダマシンゲートトランジスタのゲート絶縁破壊を抑制し、デバイスの信頼性を確保することのできる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1の上に、犠牲ゲート絶縁膜104および犠牲ゲート電極105を形成した後、犠牲ゲート電極105の側面に第1の側壁膜106を形成する。次に、第1の側壁膜106を介して、犠牲ゲート電極105の側面に、第1の側壁膜106とエッチングレートの異なる第2の側壁膜110を形成する。ここで、第1の側壁膜106の膜厚は、犠牲ゲート絶縁膜104の膜厚より厚くなるようにする。これにより、第1の側壁膜106および犠牲ゲート絶縁膜104をウェットエッチングする際のプロセスマージンを大きくして、第2の側壁膜110のゲート電極側下部にスリットが入るのを防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に生じるリーク電流を抑制でき、高いトランジスタ特性を維持したまましきい値電圧の制御を個々のトランジスタごとに実行することができる相補型MISFETを提供することである。

【解決手段】 相補型のトランジスタのうちのn型トランジスタのゲート絶縁膜8とp型トランジスタのゲート絶縁膜9との対比において、膜厚および組成のうち少なくともいずれか一方が異なる。それにより、ゲート絶縁膜のしきい値電圧が個々のトランジスタごとに異なる。

(もっと読む)

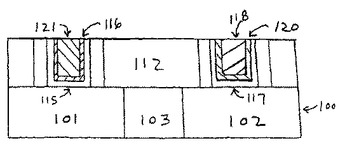

半導体装置およびその製造方法

【課題】 メタルゲート及びhigh-kゲート絶縁膜を有するCMOSにおいて、nMOS及びpMOSトランジスタの低しきい値化を実現する。

【解決手段】 n型MISFET形成領域11のゲート絶縁膜3aはHfO2膜であり、メタルゲート電極4aは、TiN膜と、ゲート絶縁膜との界面に生成されたにゲート電極に含まれるIV族遷移金属と酸素を含むがシリコンは含まない界面層とからなり、その仕事関数はn型MISFETのゲート電極材料に適した4.0〜4.2eVである。p型MISFET形成領域12のゲート絶縁膜3bはHfSiO2/HfO2であり、メタルゲート電極4bはTiNと、ゲート絶縁膜との界面に形成されたにゲート電極に含まれるIV族遷移金属と酸素および金属的シリコン(Si0)からなる界面層とからなり、その仕事関数は、p型MISFETのゲート電極材料に適した4.9eVとなっている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

電界効果トランジスタ及び電界効果トランジスタの製造方法

本発明は電界効果トランジスタの製造方法に関し、シリコンの半導体基体(1)は、いずれもエクステンション(2A、3A)を有する第1の導電型のソース領域(2)及びドレイン領域(3)と、チャネル領域(4)の上に配置されたゲート領域(5)と、が表面に設けられ、エクステンション(2A、3A)及びチャネル領域(4)の隣接部分(4A)の間のpn接合が2つの逆の導電型のドーパントの注入(I1、I2)によって形成され、前記2つの逆の導電型のドーパントの注入(I1、I2)の前に、pn接合が形成される部分にアモルファス化注入が行われる。アモルファス化注入(I0)及び前記2つのドーパント注入(I1、I2)はいずれも、ゲート領域(5)が形成される前に、半導体基体(1)の表面に対してほぼ90度に等しい角度で行われる。この方法では、形成されるpn接合の最も適切な部分、すなわち、表面に対して垂直に走る垂直部分は、極めて急峻で険しいだけでなく、注入の欠点がないので極めて低いリーク電流を有する。好ましくは、結晶構造のシリコンを再成長させるために低温アニールが用いられる。  (もっと読む)

(もっと読む)

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

281 - 298 / 298

[ Back to top ]