Fターム[5F140BG54]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁の形成方法及び除去 (3,620) | 側壁の除去 (394)

Fターム[5F140BG54]に分類される特許

1 - 20 / 394

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】高いオン電流を得つつ、オフリーク電流を抑制することができる半導体装置を簡単に製造することができる方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上にゲート電極を形成する。ドレイン層形成領域に第1導電型の不純物を導入する。次に、熱処理を行うことによってドレイン層形成領域の第1導電型の不純物を活性化する。次に、ソース層形成領域に不活性不純物を導入することによって該ソース層形成領域の半導体基板の単結晶をアモルファス化する。次に、ソース層形成領域に第2導電型の不純物を導入する。次に、半導体基板にマイクロ波を照射することによって少なくともソース層形成領域のアモルファス半導体を単結晶化し、かつ、ソース層形成領域の第2導電型の不純物を活性化する。ソース層形成領域における第2導電型の不純物の深さは、ドレイン層形成領域における第1導電型の不純物の深さよりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造する。

【解決手段】半導体装置の製造方法は、半導体基板50上に絶縁膜を形成する工程と、絶縁膜上に、ゲート電極20およびハードマスク34を順に積層してなる積層体10を形成する工程と、積層体10をマスクとして、半導体基板50にイオン注入を行う工程と、積層体10の側面上に保護膜44を形成する工程と、エッチングによりハードマスク34を除去する工程と、エッチングにより保護膜44を除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

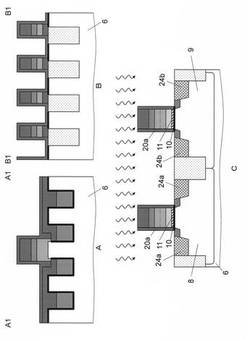

半導体装置および半導体装置の製造方法

【課題】ゲート電極とコンタクトとの間の短絡の発生を抑制する。

【解決手段】基板(2)に設けられた第1拡散領域(3)と、基板(2)に設けられた第2拡散領域(3)と、第1拡散領域(3)に接続された第1コンタクト(11)と、第2拡散領域(3)に接続された第2コンタクト(11)と、第1拡散領域(3)と第2拡散領域(3)の間に設けられたチャネル領域と、ゲート絶縁膜(6)を介してチャネル領域の上に設けられたゲート電極(5)とを具備する半導体装置を構成する。ゲート電極(5)は、第1コンタクト(11)と第2コンタクト(11)とに挟まれた第1領域(A−A’)と、第1領域と異なる第2領域(B−B’)とを備える。第1領域(A−A’)は、第1コンタクト側の第1側面と、第2コンタクト側の第2側面とを含む。第1側面は、第1コンタクトから離れる方向に傾斜する。第2側面は、第2コンタクトから離れる方向に傾斜する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを覆うシリコン窒化膜を用いて、該トランジスタの駆動能力をより一層向上することができるようにする。

【解決手段】Pウェル102の上に、NMOSゲート絶縁膜104を介在させて形成されたNMOSゲート電極106と、Pウェル102におけるNMOSゲート電極106の両側方の領域に形成されたn型ソースドレイン領域112と、Pウェル102の上に形成され、NMOSゲート電極106及びn型ソースドレイン領域112を覆うように形成されたシリコン窒化膜118とを有している。シリコン窒化膜118を構成するシリコンは、その同位体29Si又は30Siの比率が50%以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

トランジスタ及びその製造方法

【課題】駆動電流を向上したnMOSトランジスタを備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の素子領域101の上にゲート絶縁膜111を介在させて形成されたゲート電極112と、素子領域101におけるゲート電極112の両側方に形成され、n型不純物及び炭素を含むソースドレイン領域122とを備えている。ソースドレイン領域122を構成するシリコン及びソースドレイン領域122に含まれる炭素の少なくとも一方は、主同位体よりも質量数が大きい安定同位体の存在比が、天然存在比よりも高い。

(もっと読む)

1 - 20 / 394

[ Back to top ]