Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

241 - 260 / 1,105

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

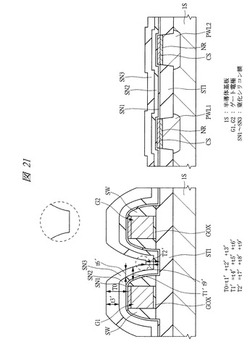

半導体装置及びその製造方法

【課題】 オン抵抗の小さいDMOSトランジスタを含む半導体装置の製造方法を提供することを目的とする。

【解決手段】

CMOSトランジスタ1は、ゲート電極9と、N+型のソース領域3と、N+型のドレイン領域4を備える。DMOSトランジスタ21は、ゲート電極29と、N+型のソース領域23と、N―型のドリフト領域30と、ドレイン領域24と、シリサイド層32aを備える。ゲート電極9のソース領域3側とドレイン領域4側の側部にはサイドウォール8Bが設けられ、ゲート電極29のソース領域23側とドレイン領域24側の側部にはサイドウォール28C、28Dが設けられている。ドレイン領域24側のサイドウォール28Cは、ソース領域23側のサイドウォール28D、及びサイドウォール2Bよりもチャネル方向に沿う厚さが厚い。さらに、シリサイド層32aがゲート電極9上面のドレイン領域24側端まで形成されている。

(もっと読む)

電界効果トランジスタ

【課題】オン動作時における耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、キャリア走行層上に形成され、キャリア走行層とは反対の導電型を有し、キャリア走行層に到る深さまで形成されたリセス部によって分離したキャリア供給層と、分離した各キャリア供給層上にリセス部を挟んで形成されたソース電極およびドレイン電極と、分離した各キャリア供給層上にわたってリセス部内におけるキャリア走行層の表面を覆うように形成されたゲート絶縁膜と、リセス部においてゲート絶縁膜上に形成されたゲート電極と、を備え、ソース電極側のキャリア供給層は、該ソース電極直下に位置するソースコンタクト領域と、ゲート電極の下方に位置し、ソースコンタクト領域よりもキャリア濃度が低いソース電界緩和領域とを有する。

(もっと読む)

半導体装置、半導体装置の製造方法、静電放電保護素子

【課題】製造効率を向上すると共に、内部回路の保護を的確に行う。

【解決手段】サージ電圧が入力パッドPADに入力された際に、ゲート電極501が、Pウェル201にて絶縁層301を介して対面する部分201Bに、キャリアを誘起させるように構成する。これにより、ESD保護素子101において、寄生バイポーラトランジスタの直流電流増幅率hFEを上昇させ、スナップバック開始電圧Vt1を低下させる。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置

【課題】熱的安定性がある一方、密着性が悪くならない程度の仕事関数を有する金属膜または金属化合物よりなる膜をゲート電極として使用した場合に、しきい値電圧を低く抑制できる半導体装置を提供する。

【解決手段】n型MIS素子とp型MIS素子を備えるCMIS素子において、n型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上にケイ窒化タンタル膜よりなるゲート電極10を形成する。一方、p型MIS素子には、ハフニウムアルミネート膜よりなるゲート絶縁膜9上に、酸化アルミニウム膜よりなるしきい値調整膜7を形成する。そして、このしきい値調整膜7上に、ケイ窒化タンタル膜よりなるゲート電極11を形成する。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置

【課題】高周波帯域で高出力動作可能な半導体装置の提供。

【解決手段】半導体装置を、半導体基板12上に形成されたP型Si層13と、絶縁膜を介して設けられたゲート電極3と、ゲート電極3の一方側のP型Si層13内に形成されN型の第1低濃度不純物拡散層44および第1拡散層44より高い不純物濃度を有するN型第2高濃度不純物拡散層45からなるドレイン領域と、第2拡散層45の各辺に対して所定間隔内側に設けられたコンタクトホール53を有する層間絶縁膜9aと、ゲート電極3の他方側のP型Si層13内に形成されN型の高濃度の第3不純物拡散層からなるソース領域41と、素子分離用絶縁膜11と、P型分離拡散層14とを備え、P型分離拡散層14は結晶欠陥を有し、ゲート幅方向の絶縁膜11と第2拡散層45の対向する端部間距離がゲート長方向における第2拡散層45とゲート電極3の対向する端部間の距離より長い。

(もっと読む)

半導体装置、その製造方法および固体撮像装置

【課題】本発明は、gmの低下を抑制し、gds、gmbを維持して、MOSトランジスタの高性能化を可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介して形成されたゲート電極13と、前記ゲート電極13のソース側の前記半導体基板11に形成されたエクステンション領域14と、前記ゲート電極13のソース側の前記半導体基板11にエクステンション領域14を介して形成されたソース領域16と、前記ゲート電極13のドレイン側の前記半導体基板11に形成されたLDD領域15と、前記ゲート電極13のドレイン側の前記半導体基板11にLDD領域15を介して形成されたドレイン領域17を有し、前記エクステンション領域14は前記LDD領域16よりも濃度が高く、前記LDD領域16よりも浅く形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11上の素子領域に設けられるゲート絶縁膜13と、ゲート絶縁膜上に設けられるゲート電極14と、ゲート電極を挟むように半導体基板中に隔離して設けられるソースSまたはドレインDと、半導体基板中に形成される素子分離溝35中の底部および所定の深さDpの側面部にわたって設けられるp型絶縁層15−1と、絶縁層15−1と共に素子分離溝の底部および所定の深さDpの側面部を挟むように半導体基板中に設けられ、素子分離溝の側壁方向に沿ってソースまたはドレインと所定の距離(dS,dD)をもってオフセットするp型不純物拡散層15−2と、絶縁層上おける素子分離溝中の所定の深さDpに設けられる第1素子分離絶縁膜12−1と、第1素子分離絶縁膜上に設けられる第2素子分離絶縁膜12−2とを具備する。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程においてストレッサー膜などから発生する水素によるp型MOSトランジスタの駆動力低下を防止する。

【解決手段】半導体装置は、n型活性領域13B上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16Bと、ゲート絶縁膜15及びゲート電極16Bの側面に形成された内側サイドウォール17及び外側サイドウォール20Bと、p型ソースドレイン領域21Bと、内側サイドウォール17の側面及び外側サイドウォール20Bの側面における少なくとも底部に形成され、水素に対してバリア性を有する絶縁性の水素バリア膜23とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲートラストプロセスで作製するトランジスタにおいて、活性領域と素子分離領域の高さばらつきのためゲートのポリシリコンを抜くことができないことにより、ゲートの抵抗にばらつきが生じるのを防ぐことを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、第1のゲート部30及び第2のゲート部31の上面が共に露出するように、酸化膜16、PMD19、及び第1のゲート部30又は第2のゲート部31の一部を研磨除去する工程、露出された部分より、ポリシリコン12を抜く工程、第1のゲート部30及び第2のゲート部31を覆うメタルを形成する工程を備える。また、第1のゲート部30及び第2のゲート部31の上面が共に露出するようにメタルを研磨除去し、第1のゲート部30と第2のゲート部31で厚みの異なるメタルを残す工程を備えて構成される。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

241 - 260 / 1,105

[ Back to top ]