Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

301 - 320 / 1,105

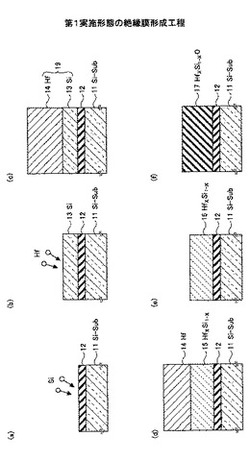

絶縁膜の形成方法および半導体装置の製造方法

【課題】炭素の混入と、組成のばらつきを低減した絶縁膜を形成する。

【解決手段】絶縁膜の形成方法において、基板上にシリコン層と金属層を順次形成してシリコンと金属の2層構造を形成し、前記シリコンと前記金属とが目標とする組成で金属珪化物を生成する反応温度を選択し、前記2層構造を加熱して金属珪化物層を形成する。前記金属のうち、未反応で残る部分を除去する。前記金属珪化物層を酸化又は窒化して、絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】縦型炉を使った半導体装置の製造において、シリコンウェハ裏面を保護することで、工程中でのウェハの汚染を抑制し、又ウェハのデチャックを容易にする。

【解決手段】シリコン基板の一の面は半導体素子を形成するものである。他の面に酸化膜を形成する工程と、第1の膜を、一の面を覆うように、また他の面の酸化膜を覆うように成膜する工程と、第1の膜を、パターニングし、マスクパターンを形成する工程と、一の面に、素子分離領域を形成する工程と、他の面において、第1の膜を除去する工程と、一の面においてゲート絶縁膜28Gを形成する工程と、一の面においてゲート絶縁膜28Gを介してゲート電極29Gを形成する工程と、ゲート電極29Gの両側にソース・ドレイン領域21c,21dを形成し、トランジスタを形成する工程と、他の面に前記酸化膜を維持したまま、半導体基板上方に配線層を形成する工程と、を含む。

(もっと読む)

非常に短いゲート形状を有するトランジスタとメモリセルの製造方法

【課題】強力なプログラム/消去効率及び読み出し速度を示し低い動作電圧を許容する非常に小さいゲート形状及び全体サイズを有した高性能のトランジスタ及びメモリセルを製造して、チャネル長さを劇的にスケーリングできる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体トランジスタを形成する方法において、半導体基板領域上に該半導体基板領域から絶縁されるゲート電極を形成する工程と、前記ゲート電極の側壁(side-walls)に沿ってオフセットスペーサを形成する工程と、前記ゲート電極と各々のソース及びドレイン領域との間のオーバーラップの広さが前記オフセットスペーサの厚さに依存するように、前記オフセットスペーサを形成した後に、前記基板領域内にソース領域及びドレイン領域を形成する工程とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MISFETの移動度劣化を抑制する。

【解決手段】nMISFETQnは、基板1上にゲート絶縁膜3を介してゲート電極4を有している。ゲート絶縁膜3は、酸化シリコンよりも誘電率が高く、ハフニウムを含む酸化膜を有している。ゲート電極4は、ゲート絶縁膜3上に窒化チタン膜5と、窒化チタン膜5上にニッケルリッチのフルシリサイド膜6とを有している。pMISFETQpは、基板1上にゲート絶縁膜11を介してゲート電極12を有している。ゲート絶縁膜11は、酸化シリコンよりも誘電率が高く、ハフニウムを含む酸化膜を有している。ゲート電極12は、ゲート絶縁膜11上にニッケルリッチのフルシリサイド膜6を有している。

(もっと読む)

非常に短いゲート形状を有するトランジスタとメモリセルの製造方法

【課題】強力なプログラム/消去効率及び読み出し速度を示し低い動作電圧を許容する非常に小さいゲート形状及び全体サイズを有した高性能のトランジスタ及びメモリセルを製造して、チャネル長さを劇的にスケーリングできる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体トランジスタを形成する方法において、半導体基板領域上に該半導体基板領域から絶縁されるゲート電極を形成する工程と、前記ゲート電極の側壁(side-walls)に沿ってオフセットスペーサを形成する工程と、前記ゲート電極と各々のソース及びドレイン領域との間のオーバーラップの広さが前記オフセットスペーサの厚さに依存するように、前記オフセットスペーサを形成した後に、前記基板領域内にソース領域及びドレイン領域を形成する工程とを含む。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】電子移動度が高く、リーク電流が小さく、オン抵抗が低い電界効果トランジスタおよび電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有する電界効果トランジスタであって、基板上に形成したp型窒化化合物半導体層と、ソース電極およびドレイン電極下部に位置し、イオン注入により形成されたn型コンタクト領域と、前記p型窒化化合物半導体層上にエピタキシャル成長によって積層されるとともに、一端部がドレイン電極側のn型コンタクト領域に隣接し、他の一端部がゲート電極の前記ドレイン電極側にオーバーラップするように形成され、前記n型コンタクト領域よりもキャリア濃度が低いn型窒化化合物半導体からなる電界緩和層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

パワー半導体装置およびパワー半導体装置の製造方法

【課題】ドレイン領域とドリフト領域との境界近傍における電界集中を緩和することにより、パワー半導体装置のドレイン耐圧を改善する。

【解決手段】パワー半導体装置10は、チャネル領域を含むボディ領域70と、チャネル領域の上にゲート絶縁膜50を介して形成されたゲート電極60と、ボディ領域に取り囲まれた領域に形成されたN型のソース領域130と、ゲート電極60から離間して形成されたドレイン領域140とを備える。ドレイン領域140の周りは、ドレイン領域より不純物濃度が低い拡散領域100により取り囲まれている。また拡散領域100とゲート電極60の下方領域との間に拡散領域100より不純物濃度が低いドリフト領域80が形成されている。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置およびその製造方法

【課題】バルク基板上に形成されたFinトランジスタにおいて、チャネル部の不純物濃度を上昇させることなく、駆動能力を向上させる。

【解決手段】Fin形状の活性領域16の側面に側壁28を形成した後、素子分離溝29に囲まれ、活性領域16よりチャネル長方向およびチャネル幅方向の幅が広い基板領域40を形成する。次に、側壁28を除去し、素子分離溝29間、および活性領域16間を絶縁膜14で埋め、基板領域40上面が露出するまでエッチングする。次に、この基板領域40の上部に不純物注入を行い、パンチスルーストッパー拡散層30を形成することで、Finトランジスタを作製する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース/ドレイン拡散層に形成されるシリサイド層のスパイクやコンタクトの突き抜けを抑制して、接合リークの発生を低減するとともに、シリサイド層を低抵抗化した半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10の上に形成されたトランジスタを有する。トランジスタのゲート電極は、ポリシリコン電極14とその上に形成されたシリサイド層32から構成される。さらに、低濃度ドーピング領域16、高濃度ドーピング領域からなるソース/ドレイン拡散層20、ソース/ドレイン拡散層20上のシリサイド層30を備える。シリサイド層30の表面は、半導体基板10の表面よりも上方に位置している。また、シリサイド層30はシリサイド化反応抑制金属を含み、シリサイド層30の表面から所定の深さに至る領域において、シリサイド層30の表面から基板側へ向かってシリサイド化反応抑制金属の濃度が高くなる濃度プロファイルを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜上にポリシリコン膜3を形成する工程と、前記ポリシリコン膜の下層側に重元素の不純物イオン4をイオン注入する工程と、前記ポリシリコン膜の上層側に、前記重元素より質量の小さい軽元素の不純物イオン6をイオン注入する工程と、前記ポリシリコン膜を加工することにより、前記ゲート絶縁膜上にゲート電極3aを形成する工程と、前記半導体基板に不純物イオンをイオン注入し、熱処理を施すことによりソース・ドレイン領域の拡散層9を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ディボットの影響が抑制される分離構造を備えた半導体装置と、その製造方法を提供する。

【解決手段】素子分離領域Bでは、所定の深さのトレンチ2が形成されている。トレンチ2の底面上および側壁面上には、シリコン窒化膜からなるライナー膜4が形成されている。そのライナー膜4の上には、トレンチ2の深さの途中までを充填するようにシリコン酸化膜7が形成されている。トレンチ2の開口端からトレンチ2の側壁のライナー膜4を経てシリコン酸化膜7にわたり、これらの膜を覆うように、シリコン窒化膜からなるバリアー膜6が形成されている。そのバリアー膜6の表面上には、トレンチ2を最終的に充填するようにシリコン酸化膜9が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネルにおけるキャリアの移動度を向上させつつ、工程数の増加、品質の劣化およびチップサイズの増大を防ぐことができる半導体装置の製造方法を提供する。

【解決手段】Si基板1上に、PMOSトランジスタ2のチャネルに対し圧縮応力を導入する圧縮窒化膜13を形成する。次に、フッ素系ガスとO2ガスを混合した第1の混合ガスを用いて、NMOS領域5に形成された圧縮窒化膜13をエッチングする。次に、PMOS領域4では圧縮窒化膜13上に、NMOS領域5ではSi基板1上に、NMOSトランジスタ3のチャネルに対し引張り応力を導入する引張り窒化膜15を形成する。フッ素系ガスとO2ガスを混合した第2の混合ガスを用いて、PMOS領域4に形成された引張り窒化膜15を圧縮窒化膜13に対して選択的にエッチングする。この際に、第2の混合ガスのO2分圧を第1のガスのO2分圧よりも低くする。

(もっと読む)

半導体装置

【課題】オン抵抗と耐圧のトレードオフを改善した半導体装置を提供することにある。

【解決手段】ソースドレイン方向に複数のトレンチをストライプ状に形成し、そのトレンチの側面および底面ならびにトレンチに挟まれた領域の上面にチャネル領域を形成する半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】オン抵抗の小さいDMOSトランジスタを含む半導体装置を提供する。

【解決手段】ゲート電極27の側壁に形成されるサイドウォール26は、CMOSトランジスタ1のサイドウォール8とは異なり、ドレイン側とソース側とで、水平方向(半導体層2の表面に沿った方向)の厚さが異なっており、ドレイン側のサイドウォール26Bは、ソース側のサイドウォール26Aよりも厚い。ソース側のサイドウォール26Aは、CMOSトランジスタ1のサイドウォール8と略同一の厚さを有している。ドリフト領域23、LDD領域25、ドレイン領域21、及びソース領域24は、これらサイドウォール26A、26Bに自己整合的に形成される。このため、LDD領域25は、ドリフト領域23に比べ、サイドウォール26A、26Bの厚さの差の分だけ水平方向の長さが小さくされている。

(もっと読む)

半導体装置の製造方法

【課題】低温領域でも充分な増速酸化現象が起こって大きな酸化速度が得られる熱酸化方法を提供することにある。また、低温領域で形成しても高い信頼性を有する酸化シリコン膜を成膜できる熱酸化方法を提供する。

【解決手段】本発明の基本概念は、プラズマを用いることなく、反応性の大きい酸素ラジカルを大量に生成し熱反応で酸化シリコン膜を形成することにある。具体的には、オゾン(O3)を活性な他のガスと反応させることで、低温領域でも高効率にオゾン(O3)を分解して酸素ラジカル(O*)を大量に発生させることを特徴とする。例えば、活性なガスとしては、ハロゲン元素を含む化合物ガスなどを用いることができる。

(もっと読む)

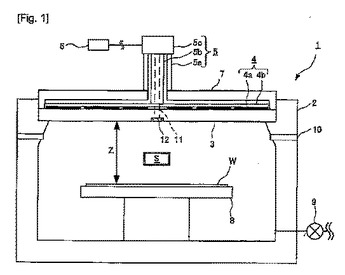

シリコン酸化膜の成膜方法、シリコン酸化膜、半導体装置および半導体装置の製造方法

プラズマ処理装置1のチャンバ2内に、シリコン化合物ガス、酸化性ガス、および希ガスを供給する。マイクロ波をチャンバ2内に供給し、マイクロ波により生成されたプラズマで、被処理基板上にシリコン酸化膜を形成する。希ガスの分圧比は、シリコン化合物ガスと酸化性ガスと希ガスを併せたトータルガス圧の10%以上の割合であって、シリコン化合物ガスと酸化性ガスの有効流量比(酸化性ガス/シリコン化合物ガス)は、3以上11以下とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】生産性を損なうことなく、MISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1の主面s1のNMIS領域RNには素子用pウェルpwを、PMIS領域RPには素子用nウェルnwを形成した後、主面s1に順に形成したゲート絶縁膜GIおよび第1多結晶シリコン膜E1aを透過させるようにしてアクセプタとなる不純物イオンを注入して、チャネル領域CHの不純物濃度を調整する。その後、第1多結晶シリコン膜E1aおよびその上に形成した第2多結晶シリコン膜のうち、NMIS領域RNにはドナー不純物を、PMIS領域RPにはアクセプタ不純物を注入した後、これらを加工して、n型のゲート電極とp型のゲート電極とを形成する。ゲート絶縁膜GIは、シリコン基板1の主面を酸化した後、炉体内において一酸化二窒素雰囲気中で熱処理を施すようにして形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイドブロック層の除去方法を工夫することで、良好な抵抗値を持つシリサイド層を形成することができる半導体装置の製造方法を得る。

【解決手段】シリサイドブロック層10を反応性イオンエッチングで除去する際、反応性イオンエッチングの終点検出前よりも反応性イオンエッチングの終点検出後のほうが、イオン引き込み用のバイアス高周波電力の電圧振幅値であるVppが高くなるように設定する。

(もっと読む)

301 - 320 / 1,105

[ Back to top ]