Fターム[5F140BH17]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | DDD(Doble doped dorain) (528)

Fターム[5F140BH17]に分類される特許

1 - 20 / 528

半導体装置

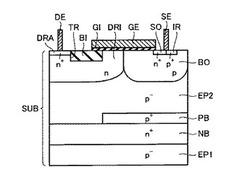

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置

【課題】特性の優れた半導体装置を提供する。

【解決手段】本発明の一態様にかかる半導体装置は、半導体基板1に設けられた第1導電型のN−型オフセット層8と、トレンチ12を有し、N−型オフセット層8の間に設けられた第2の導電型のチャネル領域13と、チャネル領域13の上に形成され、トレンチ12に埋設されたトレンチゲート10を有するゲート電極4と、を備えたトランジスタを含み、ゲート幅方向におけるトレンチゲート10の幅がゲート長方向の位置に応じて変化しているものである。

(もっと読む)

半導体装置

【課題】長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に前記第1トレンチ領域の長さ方向の両端に接して設けられた第2トレンチ領域014および第3トレンチ領域015と、トレンチ領域に形成された第2導電型のウェル領域005と、前記第1トレンチ領域に設けられたゲート絶縁膜004と、前記ゲート絶縁膜上に接して設けられたゲート電極003と、前記第1トレンチと前記第2トレンチ領域と前記第3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置

【課題】1T−DRAMにおいて、高いGIDL電流は、主にPN接合でのリーク電流によるものであり、データ保持時にリーク電流が発生する原因にもなり、DRAMにおける電荷保持時間を低下させている。

【解決手段】ドレイン拡散層のうちゲート電極とオーバーラップする部分を、不純物濃度の異なる2つの部分に分けている。これら2つの部分のうち、不純物濃度がより低い一方の部分では、ボディ部に隣接しており、電界が低減されるためリーク電流が抑制される。また、不純物濃度がより高い他方の部分では、ボディ部から絶縁されており、ゲート絶縁層との界面において比較的大きなトンネル効果が得られる。その結果、GIDL電流を増大しつつ、PN接合によるリーク電流を抑制し、データ保持時間を増大させることが可能となっている。

(もっと読む)

半導体装置

【課題】アバランシェ降伏電流が流れている状態において寄生トランジスタのターンオンを抑制することにより、十分なアバランシェ耐量を確保することのできる半導体装置を提供する。

【解決手段】基板の表面ではn型領域とベース領域とが隣接している。エミッタ/ソース領域はベース領域内でn型領域から離れている。ゲート絶縁膜はn型領域とエミッタ/ソース領域との間でベース領域を覆い、その上にゲート電極が形成されている。ドレイン領域とコレクタ領域とはn型領域内でベース領域から離れている。コレクタ接続領域はn型領域内で、ベース領域、ドレイン領域、及びコレクタ領域のいずれからも離れている。ドレイン電極はドレイン領域に接続されている。コレクタ電極はコレクタ領域とコレクタ接続領域とに接続されている。ゲートターンオフ状態でドレイン電極にアバランシェ降伏電流が流れるとき、コレクタ電極の電位がドレイン電極の電位よりも低い。

(もっと読む)

半導体装置

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置

【課題】 出力回路用、或いは、アナログ回路用の2種類の特性に夫々特性が最適化されてなるトランジスタを備えた半導体装置を低コストで提供する。

【解決手段】

同一基板101上に、出力回路用の第1のトランジスタ1aと、アナログ回路用の第2のトランジスタ1bが搭載された半導体装置であって、各トランジスタのゲート絶縁膜が、ドリフト領域107上面の一部の領域において、膜厚の厚い厚膜絶縁膜108bとなっており、ボディ領域103に向かって延伸するドリフト領域107を、第1のトランジスタ1aでは当該厚膜絶縁膜108bのボディ領域103側境界Aを超えて延伸させ、第2のトランジスタ1bでは当該厚膜絶縁膜108bのボディ領域側境界Aよりも内側にとどまるように延伸させる。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置

【課題】信頼性が高い半導体装置を提供する。

【解決手段】例えば、ドレイン用の半導体層DF2(n),DF1(n+)およびコンタクト層CNTdと、ソース用の半導体領域DFAおよびコンタクト層と、ソース・ドレイン間に配置されるゲート層GTとを備える。ソース用のコンタクト層は、長辺側に対応する2個のコンタクト層CNTs1,CNTs2で構成され、短辺側に対応する部分には配置されない(C1−C1’間でY軸方向に延伸するコンタクト層は備えない)。また、ドレイン用のCNTdとDF1(n+)の短辺側の間隔X1は、長辺側の間隔Y1よりも例えば3倍以上広い。

(もっと読む)

半導体装置

【課題】低オン抵抗特性を有するパワーMOSトランジスタのスイッチング特性を、従来以上に改善した高効率パワーMOSトランジスタを実現する。

【解決手段】Finger形状電極からなるソース電極8とドレイン電極9の間をFinger形状電極の一方の端部GE1から他方の端部GE2まで延在するゲート電極6と、層間絶縁膜7に形成されたコンタクトホールを介してゲート電極6の端部GE1、GE2とそれぞれ接続されるゲート引き出し電極と、前記層間絶縁膜7上を被覆するパッシベーション膜12と、該パッシベーション膜12の開口に露出する前記ゲート引き出し電極の一部となるゲート接続電極G1、G2と、該ゲート接続電極G1、G2に形成された突起電極25を備える半導体チップ100を、該突起電極25を介して、BGA基板200の表面201に形成された低抵抗のゲート電極シャント用基板配線23に接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ横型パワーMOSFETにおいて、装置の信頼性を高めること。

【解決手段】半導体基板1の表面層にトレンチ5を形成する。トレンチ5は、半導体基板1の表面層を第1メサ領域41と第2メサ領域42に分割し、かつ第1メサ領域41と第2メサ領域42を交互に配置させる。第1メサ領域41および第2メサ領域42は、それぞれソース電流およびドレイン電流の引き出しをおこなう。第2メサ領域42は、半導体基板1からの深さが、第1メサ領域41よりも深くなっている。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

1 - 20 / 528

[ Back to top ]