Fターム[5F140BK03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | LDD領域、エクステンション領域の形成 (1,808) | 外側(高不純物)領域→内側(低不純物)領域 (104)

Fターム[5F140BK03]に分類される特許

1 - 20 / 104

半導体装置及び半導体装置の製造方法

半導体装置および半導体装置の製造方法

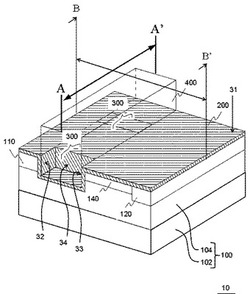

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置の製造方法

【課題】高いオン電流を得つつ、オフリーク電流を抑制することができる半導体装置を簡単に製造することができる方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上にゲート電極を形成する。ドレイン層形成領域に第1導電型の不純物を導入する。次に、熱処理を行うことによってドレイン層形成領域の第1導電型の不純物を活性化する。次に、ソース層形成領域に不活性不純物を導入することによって該ソース層形成領域の半導体基板の単結晶をアモルファス化する。次に、ソース層形成領域に第2導電型の不純物を導入する。次に、半導体基板にマイクロ波を照射することによって少なくともソース層形成領域のアモルファス半導体を単結晶化し、かつ、ソース層形成領域の第2導電型の不純物を活性化する。ソース層形成領域における第2導電型の不純物の深さは、ドレイン層形成領域における第1導電型の不純物の深さよりも浅い。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置の製造方法

【課題】不純物イオン注入時に形成されたフレンケル型結晶欠陥を終端させ、ボロンの増速拡散を抑制することで、逆短チャンネル効果を改善した半導体装置の製造方法を提供する。

【解決手段】MOS型トランジスタを備えた半導体装置の製造方法において、MOSトランジスタは、P型ウェル領域と、N型ソース・ドレイン領域と、チャネル領域と、ゲート電極と、からなるNMOSトランジスタであって、N型ソース・ドレイン領域を不純物イオン注入により形成する工程と、ソース・ドレイン領域と同一領域に、ハロゲン元素をイオン注入する工程と、ソース・ドレイン領域を活性化させるための活性化熱処理工程とを含む。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】混晶層に発生する転位、結晶欠陥を抑制することができる半導体装置を提供すること。

【解決手段】p型のSi基板13表面のn型ウェル層16の両端に形成され、SiおよびGeからなる混晶層18と、これらの混晶層18の表面にそれぞれ形成されたp型の不純物注入層19、20と、これらの不純物注入層19、20をそれぞれドレイン領域、ソース領域とするpMOSFET15−1と、を具備する素子領域11と、この素子領域11を囲うようにSi基板13の表面に形成された素子分離層14−1と、この素子分離層14−1外のSi基板13の表面に前記素子領域11の混晶層18と同一材料で形成され、その主方向が、Si基板13の<110>方向とは異なるダミーパターン35と、を具備する。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

多重Vt電界効果トランジスタ素子

【課題】 多重閾値電圧(Vt)電界効果トランジスタ(FET)素子、及びその製造のための技術を提供する。

【解決手段】 1つの態様において、ソース領域と、ドレイン領域と、ソース領域とドレイン領域とを相互接続する少なくとも1つのチャネルと、チャネルの少なくとも一部を囲み、ゲート全体に対し選択的に配置された少なくとも1つのバンド・エッジ金属により多重閾値電圧を有するように構成されたゲートとを含むFET素子が提供される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル特性を低下させることなく、チャネル領域に十分な歪みを生じさせることのできる半導体層が埋め込まれたソース・ドレイン領域を有する半導体装置およびその製造方法を提供する。

【解決手段】N型のシリコン基板11の主面にゲート絶縁膜を介して形成されたゲート電極13と、ゲート電極13の下方に形成されるチャネル領域14を挟むように形成され、チャネル領域14に歪みを与えるためのゲルマニウム、P型不純物のボロンおよびボロンの拡散を抑制するためのカーボンを含有する第1半導体層15a、15bと、ゲルマニウムおよびボロンを含有する第2半導体層16a、16bと、が順に積層された構造を有するソース・ドレイン領域17a、17bと、第2半導体層16a、16bのゲート電極13側の側面からチャネル領域14に隣接するエクステンション領域18a、18bと、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ、P型トランジスタともに低い閾値電圧が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板上の第1領域201にN型トランジスタが形成され、前記基板上の第2領域202にP型トランジスタが形成された半導体装置101であって、前記基板111と、シリコンを含有する第1のゲート絶縁膜121と、第1の金属と酸素とを含有する第2のゲート絶縁膜122と、前記第1の金属と異なる第2の金属と酸素とを含有する第3のゲート絶縁膜123と、ハフニウムを含有する第4のゲート絶縁膜124と、金属と窒素とを含有するゲート電極層131とを備え、前記第2領域に形成された前記ゲート電極層の厚さは、前記第1領域に形成された前記ゲート電極層の厚さよりも厚くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、ゲート容量が大きく、スイッチング素子としての高速動作が実現し難いという問題があった。

【解決手段】本発明の半導体装置では、トレンチ9内にはゲート酸化膜10、絶縁スペーサー11及びゲート電極12が形成され、絶縁スペーサー11はトレンチ9の側面に沿って一環状に形成される。この構造により、絶縁スペーサー11の膜厚によりゲート容量が低減し、高集積化によるオン抵抗値も低減することで、スイッチング素子としての高速動作が実現される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の空乏化と、ゲート電極内の不純物量の減少ないしはバラつきと、イオンがゲート絶縁膜を突き抜けてしまうことに起因したゲート絶縁膜の信頼性低下及び閾値変動を抑制する。

【解決手段】第1注入工程(図1(b)、図1(c))と第2注入工程(図1(d)、図1(e))を備える。第1注入工程ではゲート絶縁膜5と、ゲート電極9、10となる膜6と、が形成された半導体基板1のゲート電極9、10となる部分に、n型又はp型の導電型のイオンを注入する。第2注入工程では、ゲート電極9、10に同じ導電型のイオンを注入する。第1注入工程で注入するイオンの質量は、第2注入工程で注入するイオンよりも大きくする。これにより第1注入工程による不純物の濃度分布の縦方向におけるピーク位置を、第2注入工程による不純物のピーク位置よりもゲート絶縁膜5寄りにする。

(もっと読む)

1 - 20 / 104

[ Back to top ]