Fターム[5F140BK27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース、ドレイン電極形成前の処理 (1,173) | コンタクトホールの形成 (1,071) | エッチング (548) | SAC(セルフアラインコンタクト) (178)

Fターム[5F140BK27]に分類される特許

1 - 20 / 178

半導体装置及び半導体装置の製造方法

半導体装置の製造方法

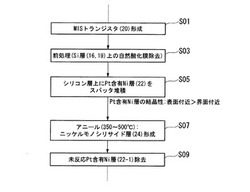

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】ゲート電極用溝18の底部に設けられた第1の不純物拡散領域27と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第2の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように半導体基板13に設けられ、第1の不純物拡散領域27と接合された第3の不純物拡散領域29と、を有する。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

トランジスタ及びその製造方法

【課題】駆動電流を向上したnMOSトランジスタを備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の素子領域101の上にゲート絶縁膜111を介在させて形成されたゲート電極112と、素子領域101におけるゲート電極112の両側方に形成され、n型不純物及び炭素を含むソースドレイン領域122とを備えている。ソースドレイン領域122を構成するシリコン及びソースドレイン領域122に含まれる炭素の少なくとも一方は、主同位体よりも質量数が大きい安定同位体の存在比が、天然存在比よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

1 - 20 / 178

[ Back to top ]