Fターム[5F140CE10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 同一真空処理 (148)

Fターム[5F140CE10]に分類される特許

101 - 120 / 148

半導体集積回路装置の製造方法

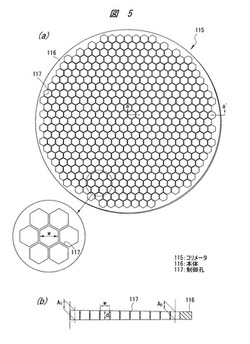

【課題】スパッタリング法により形成される膜のウエハ面内の膜厚分布の均一性を向上させることのできる技術を提供する。

【解決手段】コリメータ115の本体116を中央部から周辺部にかけて徐徐に薄くして、本体116に設けられる多数個の制御孔117のアスペクト比をコリメータ115の中央から外側にかけて連続的に小さくする。このコリメータ115をウエハとターゲットとの間に設置し、300℃以上に加熱されたウエハの上に膜厚10nm程度のコバルト膜を堆積し、続いてコバルト膜の上に窒化シリコン膜を堆積した後、シリサイド反応によりコバルトダイシリサイド層を形成する。

(もっと読む)

炭化珪素半導体素子の製造方法

【課題】ある程度の膜厚をもつ絶縁膜を成膜する場合であっても、SiO2/SiC界面

に残留するカーボンクラスターを効率的に除去または不活性化できる炭化珪素半導体素子の製造方法を提供する。

【解決手段】絶縁膜を形成する工程において、O2および/またはH2Oを含有する酸化性ガスの雰囲気下で炭化珪素エピタキシャル膜が成膜された基板を熱処理することにより該基板の表面において熱酸化膜の膜厚を増加させた後、NO、N2OまたはNO2を含有するガスの雰囲気下で該基板を熱処理してSiO2/SiC界面にあるカーボンクラスターを

除去等する工程を、複数回繰り返すようにした。

(もっと読む)

半導体装置の製造方法

【課題】均一な膜厚でかつ局所的な表面粗さの小さいゲート絶縁膜を形成する。

【解決手段】シリコン基板表面に熱酸化または熱酸窒化によってシリコン酸化膜またはシリコン酸窒化膜を形成した後(ステップS1)、そのシリコン酸化膜表面またはシリコン酸窒化膜表面にプラズマ窒化処理を施す(ステップS2)。このプラズマ窒化処理により、そのシリコン酸化膜表面またはシリコン酸窒化表面に高活性な窒素原子を生成させて活性な状態にする。そして、プラズマ窒化処理後のシリコン酸化膜表面またはシリコン酸窒化表面を大気に曝露させないようにプラズマ窒化処理に連続してALD処理を施し、その上にシリコン窒化膜を堆積する(ステップS3)。

(もっと読む)

スペーサレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法

【課題】 スペースレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法を提供する。

【解決手段】 歪み強化がnFET及びpFETデバイスの両方に対して達成される半導体構造体及びそれを製造する方法を提供する。特に、本発明は、より強い歪み強化及び欠陥削減のための少なくとも1つのスペーサレスFETを提供する。少なくとも1つのスペーサレスFETは、pFET、nFET又はそれらの組合せとすることができるが、一般に、pFETはnFETよりも大きな幅を有するように製造されるので、スペーサレスpFETが特に好ましい。少なくとも1つのスペーサレスFETは、スペーサを有するFETを含んだ従来技術の構造体よりも、デバイス・チャネルにより接近した応力誘起ライナを設けることを可能にする。スペーサレスFETは、スペーサレスFETの下側に侵入しない、対応するシリサイド化ソース/ドレイン拡散コンタクトの抵抗に悪影響を与えることなく達成される。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】炭素濃度を十分に高くすることが可能な高融点金属の金属化合物膜よりなる薄膜を形成することが可能な成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器4内に、高融点金属有機材料ガスと窒素含有ガスとを供給して被処理体の表面に高融点金属の金属化合物膜よりなる薄膜を形成する成膜方法において、前記薄膜中に含まれる炭素濃度を高めるために前記窒素含有ガスの分圧を、全圧の10%以下となるように設定して成膜工程を行うようにする。これにより、炭素濃度を十分に高くし、トランジスタのゲート電極の閾値を低減させる。

(もっと読む)

成膜方法およびコンピュータ可読記録媒体

【課題】 シリコン基板上に、しきい値特性のシフトを生じないリーク電流特性に優れたHfSiO4膜を形成する。

【解決手段】 希フッ酸処理したシリコン基板表面に、Hfと窒素を含む有機金属原料を供給し、HfNの核形成を行い、前記核形成工程の後、前記シリコン基板表面に、Hfを含む有機金属原料とSiを含む有機原料とを供給し、Hfシリケート膜をCVD法により成膜する。

(もっと読む)

半導体デバイスの製造方法

【課題】従来は選択エピタキシャル成長を行う前に、自然酸化膜除去をする為にH2アニールを高温で処理しなければならなかったが、それを止めて低温で前処理が可能な成膜工程を備える半導体デバイスの製造方法を提供する。

【解決手段】ウェハの温度を700℃に保って、エピタキシャル成長の前処理としてジクロールシランの分圧を0.25Pa、Cl2の分圧を0.03Pa、全圧100Paにして自然酸化膜除去をし、その後に前処理で使用した同じガスを分圧比を異ならせて、具体的にはジクロールシランの分圧を0.5Pa、Cl2の分圧を0〜0.05Pa、全圧100Paにして減圧CVD法によりSi膜を成膜する。

(もっと読む)

ミラー容量低下及び駆動電流改善のための単一ゲート上の複数の低及び高Kゲート酸化物

【課題】 本発明は、ミラー容量、すなわち、オーバーラップ容量が低減され、駆動電流が改善された少なくとも1つのCMOSデバイスを有する半導体構造体を提供する。

【解決手段】 本発明の構造体は、少なくとも1つの重層ゲート導電体を備える半導体基板であって、少なくとも1つの重層ゲート導電体のそれぞれが垂直縁部を有する半導体基板と、少なくとも1つの重層ゲート導電体の下に位置する第1のゲート酸化物であって、少なくとも1つの重層ゲート導電体の垂直縁部を超えて延長しない第1のゲート酸化物と、少なくとも1つの重層ゲート誘電体の少なくとも一部の下に位置する第2のゲート酸化物とを備える。本発明によると、第1のゲート酸化物及び第2のゲート酸化物は、第1のゲート酸化物が高kであるとき第2のゲート酸化物は低kであり、あるいは前記第1のゲート酸化物が低kであるとき前記第2のゲート酸化物は低kであるという条件で、高k酸化物含有材料及び低k酸化物含有材料から選択される。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極間の短絡の防止、及びキャパシタ下部電極に起因する容量絶縁膜のリーク電流増大防止が可能な半導体装置の製造方法を提供する。

【解決手段】 半導体基板100上にアモルファスシリコン膜102を形成し、アモルファスシリコン膜102の表面に、アモルファスシリコン膜102の表面のマイグレーションを防止するストッパ膜10を形成し、その後、アモルファスシリコン膜102の表面からストッパ膜10を除去する。ストッパ膜10により、アモルファスシリコン膜120形成後に、低圧の反応室内で長時間保持されても、アモルファスシリコン膜の表面マイグレーションを防止し、表面上の微小なシリコン核が2次成長することを抑制する。

(もっと読む)

ゲート誘電体層の高K窒化物形成における窒素プロファイルエンジニアリング

窒化されたゲート誘電体を形成するための方法及び装置。方法は、プラズマ窒化プロセスを用いて誘電体膜に窒素を取込んで、窒化されたゲート誘電体を形成するステップを含む。第一ステップは、ゲート誘電体膜を備える基板を準備することを含む。第二ステップは、基板上に電圧を誘導することを含む。最後に、電圧を維持しながら窒素源を備えるプラズマに基板を曝して、基板上に窒化されたゲート誘電体を形成する。一実施形態において、基板を支持する静電チャックに電圧を印加することによって電圧を基板上に誘導させる。他の実施形態において、基板に隣接して位置する電極にDCバイアス電圧を印加することによって基板上に電圧を誘導させる。 (もっと読む)

ゲート電極構造及び製造方法

電界効果トランジスタ内に用いられるゲート電極構造及び集積回路及び製造方法が開示される。その方法と構造によって仕事関数と閾値調整が改善される。 (もっと読む)

半導体ガスセンサとその製造方法

【課題】電界効果トランジスタ型のガスセンサにおいて、あらかじめトランジスタ構造を形成した後、検知対象のガスに対応した感応材料の電極を形成する際に、ゲート絶縁膜を損なうことなく、かつ、閾値ばらつきを抑制する製造方法を供給する。

【解決手段】ゲート絶縁膜を少なくともSiO2とSRN(Si Rich Nitride)膜との積層構造とする。SRN膜が層間絶縁膜を加工してゲート絶縁膜を露出する場合の加工のストッパ膜となる。ゲート絶縁膜の耐圧はSiO2で保持する。SRN膜はSi3N4膜に比べて低電圧で膜のチャージを除去することができるため、ガスセンサトランジスタの閾値ばらつきを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 接合リークを増大させることがなく、低抵抗なコンタクトを半導体基板の全面で安定して形成することができる半導体装置、及びその製造方法を提供する。

【解決手段】 半導体層を有する基板1上に、金属酸化物からなるライナ膜26と絶縁膜22からなる層間絶縁膜20を形成する。次に、絶縁膜22上に、コンタクトホール24の形成位置に開口部を有するマスクパターン23を形成する。そして、マスクパターン23をエッチングマスクとして絶縁膜22をエッチング除去し、ライナ膜26を露出させる。この後、露出したライナ膜26を真空中でエッチング除去し、半導体基板1を露出させ、当該真空中で連続して、露出した半導体基板1上に導電膜を形成することでコンタクト構造を形成する。

(もっと読む)

電子デバイス材料の製造方法

【課題】極めて薄い(例えば2.5nm以下)膜厚を有する絶縁膜としてSiO2膜およびSiON膜を用い、電極としてポリシリコン、アモルファスシリコン、SiGeを用いた良好な電気特性を有する電子デバイス(例えば高性能MOS型半導体装置)構造の製造方法を提供する。

【解決手段】酸素、および希ガスを含む処理ガスの存在下で、ウエハW上に平面アンテナ部材SPAを介してマイクロ波を照射することにより、酸素と希ガスとを含むプラズマ(ないし窒素と希ガスとを含むプラズマ、または窒素と希ガスと水素を含むプラズマ)を形成する。このプラズマを用いて前記ウエハ表面に酸化膜(ないし酸窒化膜)を形成し、必要に応じてポリシリコン等の電極を形成して電子デバイス構造を形成する。

(もっと読む)

プラズマ窒化したゲート誘電体を2段階式で窒化後アニーリングするための改善された製造方法

シリコンオキシナイトライドゲート誘電体の形成方法である。この方法は、シリコンオキシナイトライド膜を形成するために、プラズマ窒化処理を使用して誘電体膜内に窒素を組み込むステップを含む。シリコンオキシナイトライド膜は、第1環境内でアニーリングされる。第1環境は、第1温度にある第1酸素部分圧を伴った不活性環境を備える。次に、シリコンオキシナイトライド膜は、第2温度にある第2酸素部分圧を備える第2環境内でアニーリングされる。第2酸素部分圧は第1酸素部分圧よりも高い。 (もっと読む)

半導体装置の製造方法

【課題】 ファセット形状のない金属シリサイド層を形成し、ソース・ドレインとシリコン基板との間の接合リークを減少させる。

【解決手段】 シリコン基板1の上にソース・ドレイン5を形成し、その上にシリサイド化用金属膜(Ni膜)6、ストレス膜7を形成する。ストレス膜7としてTiN膜およびCo膜からなる積層膜を形成する。この状態でシリサイド化アニールを行うと、ストレス膜7は引っ張り応力10aを有する。この応力に対応するように、シリサイド化用金属膜6は圧縮応力10bを有する。

このようにしてシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させることにより、反応速度が抑制される。このため、ファセット形状を有しないNiモノシリサイド層(NiSi)を形成することができる。これにより、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を減少させることができる。

(もっと読む)

ゲート絶縁膜の製造方法および半導体装置の製造方法

【課題】 薄膜化しても、半導体装置に優れた電気的特性を付与できる良質なゲート絶縁膜を製造する。

【解決手段】 プラズマ処理装置の処理室内で、被処理体表面のシリコンに酸素含有プラズマを作用させてシリコン酸化膜を形成する酸化処理工程を含むゲート絶縁膜の製造方法であって、前記酸化処理工程における処理温度は600℃超1000℃以下であり、前記酸素含有プラズマは、少なくとも希ガスと酸素ガスとを含む酸素含有処理ガスを前記処理室内に導入するとともに、アンテナを介して該処理室内に高周波またはマイクロ波を導入することによって形成される前記酸素含有処理ガスのプラズマであることを特徴とする、ゲート絶縁膜の製造方法。

(もっと読む)

高誘電率膜上のシリコンオキサイドキャップ

【課題】高kゲート絶縁膜上のドープされたシリコンゲート間に短絡をもたらす欠陥、トラッピングを回避する、前記高kゲート絶縁膜および前記高kゲート絶縁膜上のシリコンオキサイド膜の製造法を提供する。

【解決手段】原子層堆積プロセスを用いて基板上に高kゲート絶縁材料を堆積することを包含する、半導体基板上に集積回路構造を形成するための方法。シリコンオキサイドキャッピング層は、高速熱化学蒸着プロセスにおいてゲート絶縁材料上に堆積される。ゲート電極は、シリコンオキサイドキャッピング層上に形成される。

(もっと読む)

自己整合され積極的にスケーリングされたCMOSデバイスにおけるゲート電極の金属/金属窒化物二重層のCMOS構造体及び半導体構造体

【課題】 低仕事関数金属の不適切な熱安定性のために、nFET仕事関数とpFET仕事関数との両方を適正にするために用いることができるゲート・スタックを有するCMOS構造体を提供すること。

【解決手段】 本発明は、半導体基板の1つの領域上に配置された少なくとも1つのnMOSデバイスと、半導体基板の別の領域上に配置された少なくとも1つのpMOSデバイスとを含む、CMOS構造体に向けられる。本発明によれば、少なくとも1つのnMOSデバイスは、ゲート誘電体と、4.2eV未満の仕事関数を有する低仕事関数の元素状金属と、その場金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを含み、少なくとも1つのpMOSデバイスは、ゲート誘電体と、4.9eVより大きい仕事関数を有する高仕事関数の元素状金属と、金属キャッピング層と、ポリシリコン・カプセル化層とを含むゲート・スタックを有する。本発明はまた、こうしたCMOS構造体を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法

【課題】 酸化種の拡散による応力の発生を抑制してリーク電流の更なる低減を図る。

【解決手段】 半導体基板上に、隣接する素子を電気的に分離するための素子分離領域104としてトレンチ形状の埋め込み絶縁領域を形成した後、全面にシリコン酸化膜109を形成する。さらに、シリコン酸化膜109上にシリコン窒化膜110を形成し、そのシリコン窒化膜110全体を酸化することでシリコン酸化膜を得る。

(もっと読む)

101 - 120 / 148

[ Back to top ]