Fターム[5F140CE10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 同一真空処理 (148)

Fターム[5F140CE10]に分類される特許

61 - 80 / 148

半導体素子及び半導体素子の製造方法

【課題】急峻な不純物分布のhalo層を備える半導体素子及び半導体素子の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体素子1は、半導体基板10と、半導体基板10に設けられる凸領域12と、凸領域12上に設けられるゲート絶縁膜100と、ゲート絶縁膜100の下の凸領域12内に位置するチャネル領域101と、凸領域12の両側に設けられ、チャネル領域101の両側にエクステンション115aを有するソースドレイン領域115と、凸領域12とソースドレイン領域115との間に設けられ、凸領域12と接触する部分に境界を有して設けられるhalo層110とを備える。

(もっと読む)

半導体装置の製造方法

【課題】可及的に少ない工程で高精度且つ容易に2種の半導体層を選択形成し、工程の簡素化を図り工程数及び製造コストの大幅な削減をするも、各導電型のトランジスタに適合して素子性能の高い半導体装置を実現する。

【解決手段】P型MOSトランジスタの素子領域及びN型MOSトランジスタの素子領域の双方に、例えばエピタキシャル成長法によりSiC層を選択的に同時形成し、N型MOSトランジスタの素子領域にマスク層を形成し、マスク層を用いて、P型MOSトランジスタの素子領域に形成されたSiC層を除去し、例えばエピタキシャル成長法によりSiGe層を選択的に形成した後、マスク層を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置のゲート酸化膜上に窒化珪素層を形成し、窒化物層を熱処理する方法

【課題】従来技術の問題の少なくとも一つを解決する、ゲート酸化膜上に窒化珪素膜を形成する方法を提供する。

【解決手段】半導体装置におけるゲート構造の形成の一部として、ゲート酸化膜上に窒化珪素膜を形成する方法であって、窒化処理プロセスにより、半導体基板のゲート酸化膜の上部に、窒化珪素の層を形成するステップと、熱処理チャンバ内で、前記半導体基板を加熱するステップと、前記熱処理チャンバ内で、前記半導体基板をN2に暴露するステップと、前記熱処理チャンバ内で、前記半導体基板をN2およびN2Oの混合物に暴露するステップと、を有する方法。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体デバイスの製造方法及び半導体デバイス製造装置及び半導体デバイス製造システム

【目的】本発明は、窒素成分の抜けが少なく、ゲートリーク電流の増大を抑制することができるHigh−kゲート絶縁膜を成膜する、High-kゲート絶縁膜の成膜方法を提供する。

【解決手段】 第一の処理部にて、シリコン基板上にHigh-kゲート絶縁膜を形成する工程と、シリコン基板を第二の処理部に搬入する工程と、前記ゲート絶縁膜を窒素及び希ガス含有ガスでHigh-kゲート絶縁膜を窒化する工程と、 前記窒化された基板を前記第二の処理部でアニール処理する工程とを有する半導体デバイスの製造方法。

(もっと読む)

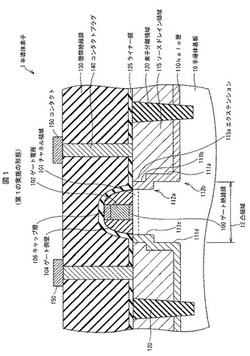

電界効果トランジスタ

【課題】ゲートの漏れ電流を低減させる。

【解決手段】電子トラップ及びゲート電流の漏れを減少させる窒化物系FETデバイス10である。該デバイスは、デバイスの加工に起因するトラップを減少させるため比較的厚い不動態化層20と、ゲート電流の漏れを減少させるためゲート端子38の下方の薄い不動態化層16、18とを含む。デバイスは、基板12上に堆積させた半導体デバイス層14を含む。複数の不動態化層が半導体デバイス層14上に堆積され、少なくとも2つの層はエッチストップを提供し得るよう異なる誘電性材料にて出来ている。層の間の境界面をエッチストップとして使用することにより1つ又はより多くの不動態化層18、20を除去し、ゲート端子38と半導体デバイス層14間の距離を正確に制御することができるようにし、この距離はデバイスの性能を向上させ且つゲート電流の漏れを減少させるよう極めて短くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域として用いるエピタキシャル成長結晶からゲート絶縁膜への不純物拡散による信頼性の低下を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、第1の面と、前記第1の面に対して傾斜した第2の面とを有するSiGe結晶層を形成する工程と、前記SiGe結晶層上に非晶質Si膜を形成する工程と、加熱処理を施すことにより、前記SiGe結晶層の前記第1および第2の面をシードとして、前記非晶質Si膜の前記第1および第2の面の近傍に位置する部分を結晶化させてSi結晶層を形成する工程と、前記非晶質Si膜の加熱処理により結晶化しなかった部分を選択的に除去、または薄くする工程と、前記Si結晶層の表面に酸化処理を施すことにより、前記Si結晶層の表面にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、を含む。

(もっと読む)

半導体素子の製造方法

【課題】垂直型トランジスタの形成時に、ビットライントレンチの形成工程をを単純化することができる半導体素子及びその製造方法を提供する。

【解決手段】垂直型トランジスタの形成のため、ソース/ドレーン領域に用いられる第1垂直型ピラー120と、チャンネルに用いられる第3垂直型ピラー125と、第1ビットラインインプラント領域140と、第3垂直型ピラー125の側壁を取り囲むサラウンドゲート130とで垂直型トランジスタ150を形成した後、ビットライントレンチの形成のためギャップフィル特性に優れたSOC(Spin On Carbon)膜160を形成する。SOC膜160は低温処理が可能であり、垂直型トランジスタ150に加えるストレスを最小化して倒れ問題を防止することができ、高温アニーリング工程で発生する表面の粗化現象がないので、CMP工程を省略することができる。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の製造において、細線化したゲート電極上のシリサイドにおける凝集の防止および当該シリサイドの薄膜化を両立する。

【解決手段】NMOSトランジスタのゲート電極12並びにソース・ドレイン領域15の上部、およびPMOSトランジスタのゲート電極22並びにソース・ドレイン領域25には、それぞれNiシリサイド膜12s,15s,22s,25sが自己整合的に形成されている。Niシリサイド膜12s,15s,22s,25sは、NiおよびSiを主成分とし、化学量論組成がNiSiあるいはNiSi2である。但しそれらはPt,V,Pd,Zr,Hf,Nbのうち1以上の元素を合計で10at%未満の固溶量で含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置のリセスゲート製造方法

【課題】リセスゲート工程中にリセス領域のエッチング工程で尖状のホーン(Horn)が発生することを抑制できる半導体装置のリセスゲート製造方法を提供すること。

【解決手段】シリコン基板21をエッチングし、活性領域を画定するトレンチ22を形成するステップと、該トレンチをギャップフィルする素子分離膜23を形成するステップと、前記活性領域のチャネル予定領域を開口させ、酸化膜と非晶質カーボン膜とが積層されたハードマスク膜を前記シリコン基板上に形成するステップと、前記ハードマスク膜をエッチング障壁(エッチングマスク)として前記チャネル予定領域を1次エッチングおよび2次エッチング(前記2次エッチングは前記非晶質カーボン膜を取除いた後に行う)の順序でエッチングし、デュアルプロファイルを有するリセス領域100を形成するステップとを含む。

(もっと読む)

ジャーマナイド薄膜、ジャーマナイド薄膜の作成方法、ジャーマナイド薄膜を備えたゲルマニウム構造体

【課題】低抵抗かつ熱的安定性に優れた、ジャーマナイド薄膜を提供する。

【解決手段】ゲルマニウム(Ge)基板11上に、Pt薄膜12が形成され、さらにPt薄膜12の上方にNi薄膜13が形成されている。その後、熱処理を加えることによって、Ge基板上にNi、Pt、Geの三元素からなる(Ni1-xPtx)Ge薄膜が形成された。ジャーマナイド薄膜を構成する結晶粒の結晶面方位が、前記ゲルマニウム基板の[110]結晶面に対して、[102]面あるいは[001]面を平行とする配向関係になっている。

(もっと読む)

チャンネルに対して設計されたひずみを与えるストレッサー

【課題】チャネルに対して設計されたひずみを与えるストレッサー及びその形成方法を提供すること。

【解決手段】半導体基板が、異なる不純物濃度を有する異なる部分を有するヘテロエピタキシャル・シリコン含有物質で埋め込まれたリセスを備える。歪まされた膜が、リセスされたソース/ドレイン領域を、傾斜してボトム−アップで埋め込むことができる。膜は、所定の濃度のひずみを引き起こす不純物でリセス側壁をラインし、より低い濃度の不純物でリセスの残りの部分を埋め込む。後者の場合では、側壁ライナーは先細りになりえる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ハイブリッド埋め込みプロセスを用いて、分離性能の高い素子分離構造を得る。

【解決手段】トランジスタ間を分離する素子分離構造13を有する半導体装置1の製造方法であって、素子分離構造13を形成する工程は、基板Wに形成された溝部15の底部に第1の絶縁部32を埋め込む工程と、第1の絶縁部32の上に第2の絶縁部34を埋め込む工程を有し、溝部15の底部に第1の絶縁部32を埋め込む工程は、第1の絶縁部32の材料31を基板Wの表面に成膜する工程と、溝部15の上部から第1の絶縁部32の材料31を除去する工程と、溝部15の上部において、溝部15の内壁に付着していた第1の絶縁部32の材料31の残留層32aを除去する工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド膜上に形成されるシリコン窒化膜の膨れや剥離を抑えることができる半導体装置の製造方法を提供する。

【解決手段】表面にシリサイド膜が形成された領域を有する半導体基板を、酸素元素を含むガス雰囲気中でプラズマ処理してシリサイド膜の上に酸化膜を形成する工程と、その酸化膜を形成した後、半導体基板の表面を覆うシリコン窒化膜を形成する工程と、を備えた。

(もっと読む)

半導体デバイスの製造方法。

【課題】高誘電体膜とシリコン基板とを分離する、極薄かつ緻密な界面層を形成する半導体デバイスの製造方法を提供する。

【解決手段】本発明の半導体デバイスの製造方法は、シリコン基板表面にシリコン酸化膜を形成する工程(酸化膜形成ステップ)と、シリコン酸化膜を所望膜厚だけ残してエッチングする工程(エッチングステップ)と、エッチング後のシリコン酸化膜上に高誘電体膜を形成する工程(高誘電体膜形成ステップ)とを有する。

(もっと読む)

ヘテロ接合型電界効果トランジスタ及びその製造方法

【課題】ヘテロ接合型電界効果トランジスタであって、AlN層や、xが0.6以上であるAlxGa1−xN層を、電子供給層として用いる。

【解決手段】チャネル層40である第1GaN層と、電子供給層50であるAlN層と、キャップ層60である第2GaN層とが順次に積層された積層体30を備えて構成される。また、この発明のヘテロ接合型電界効果トランジスタの他の好適実施形態によれば、チャネル層である第1GaN層と、電子供給層であるAlxGa1−xN層(0.6≦x<1)と、キャップ層である第2GaN層とが順次に積層された積層体を備えて構成される。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

61 - 80 / 148

[ Back to top ]