Fターム[5F140CE10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 同一真空処理 (148)

Fターム[5F140CE10]に分類される特許

41 - 60 / 148

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法と、それを実現する半導体装置の製造装置とを提供する。

【解決手段】半導体装置の製造方法は、半導体層を有する基板上または基板上に形成された導電膜上に、貴金属を含む合金膜を形成する工程(a)と、基板に対して熱処理を行って貴金属とシリコンとを反応させ、基板上または導電膜上に貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応記合金膜を除去する工程(c)と、基板を酸化性雰囲気に曝すことによって、貴金属の残渣の下に位置する部分を含むシリサイド膜の上面上にシリコン酸化膜を形成する工程(d)と、第2の薬液を用いて貴金属の残渣を溶解する工程(e)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、しきい値電圧の低いNチャネルMISトランジスタを有する半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、NチャネルMISトランジスタの製造方法であって、基板に形成されたP型半導体領域上に、シリコン酸化膜とこのシリコン酸化膜上の金属酸化膜とを含むゲート絶縁膜を形成する工程と、基板を熱処理した状態で、水素ラジカルを含むガスにゲート絶縁膜を暴露する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】界面層および高誘電率絶縁膜下層部への窒素原子の導入を抑制することができる半導体装置の製造方法及び基板処理装置の提供。

【解決手段】MOSFETのゲートスタック形成工程は、ウエハ上に界面層を形成するステップと、界面層に第一ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜にアニールを施すことで第一ハフニウムシリケート膜を緻密化もしくは結晶化するステップと、緻密化もしくは結晶化した第一ハフニウムシリケート膜上に第二ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜および第二ハフニウムシリケート膜に対しプラズマ窒化を施すステップと、プラズマ窒化のプラズマダメージを回復する回復アニールステップと、を有する。窒素導入による移動度の劣化を抑制し、良好なMOSFET特性を得ることができる。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

電子デバイス材料の製造方法

【課題】極めて薄い膜厚を有する絶縁膜としてSiO2膜およびSiON膜を用い、電極としてポリシリコン、アモルファスシリコン、SiGeを用いた良好な電気特性を有する電子デバイス(例えば高性能MOS型半導体装置)構造の製造方法を提供する。

【解決手段】酸素、および希ガスを含む処理ガスの存在下で、ウエハW上に平面アンテナ部材SPAを介してマイクロ波を照射することにより、酸素と希ガスとを含むプラズマ(ないし窒素と希ガスとを含むプラズマ、または窒素と希ガスと水素を含むプラズマ)を形成する。このプラズマを用いて前記ウエハ表面に酸化膜2(ないし酸窒化膜2a)を形成し、必要に応じてポリシリコン等の電極13を形成して電子デバイス構造を形成する。

(もっと読む)

半導体装置およびその製造方法、並びにMOS型電界効果トランジスタおよびその製造方法

【課題】III族窒化物系化合物半導体の表面上に酸化物を備えた半導体装置であって、上記III族窒化物系化合物半導体と上記酸化物との間の界面の界面準位密度を小さくでき、移動度を高くできるものを提供すること。

【解決手段】本発明の半導体装置では、III族窒化物系化合物半導体3の表面上に、Alを組成に含みスピネル構造をもつ酸化物4が形成されている。III族窒化物系化合物半導体3は、例えばGaNからなる。酸化物4は、例えばMgAl2O4、MnAl2O4、CoAl2O4、NiAl2O4からなる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜に高誘電率膜を用いたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板の主面上に形成した酸化シリコン(SiO2)膜上に、ハフニウムおよび酸素を含むベース絶縁膜を形成する。次いで、ベース絶縁膜上に、ベース絶縁膜より薄く、かつ、金属元素のみからなる金属薄膜を形成し、その金属薄膜上に、耐湿性および耐酸化性を有する保護膜を形成する。その後、保護膜を有する状態で、ベース絶縁膜に金属薄膜の金属元素をすべて拡散することによって、酸化シリコン膜上に、酸化シリコン膜より厚く、かつ、酸化シリコンより誘電率が高く、ベース絶縁膜のハフニウムおよび酸素と、金属薄膜の金属元素とを含む混合膜(高誘電率膜)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】Geを含有する半導体基板に効果的な洗浄方法が適用された半導体装置の製造方法を提供する。

【解決手段】Geを含有する半導体基板を、HClガス、HBrガスまたはHIガスの少なくとも一種を含むハロゲン化ガスで洗浄処理を行うことを特徴とする半導体装置の製造方法。Geを含有する半導体基板を、75℃以上110℃以下のHCl溶液で洗浄処理を行うことを特徴とする半導体装置の製造方法。例えば、MISFETのゲート絶縁膜の前処理、ソース・ドレイン電極形成の前処理、コンタクトの金属プラグ形成の前処理に適用される。

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】パンチスルーの発生を抑制すると共に、ソース、ドレインの寄生容量を低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】凹部13が形成された半導体基板1と、凹部13の底面上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極5と、ゲート電極5とその直下6とを含む領域の両側の半導体基板1にそれぞれ形成された第1導電型のS/D層7と、半導体基板1に形成された第2導電型のハロー層9と、を備え、S/D層7は、凹部13の直下の領域に形成された低濃度の第1不純物層7aと、凹部13の側面に隣接する領域に形成された高濃度の第2不純物層7bと、を有し、ハロー層9は、第1不純物層7aの直下の領域に形成され、且つ第2不純物層7bの直下の領域には形成されていない。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が高い半導体装置を製造できる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造方法は、基板11上に、シリコン酸化膜12を形成する工程と、シリコン酸化膜12に対して窒素を導入してシリコン酸窒化膜13を形成する工程と、シリコン酸窒化膜13上にZr、Hfの少なくともいずれかを含む絶縁膜14を形成する工程とを含む。基板11上にシリコン酸化膜12を形成する前記工程では、基板11上にシリコン酸化膜12を成膜した後、1050℃以上、1100℃以下でシリコン酸化膜12を熱処理する。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10に形成されたシリコンを主成分とするソース・ドレイン拡散層3上、および半導体基板に形成されソース・ドレイン拡散層に隣接する素子分離絶縁膜の上に、金属を堆積して金属膜を形成し、第1の加熱温度の第1の加熱処理によりソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜106を形成し、シリサイド膜を酸化させないようにして、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜105を形成し、第1の加熱温度よりも高い第2の加熱温度の第2の加熱処理によりシリサイド膜のシリコンの濃度を増加させ、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

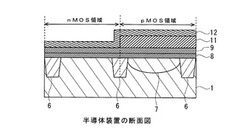

半導体装置

【課題】MISトランジスタにおいて、リーク電流の発生を抑え、チャネル移動度と信頼性とを共に向上させた半導体装置を提供する。

【解決手段】半導体装置は、第1のウエル領域3a及び第2のウエル領域3bと、素子分離領域2に囲まれた第1の活性領域21aと、素子分離領域2、2Bに囲まれた第2の活性領域21bと、第1の活性領域21a上に形成され、凹部内に埋め込まれたSi混晶層からなるソース/ドレイン領域を有する第2導電型の第1のMISトランジスタMP2と、第2の活性領域21b上に形成された第1導電型の第2のMISトランジスタMN2と、第1の活性領域21a上に形成された第2導電型の分離用MISトランジスタDP2とを備える。第1のMISトランジスタのソース/ドレイン領域は、第1の活性領域21aにおけるゲート長方向の端部に位置する素子分離領域2に接していない。

(もっと読む)

41 - 60 / 148

[ Back to top ]