Fターム[5F140CE10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 同一真空処理 (148)

Fターム[5F140CE10]に分類される特許

21 - 40 / 148

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法のうちの一部は、大部分が既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法のうちの一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより一層正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 高誘電体ゲート絶縁膜およびシリコン基板との界面を高品質化して、MISFETの特性向上を図る。

【解決手段】 シリコン基板11上にhigh−k膜21とゲート電極24を形成する半導体装置の製造方法において、high−k膜形成後にフッ素雰囲気でアニール処理23を施し、その後のプロセス温度を600℃以下で行う、半導体装置の製造方法。

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 高誘電率絶縁膜の下地となる金属膜の酸化を抑制し、成膜処理の生産性を向上させる。

【解決手段】 基板を収容した処理室内に原料を供給し排気する工程と、処理室内に第1酸化源を供給し排気する工程と、を交互に繰り返すことで、基板上に第1の高誘電率絶縁膜を形成する工程と、処理室内に原料を供給し排気する工程と、処理室内に第1酸化源とは異なる第2酸化源を供給し排気する工程と、を交互に繰り返すことで、第1の高誘電率絶縁膜上に第2の高誘電率絶縁膜を形成する工程と、を有する。

(もっと読む)

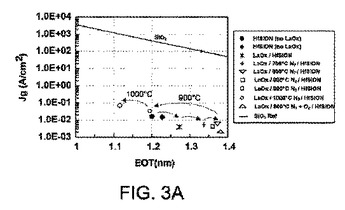

低減された等価酸化膜厚を有する高誘電率ゲートスタックの形成方法

低減された均等酸化物厚さ(EOT)を持つhigh−kゲートスタックを形成する方法を提供し、該方法は:シリコン含有基板を準備し;前記シリコン含有基板上に境界層を形成し、前記境界層が第一の等価酸化物厚さを有し;前記境界層上に第一のhigh−k膜を堆積し;前記第一のhigh−k膜及び前記境界層を、前記第一の等価酸化物厚さと等しいかそれより小さい第二の等価酸化物厚さを持つ変性境界層を形成する温度で熱処理し;及び前記変性境界層上に第二のhigh−k膜を堆積する方法である。ひとつの実施態様によると、前記第一のhigh−k膜がランタン酸化物を含み、前記第二のhigh−k膜がハフニウムシリケートを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】より高い誘電率を有する高誘電率絶縁膜を形成する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板上に高誘電率絶縁膜を形成する工程S106と、前記高誘電率絶縁膜に対し真空下で熱処理を施す工程S110と、熱処理後の前記高誘電率絶縁膜が室温となるまでの間、前記高誘電率絶縁膜が存在する空間の酸素分圧を、前記熱処理時に前記高誘電率絶縁膜が存在する空間の酸素分圧と同等もしくはそれ以下に保持する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体装置の製造方法

【課題】半導体装置の高集積化と供に、メモリ装置のキパシタで容量値の確保のために、酸素欠損のない高誘電率膜を形成する装置の製造方法を提供する。

【解決手段】誘電体膜を形成する工程と、酸化性ガスを供給して誘電体膜に対して酸化処理を行う工程を複数回、断続的に繰り返す熱処理工程と、を有する誘電体膜を備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜内に金属原子を拡散させるための膜の除去を容易にする。

【解決手段】半導体装置の製造方法は、半導体基板上に下地膜を形成する工程と、下地膜上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に金属膜を形成する工程と、窒素ガス及び不活性ガスの少なくとも一方の雰囲気中で半導体基板、下地膜、ゲート絶縁膜及び金属膜を熱処理する工程と、ゲート絶縁膜上に残存する金属膜を除去する工程と、ゲート絶縁膜上に、ゲート電極膜を形成する工程とを備える。

(もっと読む)

21 - 40 / 148

[ Back to top ]