Fターム[5F140CF07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 同時工程 (1,387) | SD拡散領域とゲート電極への拡散・注入 (182)

Fターム[5F140CF07]に分類される特許

81 - 100 / 182

半導体装置

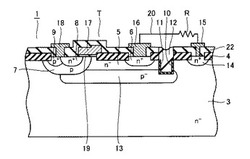

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域3には、ドレイン領域となるn-拡散領域5が形成され、そのn-拡散領域5の一方の側には、p拡散領域7と、ソース領域となるn+拡散領域8が形成されている。n-拡散領域5の他方の側には溝部10が形成されて、絶縁体12が充填されている。n-拡散領域5の直下には、p-埋め込み層13が形成されている。n-型半導体領域3の領域には、高電位が印加されるn+拡散領域14が形成され、抵抗Rを有する配線20によってn-拡散領域5と電気的に接続されている。n+拡散領域8とn-拡散領域5とによって挟まれたp拡散領域7の部分の表面上には、ゲート絶縁膜19を介在させてゲート電極17が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程におけるプラズマによる電荷の蓄積に起因するゲート絶縁膜の破壊を防ぐとともに、素子の面積の増大を抑制する。

【解決手段】アクティブ領域22が設定されている半導体基板20の、アクティブ領域に設定されたトランジスタ形成領域24にMOS型電界効果トランジスタが形成されている。MOS型電界効果トランジスタの制御電極40は、第1導電型の電極部42、45及び48と、第2導電型の電極部46と、第1導電型の電極部及び第2導電型の電極部の間にpn接合49とを有している。第1導電型の電極部は、アクティブ領域から素子分離領域にわたって形成されている。第2導電型の電極部は、素子分離領域に形成されていて、アクティブ領域の半導体基板に、電気的に接続されている。

(もっと読む)

電界効果型半導体装置及びその製造方法

【課題】 電界効果型半導体装置及びその製造方法に関し、ゲート絶縁膜にダメージを与えることなく、少なくとも窒素を含有するとともにシリコンを主成分とする膜を組成制御性良く構成する。

【解決手段】 シリコンと、シリコンに対して5〜30原子数%の窒素を含有する導電膜をゲート電極3の少なくとも一部として用いる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極からの不純物の拡散を十分に抑制しつつ、良好な特性を示すゲート絶縁膜を得ることができる半導体装置の製造方法を提供する。

【解決手段】Si基板の表面に、素子分離絶縁膜、nウェル及びpウェルを形成した後、前処理として、Si基板の洗浄を行う(ステップS1)。その後、下地酸化として、Si基板の表面をRTO法により熱酸化することにより、シリコン酸化膜を形成する(ステップS2)。続いて、シリコン酸化膜に対してプラズマ窒化を行う(ステップS3)。このプラズマ窒化の結果、活性窒素の導入によりシリコン酸化膜が窒化され、シリコン酸窒化膜が得られる。次に、アンモニア雰囲気中でアニールを行う(ステップS4)。この結果、シリコン酸窒化膜中の表面近傍に、更に窒素が導入される。次いで、後アニール(ポストアニール)として、窒素及び酸素を含有する雰囲気中でアニールを行う(ステップS5)。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制しながら高駆動能力を確保すると共に、特性が異なる複数の素子の特性を確保し且つ製造工程の省略が可能な半導体装置及びその製造方法を提供する。

【課題手段】半導体装置は、半導体基板1の第1領域A上に形成された第1ゲート電極3と、第1領域Aにおける少なくとも第1ゲート電極3の両側下部の部分に形成された第1不純物層5と、第1ゲート電極3の両側面に形成された第1サイドウォール6と、半導体基板1における第1ゲート電極3から見て第1サイドウォール6の両側に形成された第2不純物層7とを備える。第1不純物層5は、第1導電型の第1不純物と、第1導電型で且つ第1不純物よりも質量数の大きい第2不純物とを含む。

(もっと読む)

半導体装置

【課題】ゲート電極に電圧が印加されないときにも、ゲート電極とドレイン領域との間の電界を緩和し、ゲート絶縁膜に電界集中が発生するのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置100は、互いに所定の間隔を隔てて形成されたソース領域7およびドレイン領域9と、ソース領域7に接するように形成され、チャネル領域5aを含むボディ領域5と、電界緩和層3と、ボディ領域5と電界緩和層3との表面上に形成されたゲート絶縁膜13と、ゲート絶縁膜13の表面上に形成され、不純物領域14と不純物領域15とが接触するように形成されたポリシリコン層32を含むゲート電極16とを備えている。そして、不純物領域15は、ゲート電極16のドレイン領域9側に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネリングの発生と製造工程の増加とを防ぐことができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極106及び第1,第2のソース/ドレイン領域119A,119Bの上部が非晶質化シリコン層110となっている。これにより、上記第1,第2のソース/ドレイン領域119A,119Bを形成するための不純物の注入を行っても、非晶質化シリコン層110がその不純物の障壁となるので、チャネリングの発生を防ぐことができる。また、上記非晶質化シリコン層110は除去しなくてもよいので、製造工程の増加も生じない。

(もっと読む)

半導体装置の製造方法

【課題】 ソース/ドレインの横方向拡散を確実に抑止し、更なる微細化及び高性能化の要請を満たし、信頼性の高い半導体装置を実現する。

【解決手段】 ゲート電極2をマスクとしたイオン注入によりエクステンション領域3を形成した後、ゲート電極2及び第1のサイドウォール4をマスクとして、ソース/ドレイン5の不純物の拡散抑制機能を有する物質をイオン注入し、半導体基板1の表層のサイドウォール4に整合する部位を非晶質化してアモルファス状態の拡散抑制領域6を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明では、酸素欠損を低減させ、信頼性を改善した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】第1の発明の半導体装置は、基板と、基板に形成された半導体領域と、半導体領域上に形成され、1種以上の第1金属元素の酸化物で形成された絶縁膜と、絶縁膜上に形成され、酸化物の生成自由エネルギーについて第1金属元素よりも大でありかつ金属状態である第2金属元素、および第1金属元素の酸化物で形成された遷移層と、遷移層上に形成された電極と、電極をゲート長方向に挟む半導体領域に形成されたソース・ドレイン領域とを備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】SiGeによる高移動度の恩恵を十分に受けながら、実効ゲート長の広がりを抑制できるようにした半導体装置の製造方法を提供する。

【解決手段】歪SiGeトランジスタ、を有する半導体装置の製造方法であって、シリコン基板1上にSiGe層5を形成する工程と、SiGe層5上にゲート酸化膜7を形成する工程と、ゲート酸化膜7上にゲート電極8を形成する工程と、ゲート電極8をマスクにシリコン基板1に向けてBF2+イオンを斜めにイオン注入することによって、ゲート電極8の両側下から当該ゲート電極8直下にかけてのSiGe層5にP−領域9を形成する工程と、P−領域9を形成した後でゲート電極8の側面にサイドウォール10を形成する工程と、ゲート電極8およびサイドウォール10の両方をマスクにシリコン基板1に向けてBF2+イオンをイオン注入することによって、シリコン基板1上にP+領域11を形成する工程と、を含む。

(もっと読む)

絶縁膜、およびそれを用いた半導体装置

【課題】リーク特性等の特性が優れた高誘電体絶縁膜を提供する。

【解決手段】本発明の絶縁膜は、第1の金属と酸素からなる金属酸化物にフッ素を導入した絶縁膜であって、窒素或いは前記金属酸化物をなす第1の金属の価数よりも小さな価数の第2の金属を少なくとも1つ、前記フッ素と同時に導入したことを特徴とし、窒素または前記第2の金属の量を[X]、フッ素の量を[F]と表わすとき、{[X]−[F]}/2≦8.4atomic%であることを特徴とする。

(もっと読む)

固体撮像素子及びその製造方法、並びに半導体装置及びその製造方法

【課題】p型不純物領域の活性化を低温で行うことを可能にする固体撮像素子の製造方法を提供する。

【解決手段】光電変換が行われる受光センサ部が半導体基体内に形成され、この半導体基体の表面側に配線層又は電極層が形成され、半導体基体に、表面側とは反対の裏面側から光を入射させる裏面照射型構造を有する固体撮像素子を製造する際に、半導体基体の裏面側の部分をアモルファス化してアモルファス半導体層62を形成する工程と、半導体基体の裏面側へp型不純物をイオン注入63する工程とを、それぞれ行い、その後に、レーザーアニール65によってp型不純物を活性化させることにより、半導体基体の裏面側にp型半導体領域31を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上述した積み上げソース/ドレイン構造とブースター技術とを両立させることが可能で、これによりキャリア移動度を向上させた素子構造の微細化を図ることができ、これにより更なる高機能化を達成することが可能な半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板1上にゲート絶縁膜3を介して設けられたゲート電極4aと、ゲート電極4aの側壁に形成された絶縁性のオフセットスペーサ6と、オフセットスペーサ6との間に間隔を保った状態でシリコン基板11の表面側に設けられた掘り込みパターンa内にエピタキシャル成長によって形成された化合物半導体層11と、オフセットスペーサ6によってゲート電極4aと絶縁された状態でシリコン基板1上および化合物半導体層11上にエピタキシャル成長によって積上げ形成されたシリコン層13とを備えたことを特徴とする半導体装置Tr1。

(もっと読む)

半導体装置の製造方法

【課題】高信頼性を有するゲート絶縁膜を形成可能な半導体装置の製造方法を提供する。

【解決手段】シャロートレンチアイソレーション方式の素子分離構造を有する半導体装置の製造方法であって、シリコン基板11の表面に溝14を形成した後に、溝14の内表面14aを洗浄して汚染物を除去し、次いで、溝14の内表面14aの欠陥層15を除去する。欠陥層15の除去は、200℃以下の基板温度でフッ素元素含有ガスおよび酸素ガスを電離させて発生したラジカルによる等方性エッチングにより溝14の内表面14aを5nm程度エッチングする。

(もっと読む)

半導体装置および半導体装置の製造方法および携帯電子機器

【課題】キンク効果を抑制できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】シリコン基板101に形成された素子分離領域102とその素子分離領域102以外の領域との境界を跨ぐように、シリコン基板101上にゲート絶縁膜103を介してゲート電極104が形成されたMOSトランジスタを備える。上記素子分離領域102とその素子分離領域102以外の領域との境界の段差領域120におけるゲート絶縁膜103の膜厚を、その段差領域120以外の領域におけるゲート絶縁膜103の膜厚に対して65%〜100%とする。

(もっと読む)

極薄先端を有する新規のトランジスタおよびその製造方法

【課題】低抵抗極薄先端領域を有する新規のトランジスタおよびVLSI生産可能製造方法を提供する。

【解決手段】第1のドープ半導体材料を前記半導体基板上に前記第1の側壁スペーサの外縁に整合して形成し、ドーパントを前記半導体材料から前記基板中に前記側壁スペーサの第1の対の下に拡散させて、一対の先端領域を形成し、側壁スペーサの第2の対を前記第1の半導体基板上に前記側壁スペーサの第1の対の外縁に整合して形成し、ソース/ドレイン・コンタクト領域を形成するために、イオンを前記半導体材料中および前記基板中に前記側壁スペーサの第2の対の外縁に整合させて注入する。

(もっと読む)

半導体装置およびその製造方法

【課題】熱処理に伴うゲート電極のシート抵抗値の上昇と、接合破壊により生じる接合リーク電流値上昇を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1と、半導体基板1上にゲート絶縁膜3を介して形成されるゲート電極4と、ゲート電極4を挟んで半導体基板1の表面に形成される一対の第2の不純物拡散層7と、ゲート電極4の上部、および、第2の不純物拡散層7の上部に形成されるNi(ニッケル)シリサイド10とを備え、ゲート電極4の上部、および、第2の不純物拡散層7は、B(ボロン)と、Bよりも大きい原子半径を有し、かつ、Bと同じ導電型の不純物であるIn(インジウム)とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】DMOSトランジスタを有する半導体装置において、ゲート・ドレイン間容量を小さくする。

【解決手段】半導体層20に形成され、それぞれがボディ領域として機能し、互いに離間している複数の第2導電型不純物領域22と、複数の第2導電型領域22それぞれの一部に形成され、ソース又はドレインとして機能する第1導電型不純物領域25と、半導体層20と第1導電型不純物領域25の間に位置する第2導電型不純物領域22上、及び複数の第2導電型不純物領域22の相互間に位置する半導体層20上に形成されたゲート絶縁膜23と、ゲート絶縁膜23上に形成され、ゲート電極として機能する、不純物が導入された半導体層24とを具備する。半導体層24は、複数の第2導電型領域22の相互間の上方に、不純物が導入されていないノンドープ領域24aを有する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの閾値電圧のばらつきを小さくすることができる半導体装置の製造方法を提供する。

【解決手段】面方位が(100)であるシリコンウェハ1に対して、シリコンウェハ1に対して垂直な軸から7°傾けた方向であり、かつシリコンウェハ1の中心を回転軸とした場合にノッチ又はオリフラの中心から27°回転させた方向から、注入深さが0.5〜1μmとなるように不純物イオンを注入することにより、素子領域にウェル10を形成する。ウェル10を形成するときのイオン注入角度を適切な範囲に設定しているため、注入された不純物の濃度分布のばらつきが抑制される。このため、熱拡散後のウェル10における不純物の濃度分布もばらつきが抑制され、トランジスタの閾値電圧のばらつきが抑制される。

(もっと読む)

81 - 100 / 182

[ Back to top ]