Fターム[5F152CC08]の内容

再結晶化技術 (53,633) | 基板 (3,980) | 材料(結晶化直前の状態) (3,902) | 半導体 (685) | Si (483)

Fターム[5F152CC08]に分類される特許

81 - 100 / 483

半導体装置およびその作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことにより、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体基板の製造方法および半導体基板製造装置

【課題】半導体に注入された不純物を活性化するとともに該活性化によって表面性状を一様なものにして撮像素子などとして使用する際に、良好な特性を得る。

【解決手段】半導体にレーザを照射して半導体に注入された不純物を活性化する半導体基板の製造方法において、前記不純物が活性化される第1のエネルギー密度によって前記半導体に第1のレーザを照射した後、前記第1のエネルギー密度よりも低い第2のエネルギー密度によって前記半導体の前記第1のレーザ照射面上に第2のレーザを照射するので、第1のレーザ照射でレーザアニールすることによって充分な活性化を安定して行い、さらに第2のレーザ照射でレーザアニールすることで、第1のレーザ照射で生じた不規則な表面荒れを一様な荒れにする。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面上の結晶領域を有する酸化物半導体層と、前記酸化物半導体層と接するソース電極層およびドレイン電極層と、前記酸化物半導体層、前記ソース電極層、および前記ドレイン電極層を覆うゲート絶縁層と、前記ゲート絶縁層上の、前記結晶領域と重畳する領域のゲート電極層と、を有し、前記結晶領域は、前記酸化物半導体層の表面と略垂直な方向にc軸が配向する結晶を有する領域である半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の結晶性を有する酸化物半導体膜及び第2の結晶性を有する酸化物半導体膜が積層された酸化物半導体積層体を有する縦型トランジスタ及び縦型ダイオードである。当該酸化物半導体積層体は、結晶成長の工程において、酸化物半導体積層体に含まれる電子供与体(ドナー)となる不純物が除去されるため、酸化物半導体積層体は、高純度化され、キャリア密度が低く、真性または実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい。

(もっと読む)

SOI基板の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、単結晶半導体層の膜厚の厚いSOI基板を提供することを課題の一とする。その際に、予めシード層となる単結晶半導体層の結晶欠陥を修復しなくとも、良好にエピタキシャル成長が進む方法を提供することを課題の一とする。また、シード層の結晶欠陥を修復する工程を別に設けなくとも、固相エピタキシャル成長によりシード層である単結晶半導体層の結晶性が回復したSOI基板を提供することを課題の一とする。

【解決手段】絶縁層を介して基板に設けられた第1単結晶半導体層上に、非晶質半導体層を形成する。非晶質半導体層は、成膜温度100℃以上275℃以下、シラン系ガスを希釈しないで用いるCVD法により形成する。熱処理を行って、非晶質半導体層を固相エピタキシャル成長させて、単結晶半導体層の膜厚の厚いSOI基板を作製する。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の酸化物半導体層を用いた新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上の、第1の酸化物半導体層の表面から内部に向かって成長させた結晶領域を有する第1の酸化物半導体層と、第1の酸化物半導体層上の第2の酸化物半導体層と、第2の酸化物半導体層と接するソース電極層およびドレイン電極層と、第2の酸化物半導体層、ソース電極層、およびドレイン電極層を覆うゲート絶縁層と、ゲート絶縁層上の、第2の酸化物半導体層と重畳する領域のゲート電極層と、を有し、第2の酸化物半導体層は、結晶領域から成長させた結晶を有する層である半導体装置である。

(もっと読む)

カラーディスプレイ用TFTパネルおよびその製造方法

【課題】低温プロセスにおいて重複走査領域が発生する場合であっても、デバイス特性にばらつきの少ないTFTパネルを提供すること。

【解決手段】薄膜トランジスタが列状に配列され、かつ互いに平行な複数の制御領域が連続して並んだ基板と、前記基板上に配置された平坦化膜とを有するTFTパネルであって、前記制御領域には、最大結晶粒径が大きい半導体層からなるチャネルを有する薄膜トランジスタXが列状に配列された制御領域Xと、最大結晶粒径が小さい半導体層からなるチャネルを有する薄膜トランジスタYが列状に配列された制御領域Yと、が含まれ、前記制御領域X同士の中心間距離は、前記制御領域の短軸の3n[nは1以上の整数]倍である、カラーディスプレイ用TFTパネル。

(もっと読む)

結晶化膜の製造方法及び結晶化装置

【課題】基板上に形成されたアモルファス膜の結晶化を、基板表面に対して垂直方向(即ち下から上方向)ではなく略平行方向(即ち横方向)に進行させる結晶化膜の製造方法を提供する。

【解決手段】本発明の一態様は、基板上にアモルファス膜1を形成し、前記アモルファス膜1にレーザ光を照射してレーザ光照射領域1aを結晶化し、前記アモルファス膜1に熱処理を施すことにより、前記レーザ光照射領域以外のアモルファス膜1を結晶化することを特徴とする。

(もっと読む)

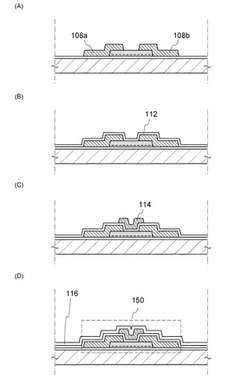

薄膜トランジスタ

【課題】イオン注入を行わずに低コストで製造できる構造形態を備えた薄膜トランジスタを提供する。

【解決手段】基板10上(又は第1下地膜11乃至第2下地膜12上)に設けられたポリシリコン半導体膜13と、ポリシリコン半導体膜13上に離間して設けられたソース電極15s及びドレイン電極15dと、ポリシリコン半導体膜13上にゲート絶縁膜14を介して設けられたゲート電極15gとを少なくとも有する。ポリシリコン半導体膜13は、面内方向にソース電極接続領域13s、チャネル領域13c及びドレイン電極接続領域13dを有し、チャネル領域13cにはドーパントが含まれておらず、ソース電極接続領域13s及びドレイン電極接続領域13dは基板10側からソース電極側及びドレイン電極側に向かってドーパント一定濃度層21とドーパント減少傾斜層22’とを有する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供することを目的の一とする。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、および、半導体材料の酸化の速度および酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が選択的に除去されるエッチング処理と、損傷半導体領域が選択的に除去されるエッチング処理の後に、半導体基板の表面に研磨を行う半導体基板の再生方法である。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】多孔質ゲート絶縁層を設けることにより基板に発生する熱応力を低減し、基板の割れを防止することが可能な半導体デバイスおよびその製造方法を提供すること。

【解決手段】基板上に形成されたゲート電極およびゲート絶縁層上にソース電極及びドレイン電極並びに電極間を接続する半導体層を有し、ゲート絶縁層を挟んでゲート電極と反対側にソース電極、ドレイン電極とが配置された半導体素子において、多孔質ゲート絶縁層を設けることにより基板に発生する熱応力を低減し、基板の割れを防止する。

(もっと読む)

多結晶シリコン形成装置及びその方法

【課題】工程の生産性を向上させることができる多結晶シリコン形成装置を開示する。

【解決手段】本発明に係る装置は、基板上に形成した非晶質シリコンを熱処理して多結晶シリコンを形成する装置であって、非晶質シリコンを予熱する予熱部200と、予熱部200で予熱された非晶質シリコンを結晶化熱処理する熱処理部300とを備えていることを特徴とする。予熱部200での基板の予熱は、基板が基板ホルダから離間した状態で行われ、熱処理部300での基板の熱処理は、基板が基板ホルダ上に載置した状態で行われる。

(もっと読む)

半導体装置の作製方法

【課題】絶縁基板上に第1の単結晶半導体膜と、該第1の単結晶半導体膜上に第2の単結晶半導体膜を有する半導体装置の作製する方法を提供する。

【解決手段】第1の単結晶半導体基板に第1のイオンをドープして第1の脆化層を形成する工程と、第2の単結晶半導体基板に第2のイオンをドープして第2の脆化層を形成する工程と、第1の単結晶半導体基板と第2の単結晶半導体基板とを貼り合わせる工程と、第1の加熱処理により、第2の単結晶半導体基板上に第1の単結晶半導体膜を形成する工程と、第1の単結晶半導体膜上に絶縁基板を貼り合わせる工程と、第2の加熱処理により、絶縁基板上に、第1の単結晶半導体膜及び第2の単結晶半導体膜を形成する工程と、を有し、第1のイオンのドーズ量は第2のイオンのドーズ量よりも多く、第1の加熱処理の温度は第2の加熱処理を温度よりも低い。

(もっと読む)

シリコン層の製造方法

本発明は、一般式SiaH2a+2(式中、a=3〜10)の少なくとも1種のヒドリドシランから製造可能な少なくとも1種の高級シランを基板上に塗布し、引き続き熱的に、主にシリコンからなる層に変換し、その際、この高級シランの熱的変換は500〜900℃の温度でかつ≦5分の変換時間で行う、基板上にシリコン層を熱的に製造する液相法、前記方法により製造可能なシリコン層及びその使用に関する。 (もっと読む)

半導体装置の作製方法

【課題】基板処理の効率を高めることができ、また半導体膜の移動度を高めることができるレーザー結晶化法を用いた半導体製造装置を提供する。

【解決手段】半導体膜を成膜する成膜装置と、レーザー装置とを備えたマルチチャンバー方式の半導体製造装置であり、レーザー装置は、被処理物に対するレーザー光の照射位置を制御する第1の手段と、レーザー光を発振する第2の手段(レーザー発振装置1213)と、前記レーザー光を加工または集光する第3の手段(光学系1214)と、前記第2の手段の発振を制御し、なおかつ第3の手段によって加工されたレーザー光のビームスポットがマスクの形状のデータ(パターン情報)に従って定められる位置を覆うように前記第1の手段を制御する第4の手段とを有する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供することを目的の一とする。または、半導体基板の再生に適した方法を用いて再生半導体基板を作製することを目的の一とする。または、当該再生半導体基板を用いてSOI基板を作製することを目的の一とする。

【解決手段】損傷した半導体領域と絶縁層とを含む段差部が周縁部に存在する半導体基板に対し、前記絶縁層が除去されるエッチング処理と、前記半導体基板を構成する半導体材料を酸化する物質、前記酸化された半導体材料を溶解する物質、および、前記半導体材料の酸化の速度および前記酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して前記損傷半導体領域が選択的に除去されるエッチング処理と、水素を含む雰囲気中で熱処理と、を行うことで半導体基板を再生する。

(もっと読む)

酸化物半導体膜、および半導体装置

【課題】半導体装置に用いるのに好適な新たな構造の酸化物半導体膜を提供することを目的の一とする。または、新たな構造の酸化物半導体膜を用いた半導体装置を提供することを目的の一とする。

【解決手段】非晶質を主たる構成とする非晶質領域と、表面近傍の、In2Ga2ZnO7の結晶粒を含む結晶領域と、を有し、結晶粒は、そのc軸が、表面に対して略垂直な方向となるように配向している酸化物半導体膜である。または、このような酸化物半導体膜を用いた半導体装置である。

(もっと読む)

シリコン薄膜の処理方法およびフラッシュランプ照射装置

【課題】基板とアモルファスシリコン薄膜との間に部分的に金属層が配置されていても、結晶粒径が均一でクラックのないポリシリコン薄膜を得ることができるシリコン薄膜の処理方法およびこの方法に用いられるフラッシュランプ照射装置を提供する。

【解決手段】点灯時のパルス幅が50〜200μsecのフラッシュランプからの光を、基板上に部分的に配置された金属層を介して形成された厚みが30〜100nmのアモルファスシリコン薄膜に照射して、ポリシリコン薄膜を形成するシリコン薄膜の処理方法において、長波長側の光をカットする波長カットフィルタを介して、フラッシュランプからの光をアモルファスシリコン薄膜に照射する工程を有し、波長カットフィルタによってカットされる光の波長領域の短波長側端の波長が650nm以下、アモルファスシリコン薄膜に照射される光の照射エネルギーが2.00〜3.10J/cm2 である。

(もっと読む)

非周期的なパルスによる部分的溶解膜処理のシステムおよび方法

一態様において、本開示は薄膜処理方法に関する。本方法は、第1の選択された方向に薄膜を進める間、第1レーザパルスと第2レーザパルスで薄膜の第1領域を照射し、各レーザパルスは成形ビームを供給し、薄膜を部分的に溶解するのに十分なフルエンスを持ち、第1領域は再凝固および結晶化して第1の結晶化領域を形成する。更に本方法は、第3レーザパルスと第4レーザパルスで薄膜の第2領域を照射し、各レーザパルスは形成ビームを供給し、薄膜を部分的に溶解するのに十分なフルエンスを持ち、第2領域は再凝固および結晶化して第2の結晶化領域を形成する。第1レーザパルスと第2レーザパルス間の時間間隔は、第1レーザパルスと第3レーザパルス間の時間間隔の半分未満である。 (もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)とボンド基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。または、上記荒れを抑えて半導体装置の歩留まりを向上することを目的の一とする。

【解決手段】ボンド基板にイオンを添加して該ボンド基板に脆化領域を形成し、ベース基板にレーザー光の照射による複数の凹凸部を形成し、絶縁層を介してボンド基板とベース基板とを貼り合わせる際に、複数の凹凸部をボンド基板とベース基板との位置合わせの指標として用いると共に、複数の凹凸部の一を含む領域に、ボンド基板とベース基板とが貼り合わない領域であってその外周が閉じられた領域を形成し、熱処理を施すことにより、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成する。

(もっと読む)

81 - 100 / 483

[ Back to top ]