Fターム[5F152CE12]の内容

Fターム[5F152CE12]の下位に属するFターム

Fターム[5F152CE12]に分類される特許

121 - 140 / 390

半導体装置の作製方法、半導体装置及び電子機器

【課題】製造コストを低減しつつ、高速動作が可能な回路を有する半導体装置の作製方法を提供することを課題の一とする。または、該半導体装置を提供するための半導体基板の作製方法を提供することを課題の一とする。または、該半導体装置を用いた電子機器を提供することを課題の一とする。

【解決手段】基板上に非単結晶半導体層を形成した後、非単結晶半導体層の一部の領域上に単結晶半導体層を形成する。これにより、非単結晶半導体層を用いて大面積が必要とされる領域(例えば、表示装置における画素領域)の半導体素子を形成し、単結晶半導体層を用いて高速動作が求められる領域(例えば、表示装置における駆動回路領域)の半導体素子を形成することができる。

(もっと読む)

半導体結晶薄膜の作製方法および装置

【課題】アモルファスシリコン薄膜を熱吸収層を用いて加熱結晶化するとともに、熱吸収層を汚染なく簡易方法によって除去でき、さらに結晶の欠陥を効率よく低減する。

【解決手段】基板2上に形成されたアモルファス半導体薄膜(a−シリコン膜1)を結晶化させる際に、前記アモルファス半導体薄膜の結晶化させたい箇所の表面にのみ予め熱吸収層3を設け、エネルギー照射することで前記アモルファス半導体薄膜を結晶化し、その後、ドライプロセスにより改質物質(水素など)を添加して、前記熱吸収層3を脆化させて半導体薄膜上から除去するとともに結晶化された前記半導体薄膜(p−シリコン膜1a)の欠陥低減を同時に行う。

(もっと読む)

ディスプレーデバイス用半導体装置の製造方法

【課題】 ディスプレーデバイス用半導体装置の製造方法において、ガラス基板に熱的に損傷を与えないで、炭酸ガスレーザーによりSiを熱処理する。

【解決手段】 上下のSiO2膜2、3に挟まれた多結晶Si又は非晶質Si層1からなるサンドイッチ構造30とガラス基板6の間に反射金属膜4を配置する。炭酸ガスレーザーを上側SiO2膜からガラス基板6に向かって照射することにより多結晶もしくは非晶質Si層を熱処理し、その後、RGB配置領域20からサンドイッチ構造30及び反射金属膜4を除去する。

(もっと読む)

多結晶半導体膜の形成方法、薄膜トランジスタ、および薄膜トランジスタの製造方法

【課題】 隣り合う2つのTFTの間に短絡が発生するのを確実に防止するとともに、回路設計の自由度を増大させることができる多結晶半導体膜の形成方法。

【解決手段】 絶縁基板上において第1方向に沿って結晶成長した多結晶半導体膜を形成する本発明の方法では、第1方向に沿って第1の向きに結晶成長した結晶粒(15a)と第1の向きとは逆の第2の向きに結晶成長した結晶粒(15b)とが、第1方向と直交する第2方向に沿って鋸歯状または正弦波状に衝突するように、絶縁基板上における結晶成長を制御する。

(もっと読む)

結晶シリコンアレイ、および薄膜トランジスタの製造方法

【課題】 1つの結晶粒内に複数の薄膜トランジスタを配置することのできるような大粒径の結晶を含む結晶シリコンアレイ。

【解決手段】 非晶質シリコン薄膜を結晶化して得られる結晶シリコンアレイの結晶化単位領域(U)は、7μm角以上の正方形領域を内包する大きさを有する二次元結晶部(21)と、主成長方向(F1)に間隔を隔てた一対の二次元結晶部の間に形成されて主成長方向に沿って0.2μm以上の長さを有する微結晶部(22)と、3.5μm以上の粒長を有する針状結晶部(23)とを含む。二次元結晶部は、1つの結晶核からの成長により形成され、結晶の主成長方向を有する。針状結晶部は、一対の二次元結晶部の間において主成長方向と直交する方向に沿った成長により形成されている。

(もっと読む)

半導体薄膜、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに、半導体薄膜の製造装置

【課題】信頼性向上、歩留まり向上が可能で、かつ品質向上につながる半導体薄膜の製造方法を提供すること。

【解決手段】本発明に係る半導体薄膜の製造方法は、基板上に非晶質の半導体薄膜を形成する工程(step1)と、自然酸化膜を除去する工程(Step2)と、紫外線照射によって生成するオゾン又は/及び酸素ラジカルにより表面酸化処理を行う工程(Step3)と、結晶粒界が略等間隔で、かつ格子状の周期構造を有する多結晶化された半導体薄膜を得るレーザーアニール工程(Step4)とを備え、レーザーアニール工程において、表面酸化処理を行う工程を経ずに、自然酸化膜を除去する工程後、直ちにレーザーアニールを行うことにより多結晶化された半導体薄膜を得る場合のレーザー光の最適エネルギー密度に対して、所定のエネルギー密度だけ低いエネルギー密度にてレーザー光照射を行う。

(もっと読む)

半導体基板、及びその製造方法

【課題】DSB基板を用いてHOT構造の半導体基板を作製するに際し、その機能性基板の、互いに異なる結晶方位を有する結晶領域の境界における結晶欠陥の発生を抑制し、本来的な実用に足る前記HOT構造の半導体基板を提供する。

【解決手段】第1の結晶方位を有するシリコン支持基板と、このシリコン支持基板上に直接的に形成され、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第1の結晶領域と、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第2の結晶領域とを有するシリコン機能性基板とを具えた半導体基板において、前記シリコン機能性基板の、前記第1の結晶領域及び前記第2の結晶領域の境界に、少なくとも前記シリコン支持基板の主面にまで達するような溝部を形成する。

(もっと読む)

半導体薄膜の結晶化方法、薄膜半導体装置の製造方法及び液晶表示装置の製造方法

【課題】結晶化するためのエネルギー線のエネルギー量のばらつきが不規則に発生しても比較的安定した大きさの結晶化領域や良質の2次元結晶を得ることの可能な半導体薄膜の結晶化方法、良好な特性を有する薄膜半導体装置の製造方法及び液晶表示装置の製造方法を提供すること。

【解決手段】非単結晶半導体薄膜に周期的な強度分布を有するパルスエネルギー線を照射して、前記半導体薄膜の照射された部分を溶解し、前記パルスエネルギー線の遮断後凝固させることにより、前記パルスエネルギー線照射領域内のエネルギー強度が極小である付近に発生する結晶核から放射状に結晶を成長させて2次元結晶化領域を形成する半導体薄膜の結晶化方法であって、前記パルスエネルギー線の照射は、前記半導体薄膜の第1の照射位置に第1のエネルギー線を照射する第1の照射工程と、前記第1の照射位置からずらし、少なくとも前記結晶核を含む第2の照射位置に第2のエネルギー線を照射する第2の照射工程とを含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】単結晶シリコン層でのキャリアの蓄積を防止することが可能な半導体装置を提供する。

【解決手段】単結晶シリコン基板11と、単結晶シリコン基板上に部分的に形成された絶縁層12と、単結晶シリコン基板上及び絶縁層上に形成され、過剰な4族元素に基づく欠陥層を含んだ単結晶シリコン層14と、単結晶シリコン層上に形成された第1のゲート絶縁膜16と、第1のゲート絶縁膜上に形成された電荷蓄積層17と、電荷蓄積層上に形成された第2のゲート絶縁膜19と、第2のゲート絶縁膜上に形成された制御ゲート電極22とを含むメモリセル用の複数の第1のゲート構造31とを備える。

(もっと読む)

表示装置および表示装置の製造方法

【課題】簡単な構成で、且つ若干の工程数の増加のみで、オフ電流の低減を図ったポリシリコン薄膜トランジスタを備える表示装置を提供する。

【解決手段】絶縁基板と、前記絶縁基板上に形成された薄膜トランジスタとを有する表示装置であって、前記薄膜トランジスタの半導体層は、多結晶シリコン層と、前記多結晶シリコン層の上層に形成された第1の非晶質シリコン層と、前記第1の非晶質シリコン層の上層に形成された第2の非晶質シリコン層とを有する。

(もっと読む)

光照射装置、結晶化装置、結晶化方法、およびデバイス

【課題】 デフォーカスの影響をほとんど受けることなく、所望のディップ状の光強度分布を所望の位置に安定的に形成することのできる結晶化装置。

【解決手段】 180度と実質的に異なる位相差の位相段差を有し、入射光を位相変調する光変調素子(1)と、光変調素子を照明する照明系(2)と、光変調素子により位相変調された光に基づいて所定の光強度分布を所定面に形成する結像光学系(3)と、結像光学系の瞳位置に配置されて第1領域を通過する第1光束と第2領域を通過する第2光束とを互いに非干渉性にする空間フィルター(6)とを備えている。

(もっと読む)

結晶化装置、結晶化方法、およびデバイス

【課題】 簡素な構成にしたがって光学系の大型化を招くことなく、非単結晶半導体膜上での干渉縞の発生を良好に抑えることのできる結晶化装置。

【解決手段】 所定の光強度分布を有する光を非単結晶半導体膜に照射して結晶化半導体膜を生成する結晶化装置。所定方向(y方向)に沿って配列された複数のシリンドリカルレンズ要素(23ba)を有するホモジナイザを介して光変調素子を照明する照明系と、光変調素子を介した光に基づいて所定の光強度分布を形成する結像光学系と、複数のシリンドリカルレンズ要素に対して1個おきに設けられた複数の短冊状の光学部材(25)とを備えている。

(もっと読む)

半導体装置、表示装置及びその製造方法

【課題】閾値電圧などのばらつきを低減させることができ、信頼性の高い高性能なTFT特性を持つ半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、基板上に形成され、ソース領域4c、ドレイン領域4d及びチャネル領域4bを有する多結晶半導体層4aと、多結晶半導体層4aのソース領域4c及びドレイン領域4d上に形成された金属性導電層6と、多結晶半導体層4aと金属性導電層6との間に形成された合金層5とを有し、多結晶半導体層4aは、チャネル領域4bの膜厚が、金属性導電層6が形成された領域の膜厚より薄くなるように形成された凹部4eを有し、凹部4eの深さXと、合金層5の膜厚Yと、金属性導電層6の膜厚tとが、次の関係を満たしている。

0.1t≦Y≦0.3t

0.3Y≦X≦2Y

(もっと読む)

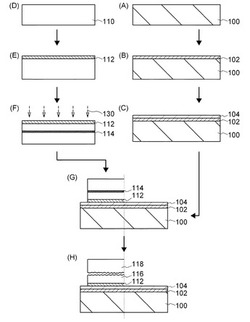

表示装置の製造方法

【課題】製造工程の低減を図った表示装置の製造方法の提供。薄膜トランジスタの特性の劣化を抑制した表示装置の製造方法の提供。

【解決手段】同一の基板上に、ゲート電極、ゲート絶縁層、結晶質と非晶質の積層の半導体層、ソース電極およびドレイン電極を順次形成した第1の薄膜トランジスタと、ゲート電極、ゲート絶縁膜、非晶質の半導体層、ソース電極およびドレイン電極を順次形成した第2の薄膜トランジスタを備える表示装置の製造方法にあって、

前記ゲート絶縁膜の形成後に、前記基板上に非晶質の半導体層を形成し、該非晶質の半導体層に選択的に前記結晶質の半導体層を形成する工程と、

アルカリ性のアミン系のエッチング液を用いて前記結晶質の半導体層を残存させて前記非晶質の半導体層をエッチングする工程とを備える。

(もっと読む)

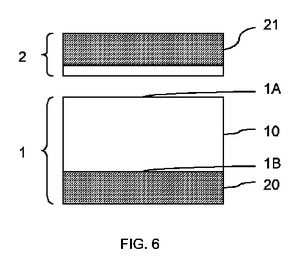

基板とその一方の面上に堆積させた層とを含む構造体の製造方法

本発明は、電子工学、光学、光電子工学または光起電力工学用の、基板(10)と前記基板(10)の一方の面上に材料を堆積させることにより形成された層(20)とを含む構造体(1)の製造方法に関し、この方法は、前記基板(10)の面(1B)が堆積した材料の層(20)により覆われ、前記基板の他の面(1A)が露出している前記構造体(1)を形成するように、−一方で前記基板(10)を、他方で残りの部分を画定する脆化区域を含む脆化された基板を形成する工程、−前記脆化された基板の2つの面のそれぞれの上に前記材料の層を堆積させる工程、−前記脆化された基板をへき開する工程を含むことを特徴とする。  (もっと読む)

(もっと読む)

液晶表示装置

【課題】poly−Si層とa−Si層が積層されたボトムゲート型TFTによる内蔵型駆動回路を形成した表示装置の製造コストを低減する。

【解決手段】ゲート電極103およびゲート絶縁膜104の上にpoly−Si層107とa−Si層108が積層されてアクティブ領域が形成されている。poly−Siは全面に形成されたa−Siの一部をレーザアニールによってpoly−Siに変換している。poly−Siとa−Siを同時にドライエッチングし、エッチング速度の差によってa−Siのみ除去し、poly−Si層107を残留させる。これによってフォトリソグラフィ工程無しに、poly−Si層107のパターニングが出来、製造コストを低減できる。

(もっと読む)

結晶化方法および結晶化装置

【課題】結晶成長時間を十分に長くして、大粒径の結晶を得ることができる半導体膜の結晶化方法、及び結晶化装置を提供すること。

【解決手段】レーザ発振器から発振されたパルスレーザ光を、分割し、互いに光路長の異なる光路を進んだ後に合成する工程、合成されたパルスレーザ光を位相変調素子により所定の光強度分布を有するパルスレーザ光に変調する工程、及び前記所定の光強度分布を有するレーザ光を非単結晶膜に照射し、非単結晶を結晶化する工程を具備し、前記パルスレーザ光を分割し、合成する工程は、順番に配列された3つ以上の光学的分割・合成手段において、1つの光学的分割・合成手段により分割された一方のパルスレーザ光を、次の分割・合成手段により順次分割するとともに、1つの光学的分割・合成手段により分割された他方のパルスレーザ光を前の分割・合成手段により分割された他方のパルスレーザ光と合成することを特徴とする結晶化方法。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、及び、電子装置

【課題】リーク電流の発生の抑制を行うゲッタリングの効果を良好に得ることが可能な薄膜トランジスタを提供する。

【解決手段】チャネル領域を挟んでソース領域とドレイン領域とを有する半導体層を備える薄膜トランジスタであって、上記ソース領域及びドレイン領域の少なくとも一方の領域は、チャネル領域よりも膜厚の薄い領域を有する薄膜トランジスタであり、好ましくは、上記ソース領域及びドレイン領域の少なくとも一方の領域は、該領域内で膜厚の厚い領域と膜厚の薄い領域とを有する薄膜トランジスタである。

(もっと読む)

位相シフトマスク

【課題】 例えば結晶化装置に適用されて、結晶核の位置を制御することができ、ひいては結晶の形成領域を二次元的にほぼ制御することのできる位相シフトマスク。

【解決手段】 ほぼ直線状の境界線(10a)の両側に形成されて第1の位相差を有する第1領域(11)および第2領域(12)と、境界線に沿って第1領域および第2領域のうちの少なくとも一方の領域に形成された所定形状の微小領域(13)とを備え、微小領域が形成された第1領域または第2領域と微小領域との間に第2の位相差が付与されている。

(もっと読む)

結晶質半導体膜の製造方法およびアクティブマトリクス基板の製造方法

【課題】従来のLPS膜よりも平均結晶粒径が大きく、且つ、従来の固相結晶化膜(例えば、CGSシリコン膜)よりも平均結晶粒径が小さい結晶質半導体膜の製造方法を提供する。

【解決手段】本発明の結晶質半導体膜の製造方法は、第1および第2主面を有する透明な基板を用意する工程と、基板の第1主面上に所定のパターンの遮光層を形成する工程と、遮光層の少なくとも一部を覆う半導体膜であって、遮光層と重ならない第1領域と、遮光層と重なる第2領域とを有する非晶質状態の半導体膜を形成する工程と、第2主面側から半導体膜に光を照射し第1領域の半導体膜だけを選択的に結晶化することによって第1結晶領域を形成する工程と、その後に、第2領域の半導体膜を固相結晶化することによって第2結晶領域を形成する工程とを包含する。

(もっと読む)

121 - 140 / 390

[ Back to top ]