Fターム[5F152CE12]の内容

Fターム[5F152CE12]の下位に属するFターム

Fターム[5F152CE12]に分類される特許

41 - 60 / 390

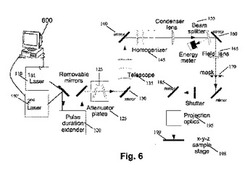

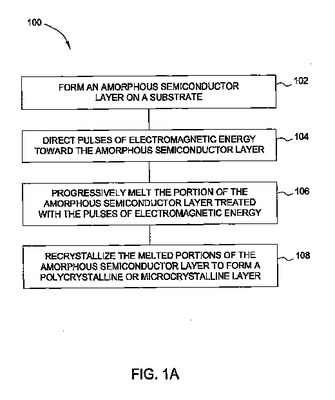

半導体用途のための結晶化処理

基板上に結晶半導体層を形成するための方法および装置が提供される。半導体層は気相堆積によって形成される。パルスレーザ溶融/再結晶化プロセスが半導体層を結晶層に変換するために実行される。レーザまたは他の電磁放射のパルスがパルス列に形成され、処置ゾーンにわたって均一に分配され、連続する隣接した処置ゾーンがパルス列にさらされて、堆積された材料を結晶材料に漸進的に変換する。  (もっと読む)

(もっと読む)

非周期パルス逐次的横方向結晶化のためのシステムおよび方法

非周期パルス逐次的横方向結晶化のための開示されたシステムおよび方法は、薄膜を処理することに関する。(選択方向に薄膜を進行させながら)薄膜を処理する方法は、第1のレーザパルスおよび第2のレーザパルスにより薄膜の第1の領域を照射し、第3のレーザパルスおよび第4のレーザパルスにより薄膜の第2の領域を照射することを含み、第1のレーザパルスと第2のレーザパルスとの間の時間間隔は、第1のレーザパルスと第3のレーザパルスとの間の半分の時間間隔よりも短い。いくつかの実施形態において、各パルスは、形成されたビームを提供し、冷却の際横方向から結晶化する溶融区域を形成するために、その厚さの全体にわたって、薄膜を溶融させるのに十分な流束量を有する。いくつかの実施形態において、第1の領域および第2の領域は互いに隣接している。いくつかの実施形態において、第1の領域および第2の領域は、離間して配置される。 (もっと読む)

シリコン薄膜の処理方法およびフラッシュランプ照射装置

【課題】基板とアモルファスシリコン薄膜との間に部分的に金属層が配置されていても、結晶粒径が均一でクラックのないポリシリコン薄膜を得ることができるシリコン薄膜の処理方法およびこの方法に用いられるフラッシュランプ照射装置を提供する。

【解決手段】点灯時のパルス幅が50〜200μsecのフラッシュランプからの光を、基板上に部分的に配置された金属層を介して形成された厚みが30〜100nmのアモルファスシリコン薄膜に照射して、ポリシリコン薄膜を形成するシリコン薄膜の処理方法において、長波長側の光をカットする波長カットフィルタを介して、フラッシュランプからの光をアモルファスシリコン薄膜に照射する工程を有し、波長カットフィルタによってカットされる光の波長領域の短波長側端の波長が650nm以下、アモルファスシリコン薄膜に照射される光の照射エネルギーが2.00〜3.10J/cm2 である。

(もっと読む)

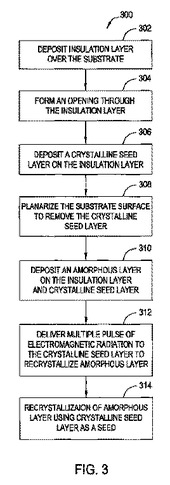

パルストレインアニール法を使用する薄膜の固相再結晶化の方法

本発明の実施形態は、電磁エネルギーの複数のパルスを使用する薄膜の固相再結晶化の方法を提供する。一実施形態では、アモルファス層が、再結晶化すると下の結晶性のシード領域またはシード層と同じグレイン構造および結晶配向を有するように堆積されている、結晶性のシード領域またはシード層へ複数のエネルギーのパルスを供給することによって、基板表面全体または基板の表面の選択された領域をアニールするために本発明の方法を使用することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法および製造装置

【課題】製造工数を増やすことなく、大粒径の多結晶シリコン膜を有する半導体装置を製造可能な製造装置、および、製造方法を提供する。

【解決手段】製造装置100は、反応室1と、ヒータ2と、圧力計3と、複数のガス導入管4a〜4gと、MFC5a〜5gと、ニッケル導入部6と、バルブ7a,7bと、ICP−MS8と、ガス排出管9と、APC10と、ポンプ11a,11bと、を備えている。製造装置100にニッケル導入部6を設けるため、製造工数を抑えて製造装置100内で大粒径の多結晶シリコン膜34の形成を行うことができ、製造コストを抑えることができる。

(もっと読む)

表示装置およびその製造方法

【課題】製造工数の増大をもたらすことなく、薄膜トランジスタのゲート絶縁膜と容量素子の誘電体膜を異なる層における絶縁膜を用いることによって、それらの特性に応じた膜厚に設定できる表示装置の提供。

【解決手段】基板上に薄膜トランジスタと容量素子が形成されている表示装置にであって、前記薄膜トランジスタは、

ゲート電極の形成領域を被って形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成され、平面的に観て、前記ゲート電極の形成領域内に開口を備える第2の絶縁膜と、

前記第2の絶縁膜上に前記開口を横切って形成され、両端に高濃度領域を備える島状の多結晶化された半導体層と、

前記半導体層の上面に前記半導体層の両端の高濃度領域のそれぞれの一部を露出させて形成された第3の絶縁膜と、

前記第3の絶縁膜から露出された前記半導体層の両端の高濃度領域のそれぞれに電気的接続がなされて形成された一対の電極と、を備えて構成され、

前記容量素子は、その誘電体膜が前記第3の絶縁膜と同層で同材料の絶縁膜によって構成されている。

(もっと読む)

半導体装置の製造方法

【課題】 単結晶構造の柱状構造を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に単結晶の柱状構造を形成する方法であって、前記半導体基板上に絶縁膜を形成する工程と、前記絶縁膜に溝を形成し、前記溝の底部に少なくとも前記半導体基板の一部を露出させる工程と、前記溝内部に少なくともゲルマニウムを含む埋め込み膜を形成する工程と、熱処理により前記埋め込み膜を溶融させる工程と、溶融した前記埋め込み膜を、前記半導体基板をシードとして単結晶化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法および半導体検査装置

【課題】モルファスシリコン膜から多結晶シリコン膜へ結晶化を行うレーザ処理工程でのレーザパワーをより最適値に合わせて、性能品質の向上した多結晶シリコン膜を安定して製造することが可能な半導体装置の製造方法および半導体検査装置を提供する。

【解決手段】レーザ処理工程13で、SPC工程12処理後の基板の中から抜き取られたモニタ基板に、異なるレーザパワーで、異なる場所にレーザ処理を行い、基板全領域に多結晶シリコン膜を形成した後、最適パワー検査抽出工程14でモニタ基板上に形成された膜質の異なる多結晶シリコン膜を検査装置で測定し、レーザパワーの最適値が求められ、レーザ処理工程13で後続のSPC工程処理後の基板表面に、最適なレーザパワーに設定されたレーザが照射され、基板全領域で高品質な多結晶シリコン膜が製造される。

(もっと読む)

シリコンナノ結晶構造体のアニール方法、およびそれを用いた基板の製造方法

【課題】結晶性を高めるとともに、表面荒れが抑制された酸素で終端されたシリコンナノ結晶構造体のアニール方法と基板の製造方法を提供する。

【解決手段】酸素で終端されたシリコンナノ結晶構造体を、950℃以上1250℃以下、かつ、窒素また希ガスから選ばれる第一のガスと酸素との混合ガスが、前混合ガスに対する酸素の濃度が10ppm以上100ppm以下であるガス雰囲気下でアニール処理する。

(もっと読む)

照射装置および半導体素子の製造方法

【課題】より均質な強度分布を有するレーザビームを安定して照射可能な照射装置を提供する。

【解決手段】レーザ光源11と、レーザ光源11からの射出レーザ光をP偏光(第1の直線偏光)とS偏光(第2の直線偏光)とに分離する偏光ビームスプリッタ13(偏光分離手段)と、第1もしくは第2の直線偏光を複数の光束に分割するシリンドリカルレンズアレイ対14(光束分割手段)と、光束を右旋回円偏光に変換する第1の1/4波長板15Aと、光束を左旋回円偏光に変換する第2の1/4波長板15Bとが光軸Zと直交するX軸方向(第1の方向)において交互に配列されてなる1/4波長板アレイ15と、右旋回円偏光および左旋回円偏光を集光し、表面3S(被照射面)へ向けて照射するコンデンサレンズ16(投影光学系)とを備える。

(もっと読む)

半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置

【課題】曲げストレスによるオン特性の劣化を抑制できる半導体装置、この半導体装置の製造方法、前記半導体装置を備えた画素アレイ基板、前記半導体装置を備えたセンシング素子アレイ基板、表示パネル、インプットパネル、表示装置、携帯機器、X線検査装置、及びレントゲン装置を提供する。

【解決手段】単結晶膜または多結晶膜からなる結晶化領域であるチャネル領域14と、アモルファス膜からなるアモルファス領域であるソース領域24及びドレイン領域34とからなる半導体層4を備えており、チャネル領域14は、半導体層4となるアモルファス膜を形成し、アモルファス膜に電流を流して一部分を結晶化することにより形成されてなる。

(もっと読む)

炭化シリコン膜の製造方法

【課題】良好な膜質であり所望の導電型や導電性に制御された炭化シリコン膜を低コストで効率よく製造する方法を提供する。

【解決手段】本発明の炭化シリコン膜の製造方法は、不純物領域を有する炭化シリコン膜の製造方法である。表層にシリコン膜16aを有する基板11のシリコン膜16aを炭化処理して、炭化された膜を含んだ炭化シリコン膜13を形成する工程を有する。不純物領域になる部分のシリコン膜を炭化処理する前に、この部分に不純物を注入する。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させ、かつ、炭化シリコンのデバイスとシリコンのデバイスが電気的に絶縁された構造とすることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上に下地層12を形成する工程と、下地層12上にシリコン膜を形成する工程と、シリコン膜をパターニングするパターニング工程と、パターニング工程の後にシリコン膜を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、炭化シリコン膜13をマスクに用いて、マスクが形成されていない領域の下地層12をエッチングする工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、パターニングされた炭化シリコン膜を得ることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14をパターニングするパターニング工程と、パターニング工程の後にシリコン膜14を炭化処理し炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】高温で長時間の処理が必要なエピタキシャル成長を用いることなく、熱応力の発生を抑え、信頼性に優れた、所望の膜厚の炭化シリコン膜を容易に得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含む第1シリコン膜14aを形成する工程と、第1シリコン膜14aを炭化処理し第1炭化シリコン膜13aを形成する工程と、第1炭化シリコン膜13aを形成した後に、第2シリコン膜14bを形成する工程と、第2炭化シリコン膜13bを形成する工程と、を少なくとも1回有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】エッチングが困難な炭化シリコン膜をエッチングすることなく、一つのチップに炭化シリコンのデバイスとシリコンのデバイスを容易に混載させることが可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、表層にシリコン膜14を有する基板11上のシリコン膜14を一部覆う位置にマスク15aを形成する工程と、マスク15aが形成されていない領域のシリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

炭化シリコン膜の製造方法

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

薄膜トランジスタ及び表示装置の作製方法

【課題】マスク数の少ない薄膜トランジスタの作製方法を提供する。

【解決手段】第1の導電膜102と、絶縁膜104と、半導体膜106と、不純物半導体膜108と、第2の導電膜110とを積層し、この上に多階調マスクを用いて凹部を有するレジストマスク112を形成し、第1のエッチングを行って薄膜積層体を形成し、第1の導電膜102がエッチングされた膜113に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層116Aを形成し、その後ソース電極及びドレイン電極等を形成することで、薄膜トランジスタを作製する。半導体膜としては結晶性半導体膜106を用いる。

(もっと読む)

表示装置の製造方法および表示装置

【課題】微結晶化による非晶質シリコンの残留割合を下げ、かつ生産効率を向上することができる表示装置を提供すること。

【解決手段】表示装置の製造方法は、非晶質シリコンからなる第1の半導体層を形成する第1の半導体積層工程と、前記第1の半導体層の上面と接するとともに不純物が添加された第2の半導体層を形成する第2の半導体積層工程と、前記第2の半導体積層工程の後に行われ、前記第1の半導体層を加熱することにより前記第1の半導体層の少なくとも一部を微結晶化させる微結晶化工程と、を含む。

(もっと読む)

41 - 60 / 390

[ Back to top ]