Fターム[5F152CE46]の内容

再結晶化技術 (53,633) | 被結晶化層 (7,497) | 前処理(結晶化のためのもの) (726) | 非晶質化 (48)

Fターム[5F152CE46]に分類される特許

1 - 20 / 48

半導体装置の製造方法

【課題】高いオン電流を得つつ、オフリーク電流を抑制することができる半導体装置を簡単に製造することができる方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上にゲート電極を形成する。ドレイン層形成領域に第1導電型の不純物を導入する。次に、熱処理を行うことによってドレイン層形成領域の第1導電型の不純物を活性化する。次に、ソース層形成領域に不活性不純物を導入することによって該ソース層形成領域の半導体基板の単結晶をアモルファス化する。次に、ソース層形成領域に第2導電型の不純物を導入する。次に、半導体基板にマイクロ波を照射することによって少なくともソース層形成領域のアモルファス半導体を単結晶化し、かつ、ソース層形成領域の第2導電型の不純物を活性化する。ソース層形成領域における第2導電型の不純物の深さは、ドレイン層形成領域における第1導電型の不純物の深さよりも浅い。

(もっと読む)

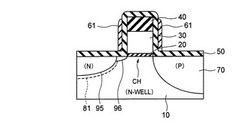

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

単結晶の半導体層を支持基板上に転写する方法

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

半導体装置の製造方法

【課題】 固相エピタキシャル成長によって、所望の面方位を有する結晶を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、第1の面方位を有するシリコン基板11上の一部に、アモルファス層13を形成する工程と、そのアモルファス層13にマイクロ波を照射し、前記アモルファス層13を第1の面方位を有する結晶層とする工程とを有していることを特徴とする半導体装置の製造方法を提供することができる。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】イオン注入によりアモルファス化された領域に光照射による活性化を行った場合に、表面に凹凸が発生するのを防止した薄膜半導体素子及びその製造方法を提供する。

【解決手段】基板1上にそれぞれ形成されたnチャネル島状半導体層4a及びpチャネル島状半導体層4b、前記島状半導体層4a,4b上に形成されたゲート絶縁膜5、及び前記ゲート絶縁膜5上にそれぞれ形成されたゲート電極6a,6bを具備し、前記nチャネル島状半導体層4aへのn型不純物のイオン注入によりアモルファス化された領域の深さt1,t3と、前記pチャネル島状半導体層4bへのp型不純物のイオン注入によりアモルファス化された領域の深さt1,t2とは、それぞれほぼ同じであるようにイオン注入を行なう。

(もっと読む)

半導体薄膜の製造方法、半導体薄膜、及び薄膜半導体装置

【課題】大きな結晶粒径の結晶粒径で、且つ、3次元的に結晶方位を制御された結晶粒で構成された半導体薄膜を製造し、この半導体薄膜を用いた半導体薄膜によって、優れたキャリア移動度を得る。

【解決手段】半導体薄膜の製造方法は、基板上に非晶質膜を形成する非晶質膜形成工程と、前記非晶質膜形成工程で形成した非晶質膜の少なくとも一部を結晶化させて、膜面に平行な特定の結晶面を持つ第1の多結晶膜を形成する第1結晶化工程と、前記第1結晶化工程で形成した第1の多結晶膜に1方向からイオン注入を行うことにより、3次元的に方位制御された所定の結晶方位を有する結晶粒を残す一方、それ以外の結晶粒を非晶質化させるイオン注入工程と、前記イオン注入工程で残った3次元的に方位制御された所定の結晶方位を有する結晶粒をシ−ドとして非晶質領域を結晶化させることにより第2の多結晶膜を形成する第2結晶化工程と、を備える。

(もっと読む)

シリコンウェーハの製造方法

【課題】光加熱式のアニール炉の低コスト化および光加熱源の長寿命化が図れ、ウェーハ表面のボイド欠陥を消滅させ、ウェーハの表面粗さを小さく可能なシリコンウェーハの製造方法を提供する。

【解決手段】ウェーハ表層にイオン注入して形成されたアモルファスシリコン領域部が、単結晶シリコンに比べて吸光係数が高いので、シリコンウェーハより低い加熱温度で、アモルファスシリコン領域部のみを溶融できる。その結果、仮にウェーハ表面にボイド欠陥が存在しても、ウェーハより低温でボイド欠陥を消滅させ、その表面粗さを小さくできる。しかも、従来より低出力の光加熱式のアニール炉でこれらの効果が得られ、アニール炉の低コスト化および光加熱源の長寿命化が図れる。

(もっと読む)

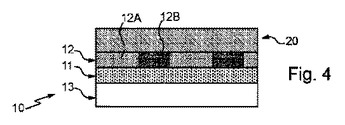

埋め込み電気絶縁連続層を備えたハイブリッド基板を製造する方法

本発明は、次の工程を含むハイブリッド基板を製造する方法に関する:第1の単結晶領域(12A)およびアモルファス材料の第2の隣接領域(12B)から構成された下位電気絶縁連続層(11)によって延在された混合層を含み、上記第2の領域は、上記第1の基板の自由表面の少なくとも一部を構成する第1の基板(10)が準備され;その表面で、所定の結晶配向を備えた基準層を含む第2の基板(20)が、少なくとも上記アモルファス領域上に、疎水性分子結合によって上記第1の基板に結合され;固相へのアモルファス領域の少なくとも一部の再結晶が、基準層の結晶配向に従って実行され、2つの基板は結合界面で分離される。  (もっと読む)

(もっと読む)

固体撮像素子及びその製造方法

【課題】赤色の光の感度を充分に得ることを可能にする固体撮像素子を提供する。

【解決手段】半導体層3の内部にフォトダイオードを構成する電荷蓄積領域4が形成され、この電荷蓄積領域4の内部又は下に、電荷蓄積領域4を透過した光を反射させて電荷蓄積領域4の中央部に向かわせる反射膜16が設けられている固体撮像素子を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】温度係数とそのシート抵抗値とを独立に調整することができる抵抗素子を提供する。

【解決手段】半導体基板1上に第1の多結晶半導体膜3を形成し、その表面から膜厚の途中までの領域に不活性元素をイオン注入することにより、該領域をアモルファス半導体膜3Aに変化させる。次に、アモルファス半導体膜3Aの中にキャリア不純物をイオン注入し、その後に熱処理を行うことにより、アモルファス半導体膜3Aを多結晶化することにより、第2の多結晶半導体膜4を形成する。これにより、第2の多結晶半導体膜4の平均的なグレインサイズは、第1の多結晶半導体膜3の平均的なグレインサイズよりも大きくなる。

(もっと読む)

粒子ビーム補助による薄膜材料の改良

基板を処理する方法の様々な例が開示される。特定の実施形態において、この方法は、チャンバ内のプラテン上に、上面および下面を有する基板を配置する工程と、複数の荷電粒子を含むプラズマであって、基板の上面の表面積と等しいかまたは大きい断面積を有するプラズマを、基板の上面上に発生させる工程と、荷電粒子を基板の上面の方に引き付けるよう、第1バイアス電圧を前記基板に印加する工程と、荷電粒子を、基板の上面全体の下方に延在する領域に導入する工程と、同時に、領域において、非晶質相から結晶相への第1相変態を開始する工程とを具えることを特徴とする。  (もっと読む)

(もっと読む)

半導体基板

【課題】DSB基板を用いてHOT構造の半導体基板を作製するに際し、その機能性基板の、互いに異なる結晶方位を有する結晶領域の境界における結晶欠陥の発生を抑制し、本来的な実用に足る前記HOT構造の半導体基板を提供する。

【解決手段】第1の結晶方位を有するシリコン支持基板と、このシリコン支持基板上に直接的に形成され、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第1の結晶領域と、前記シリコン支持基板の前記第1の結晶方位と異なる結晶方位を有する第2の結晶領域とを有するシリコン機能性基板とを具え、前記シリコン機能性基板の、少なくとも前記シリコン支持基板の主面にまで達するような、前記第1の結晶領域及び前記第2の結晶領域間の欠陥生成抑制領域を含むようにして半導体基板を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板上にオーミック電極を形成する際に、金属と炭化珪素との合金化熱処理を不要にする。

【解決手段】六方晶単結晶の炭化珪素基板11の(0001)面にリン(P)をイオン注入することで、その部分をアモルファス層12にする。次に、熱処理することで、アモルファス層12を立方晶単結晶のn型炭化珪素13に再結晶化させる。次に、そのn型炭化珪素13の上面にニッケル(Ni)を蒸着することで、電極14を形成する。炭化珪素13と電極14との間に形成されるショットキー障壁の高さが低くなり、合金化熱処理を用いることなく、電極14と炭化珪素13との間にオーミックコンタクトが実現される。

(もっと読む)

半導体記憶装置の製造方法

【課題】 固相成長に伴う欠陥領域の発生を制御することができ、回路を配置できない領域を最小限にとどめ、SOI結晶層を有効に活用することで製造コストの低減をはかる。

【解決手段】 半導体記憶装置の製造方法であって、シリコン基板上に形成された絶縁膜の複数箇所に開口部を設けた後、開口部が設けられた絶縁膜上及び該開口部内にアモルファスシリコン膜を形成し、次いで隣接する開口部間の中央付近でアモルファスシリコン膜を一方の開口部側と他方の開口部側とに分離する溝を形成し、次いで溝が形成されたアモルファスシリコン膜をアニールし、開口部をシードとして単結晶を固相成長させることによりシリコン単結晶層を形成し、次いでシリコン単結晶層上にメモリセルアレイを形成する。

(もっと読む)

1 - 20 / 48

[ Back to top ]