Fターム[5F152LM04]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 選択成長 (201) | マスク、基板の加工等 (47)

Fターム[5F152LM04]に分類される特許

1 - 20 / 47

シリコン基板、これを採用したエピ構造体及びシリコン基板の製造方法

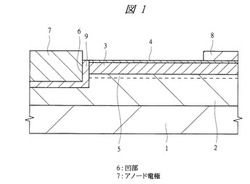

窒化物半導体ダイオード

【課題】高耐圧、低逆方向リーク電流特性を有する二次元電子ガスを導電層とした性能の高い窒化物半導体ダイオードを提供する。

【解決手段】窒化物半導体積層膜の上面に塩素ガスを用いたドライエッチングにより形成した凹部6の底面および側面部に対して、所望の不純物を拡散させる、または所望の不純物を添加した窒化物半導体を再成長することにより、アノード電極7が接触する窒化物半導体積層膜の側面部を高抵抗化させ、逆方向リーク電流を低減する。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

単結晶シリコン薄膜の製造方法、単結晶シリコン薄膜デバイスの製造方法及び太陽電池デバイスの製造方法並びに単結晶シリコン薄膜及びそれを用いた単結晶シリコン薄膜デバイス及び太陽電池デバイス

【課題】 ELOを利用して単結晶シリコン薄膜を製造するに際し、犠牲層のエッチングを容易にする単結晶シリコン薄膜の製造方法、単結晶シリコン薄膜デバイスの製造方法及び太陽電池デバイスの製造方法並びに単結晶シリコン薄膜及びそれを用いた単結晶シリコン薄膜デバイス及び太陽電池デバイスを提供する。

【解決手段】 単結晶シリコン基板1の表面にシリコンに対してエッチング選択性を有し且つエピタキシャルな関係にある犠牲層2を設け、該犠牲層2上に単結晶シリコン薄膜40をエピタキシャル成長させ、該単結晶シリコン薄膜40に複数の貫通孔42を形成すると共に当該貫通孔42を介して前記犠牲層2をエッチングし、単結晶シリコン薄膜4を分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】解像度限界より小さい寸法のパターンを規則的に形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、構造体としての第1及び第2のパターン13a、13b間に露出する種結晶としての半導体基板10からエピタキシャル結晶としての単結晶膜14を形成し、単結晶膜14を単結晶膜14の融点以下の温度で加熱することにより単結晶膜14を流動させ、流動した単結晶膜14が凝集することにより複数の凝集体15を第1及び第2のパターン13a、13b間に形成することを含む。

(もっと読む)

半導体ウェハの製造方法、半導体素子の製造方法、半導体ウェハ、半導体素子および電子装置

【課題】 歩留まりが大幅に改善された半導体ウェハの製造方法を提供する。

【解決手段】 本発明の半導体ウェハの製造方法は、基板301上の一部にストライプ状の保護膜302を形成する保護膜形成工程と、前記保護膜形成工程後、前記基板301上における前記保護膜302形成部位以外の部位に半導体結晶を成長させて半導体層を形成する半導体層形成工程とを含み、前記基板301として、前記保護膜302の長さ方向と平行な方向のオフ角θpの絶対値|θp|が、前記保護膜302の長さ方向と直交する方向のオフ角θoの絶対値|θo|よりも小さく、且つ、|θp|≦0.2°を満たすものを用いることを特徴とする。

(もっと読む)

半導体装置

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】上部拡散層上にコンタクトパッドを別途形成することなく、コンタクト合わせマージンを向上させる縦型トランジスタ構造を提供する。

【解決手段】本発明の半導体装置は、基板上に、柱状の半導体からなるボディ部(5)と、ボディ部の側面にゲート絶縁膜(10)を介して設けられるゲート電極(11)と、ボディ部の下部に接続される第1の拡散層(9)と、ボディ部の上面に接続される第2の拡散層(16)とを備える縦構造トランジスタを含む半導体装置であって、第2の拡散層(16)は、ボディ部の上面の面積以下の基板平面方向の断面を有する第1部分(14)と、第1部分の上部にボディ部の上面の面積以上の基板平面方向の断面を有する第2部分(15)とを備え、少なくとも第2部分がエピタキシャル成長層であり、隣接する縦型トランジスタ間に第2部分が接触することを防止する絶縁膜(17)を有する。

(もっと読む)

ダイヤモンド薄膜及びその製造方法

【課題】積層欠陥及び貫通転位の密度が十分に低いダイヤモンド薄膜構造とその製造方法を提供する。

【解決手段】本発明のダイヤモンド薄膜構造は、基板と、基板の主方位面の一部を覆うマスク材と、基板の主方位面の表面からエピタキシャル成長するダイヤモンド薄膜とで構成されるダイヤモンド薄膜構造であって、ダイヤモンド薄膜は、マスク材の上に形成され、ダイヤモンド薄膜の結晶方位は基板の結晶方位とそろっており、基板の主方位面の一部にストライプ状の溝が形成され、マスク材は、ストライプ状の溝を覆うように配置されている。

(もっと読む)

単結晶ゲルマニウムまたはシリコンゲルマニウムを形成する方法

【課題】基板中に形成されたトレンチ中に、単結晶のゲルマニウムまたはシリコンゲルマニウムを形成する改良された方法を提供する。

【解決手段】誘電体分離3(例えばSTI)を有する基板1を準備する工程と、基板材料1(例えばSi)のトレンチエッチング4を行う工程と、トレンチ4内への充填層5(例えばGe)の選択成長を行う工程と、略溶融温度での充填層6の加熱により、充填層5(例えばGe)の再結晶化7により達成される。

(もっと読む)

棒状ワイヤの作製方法

【課題】棒状ワイヤを基板から分離させる箇所を制御でき、棒状ワイヤの長さのばらつきを小さくすることができる棒状ワイヤの作製方法を提供する。

【解決手段】この棒状ワイヤの作製方法は、Si基板1上にGaNでできた棒状ワイヤ2を形成するワイヤ形成工程と、棒状ワイヤ2を基板1から切り離す切り離し工程とを有する。上記切り離し工程は、Si基板1を選択的にエッチングする選択エッチングを含んでいる。Si基板1と棒状ワイヤ2とが異なる材料でできているので、基板1と棒状ワイヤ2との境界面で基板1から棒状ワイヤ2を容易に分離できる。

(もっと読む)

CMOSデバイス用シリコンウェハの製造方法

【課題】 同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法の提供。

【解決手段】 CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に分離して製造する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ内にエピタキシャル成長された半導体層を有する半導体装置の製造方法を提供する。

【解決手段】シリコン基板11の主面にシリコン窒化膜31を形成する工程と、シリコン窒化膜31に開口31aを形成し、シリコン基板11の主面を露出させる工程と、開口31aを通して、シリコン基板11をエッチングし、トレンチ33を形成する工程と、トレンチ33の内面に、選択的にシリコン単結晶層をエピタキシャル成長させ、トレンチ33をシリコン単結晶層35cで埋め込む工程と、を具備する。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

3次元集積回路装置及びその製造方法

【課題】ガラス基板上に薄膜半導体層を形成した3次元集積回路装置を提供する。

【解決手段】ガラス基板11上に、単結晶もしくは準単結晶の2層の薄膜半導体層13,16が層間絶縁層14を介して積層され、2層の薄膜半導体層13,16は、下層の第1層の薄膜半導体層13と上層の第2層の薄膜半導体層16とが異なる材料であり、2層の薄膜半導体層13,16が、層間絶縁層14に形成された開口内を埋めて形成された、エピタキシャル層15によって接続され、エピタキシャル層15の表面部は、第2層の薄膜半導体層16と同じ材料の層であり、第1層の薄膜半導体層13及び第2層の薄膜半導体層16のうち、1層以上に能動素子Tr21,Tr22が形成されている3次元集積回路装置10を構成する。

(もっと読む)

1 - 20 / 47

[ Back to top ]