Fターム[5F152NN01]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904)

Fターム[5F152NN01]の下位に属するFターム

Fターム[5F152NN01]に分類される特許

21 - 39 / 39

半導体膜の製造方法及びそれを用いた電子部品の製造方法

【課題】幅広い材料選択が可能で生産性に優れた半導体膜の製造方法を提供する。

【解決手段】膜成長用基板1の表面の一部の領域に導電体層2を形成する工程と、

膜成長用基板1の表面の一部の領域以外の領域から半導体をエピタキシャル成長させ、導電体層2を覆う半導体膜3を形成する工程と、

誘導加熱用コイル4での電磁誘導により導電体層2を発熱させることで、半導体膜3を膜成長用基板1から分離する工程とを含む、半導体膜3の製造方法。

(もっと読む)

レーザーリフトオフ法およびレーザーリフトオフ装置

【課題】より平坦化された剥離面が得られるレーザーリフトオフ法およびレーザーリフトオフ装置を提供すること。

【解決手段】本発明による方法は、基板上に形成された結晶層に該基板側からレーザー光を照射することにより該結晶層を剥離するレーザーリフトオフ法であって、該レーザー光を楕円形にして照射することを特徴とする。本発明による装置は、基板上に形成された結晶層に該基板側からレーザー光を照射することにより該結晶層を剥離するレーザーリフトオフ装置であって、該レーザー光を楕円形にする手段を具備することを特徴とする。

(もっと読む)

III族窒化物系半導体、その製造方法、発光素子及び照明装置

【課題】 P型不純物がドープされ活性化されたIII族窒化物系半導体をアニールを必要とせずに容易に製造可能なP型導電性のIII族窒化物系半導体等を提供すること。

【解決手段】 基板110の一主面上に形成されたIII族窒化物系半導体(P型半導体層112)であり、III族窒化物系半導体に基板110からの不純物が含まれている。これにより、アクセプタ不純物としてのホウ素を、基板110から直接的にIII族窒化物系半導体に混入させることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体基板上にエピタキシャル成長したシリコンゲルマニウム膜の結晶欠陥や表面粗度を低減して半導体装置の信頼性を向上させる。

【解決手段】半導体ウエハ70上にシリコンゲルマニウム膜71がエピタキシャル成長され、シリコンゲルマニウム膜71上に歪シリコン膜72がエピタキシャル成長される。シリコンゲルマニウム膜71の厚み方向のゲルマニウム濃度分布は、シリコンゲルマニウム膜71の厚み方向の中間領域に最大濃度のピークを有している。その後、シリコンゲルマニウム膜71および歪シリコン膜72が形成された半導体ウエハ70に半導体素子が形成される。

(もっと読む)

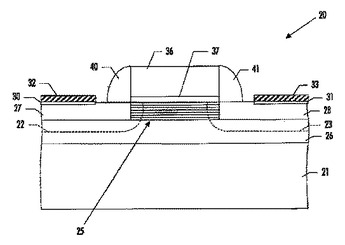

非半導体モノレイヤーを有するチャネルを含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板及びその上の少なくとも1つのMOSFETを含んでいる。このMOSFETは、空間的に隔てられたソース領域及びドレイン領域、ソース領域とドレイン領域との間のチャネル、及びチャネルの上に位置しチャネルとの界面を画成するゲートを含んでいる。ゲートは、チャネルの上に位置するゲート誘電体と、ゲート誘電体の上に位置するゲート電極とを含んでいる。また、このチャネルは、積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体モノレイヤーの結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。上記少なくとも1つの非半導体モノレイヤーは、チャネルとゲート誘電体との間の界面に対しておよそ4−100モノレイヤーの深さに位置付けられている。  (もっと読む)

(もっと読む)

光電子応用のための(Al,Ga,In)NとZnOの直接ウェーハ・ボンディング構造とその作製方法

光が導電性のあるZnOを通過し、(Al,Ga,In)NとZnOが直接ウェーハ・ボンディングされた発光ダイオード(LED)を提供する。(Al,Ga,In)NとZnOのウェーハの両方に平坦で清潔な表面を準備する。次に(Al,Ga,In)NとZnOウェーハの間でウェーハ・ボンディング工程を行うが、これは(Al,Ga,In)NとZnOウェーハを互いに張り合わせて、そこで窒素雰囲気中で一軸性圧力の下、設定温度で設定された時間ウェーハ・ボンディングを行う。ウェーハ・ボンディング工程の後、ZnOはLEDの内部から光取り出し量を増加させるために整形される。  (もっと読む)

(もっと読む)

薄膜トランジスタの作製方法及び薄膜トランジスタ

【課題】実質的なチャネル長の長さを短くし、半導体装置を微細化することができる半導体装置及びその作製方法を提供する。また、実質的なチャネル長の長さを短くすることによってゲート容量を減少させることができ、半導体装置の高速動作及び高性能化を実現できる半導体装置及び、その作製方法を提供する。また、製造工程を簡略化することができる作製方法を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に形成されたる島状半導体膜と、島状半導体膜上に形成されたゲート電極とを有する半導体装置であって、ゲート電極は高密度プラズマにより表面を酸化されることによって、スリミング化し、実質的なチャネル長を短くしている。

(もっと読む)

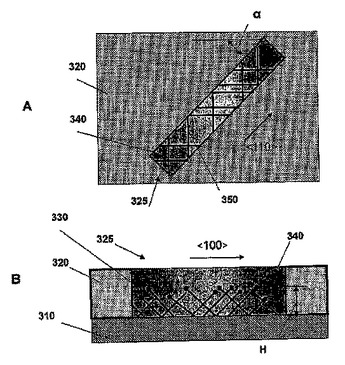

転位欠陥密度の低い格子不整合半導体構造およびこれに関連するデバイス製造方法

貫通転位が実質的にない上部分を有する制限されたエリア領域を備えている、モノリシック格子不整合半導体ヘテロ構造の製造、ならびにこのような格子不整合ヘテロ構造をベースとした半導体デバイスの製造。  (もっと読む)

(もっと読む)

剥離方法

【課題】被剥離層に損傷を与えず、小さな面積の被剥離層だけでなく、大きな面積の被剥離層も歩留まりが良好な剥離方法を提供する。

【解決手段】基板上に第1の材料を含む第1の層を形成する工程と、第1の層上に第2の材料を含む第2の層を形成する工程と、第2の層上に被剥離層を形成する工程と、加熱処理またはレーザー光の照射を行って、第2の層の圧縮応力を用いることにより、基板と被剥離層とを分離する工程とを含む。第1の材料は、Ti、Al、Ta、W、Mo、Cu、Cr、Nd、Fe、Ni、Co、Zr、Zn、Ru、Rh、Pd、Os、Ir及びPtから選択された1つ又は複数である。第2の材料は、酸化シリコンまたは酸化窒化シリコンである。

(もっと読む)

剥離方法

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。また、被剥離層の形成において、熱処理温度、基板の種類等の限定を受けない剥離方法を提供する。

【解決手段】基板上に金属層を形成し、前記金属層上に酸化物層を形成し、前記酸化物層上に被剥離層を形成し、前記被剥離層を前記金属層が設けられた基板から前記酸化物層の層内または界面において物理的手段により剥離する。

(もっと読む)

露光装置、およびこれを用いた半導体装置の作製方法

【課題】複数のレーザを用いて半導体膜のアニールを行うと、各々のレーザ照射領域の間隔が異なる。この工程の後に、予め基板上に形成したマーカーに合わせてリソグラフィ工程を行うと、レーザによって結晶化された部分に正しく露光されない。

【解決手段】レーザ照射工程で得られたレーザ照射領域をマーカーとし、ステッパの露光位置をこのレーザ照射領域中の大粒径領域に合わせて露光を行う。大粒径領域と結晶性不良領域では光の散乱強度が異なることを利用して、大粒径領域と結晶性不良領域を検出し、露光の位置を決定する。

(もっと読む)

半導体装置及びその作製方法

【課題】 信頼性が高く、製作コストを抑制した半導体装置及びその作製方法を提供する。

【解決手段】 本発明は、チャネル形成領域となる島状半導体膜と、前記島状半導体膜の側面に接し、ソース領域又はドレイン領域となる半導体膜を有する半導体装置及びその作製方法に関する。チャネル形成領域となる島状半導体膜とソース領域又はドレイン領域となる半導体膜をドーピング装置を用いないで形成することにより、製造コストを抑制することができる。かつチャネル形成領域である島状半導体膜の側面にソース領域又はドレイン領域が接することにより、空乏層が膜厚方向だけでなく横方向に広がり、ドレイン電圧による電界が緩和されるため信頼性の高い半導体装置を作製することができる。

(もっと読む)

レーザ処理装置、レーザ処理方法及び半導体装置の作製方法

【課題】

線状レーザの走査回数を減少させ、レーザアニールにかかる時間を短縮させ、半導体装置の作製工程、作製時間、作製にかかるコストを短縮させることを課題とする。

【解決手段】

本発明では、線状レーザビームの照射面に重なり合うように高温の気体を局所的に噴き付ける。線状レーザビームは、レーザ発振器から射出したレーザビームをレンズに入射することにより得られる。高温の気体は、気体圧縮ポンプで圧縮された気体をノズル型ヒータにより加熱することによって得られる。加熱された気体は、線状レーザビームの照射面に重ね合わせるように噴出する。

(もっと読む)

二枚のウエハを結合する前の熱処理

【課題】有機物や無機物又はガスの気泡が二枚のウエハーの界面に混入しないようにする方法を提供する。

【解決手段】第一のウエハ10から第二のウエハ20への層を転送する方法であって、第一のウエハの表面に、転送すべき層の厚みに近いか、より大きい厚みを有する半導体材料から選ばれた材料の層を確定する脆弱領域を第一のウエハが備え、転送すべき層の厚みに近いか、より大きい厚みを有する層が第二のウエハに接触するように二枚のウエハの表面を接触させる工程と、実質的に大気温度より高く200°Cから400°Cの範囲の第一の温度で約30分より長い第一の時間熱エネルギを供給する工程と、さらなる熱エネルギを供給して温度を第一の温度より高くして脆弱領域において第一のウエハから前記転送すべき層を剥がす工程とを備えたことを特徴とする。

(もっと読む)

レーザ照射装置およびレーザ照射方法

【課題】半導体膜全面に対して均一にレーザ処理を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】第1のレーザ発振器より出射された第1のレーザビームは、スリットを通し、さらに集光レンズを通した後に照射面に入射させる。同時に、照射面において第2のレーザ発振器より出射された第2のレーザビームを第1のレーザビームに重ねて照射する。さらに、照射面に対して相対的に走査することによって、照射面を等しくアニールする。

(もっと読む)

薄膜集積回路の作製方法、及び素子基板

【課題】 シリコンウェハから形成されるICチップは利用形態の増大、需要の増大が予想され、さらなる低コスト化が要求される。

そこで本発明は、さらなる低コストでの生産が可能なICチップの構造、プロセスの提供を課題とする。

【解決手段】 本発明において、剥離層に金属膜と、該金属膜を有する反応物を用いることを特徴とする。金属膜、又は金属を有する反応物はエッチング速度が高く好ましく、さらに、金属膜、又は金属を有する反応物をエッチングする化学的手段に加え、物理的手段を用いることができ、より簡便に、短時間で剥離層を除去することができる。

(もっと読む)

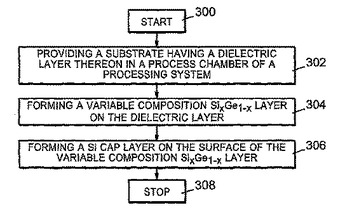

可変シリコン−ゲルマニウム組成を有するシリコンゲルマニウム薄層半導体構造および加工方法

誘電体層(410,510,610)、誘電体層(410,510,610)上の可変組成SixGe1-x層(440,520,620)、および可変組成SixGe1-x層(440,520,620)上のSiキャップ層(450,530,630)を持った基板(400,500,600)を含むSiGe薄層半導体構造である。可変組成SixGe1-x層(440,520,620)は、勾配を付けたGeを有するSixGe1-x層(520,620)、または、それぞれ異なったGe含有量(421,431)を有する複数のSixGe1-xサブ層(420,430)を含むことができる。本発明の一実施形態では、SiGe薄層半導体構造は、誘電体層(610)、誘電体層(610)上のSi含有シード層(615)、シード層(615)上の可変組成SixGe1-x層(620)、及び可変組成SixGe1-x層(620)上のSiキャップ層(630)を持つ半導体基板(600)を含む。SiGe薄層半導体構造を加工するための方法と処理ツール(1,100)も提供される。  (もっと読む)

(もっと読む)

窒化物半導体エピタキシャル層を成長させる方法

本発明は、窒化物半導体エピタキシャル層を成長させる方法に関し、第1の窒化物半導体エピタキシャル層の上に第2の窒化物半導体エピタキシャル層を第1の温度で成長させる第1の段階と、第2の窒化物半導体エピタキシャル層の上に第3の窒化物半導体エピタキシャル層を第2の温度で成長させる第2の段階と、第2の温度より高い第3の温度に昇温して第2の窒化物半導体エピタキシャル層から窒素を放出する第3の段階と、を含む窒化物半導体エピタキシャル層を成長させる方法を提供し、これにより基板の反りおよび格子欠陥密度を低減することができる。

(もっと読む)

(もっと読む)

マスクを通るラテラル成長による窒化ガリウム基板の製造とそれから製作されたデバイス

多段を用いたエピタキシャルラテラルオーバーグロースにより窒化ガリウム基板の成長を行う。開口部領域を有するマスクされた基板上で、選択的成長により最初に三角形ストライプを作成すると、大部分の貫通転位は90°曲がる。第2段では、成長条件を変化させてラテラル成長速度を高め、平坦な(0001)面を生じさせる。この段階で、表面上の転位密度は<5×107cm-2である。転位は主に、2つのラテラル成長したファセットがぶつかり合って合体した合体領域に存在する。転位密度をさらに低下させるため、2回目のマスキング工程を開口部が1回目のそれの真上にくるように行う。合体領域の貫通転位(TD)は上層には伝播しない。したがって、転位密度は全表面にわたって<1×107cm-2まで低下する。  (もっと読む)

(もっと読む)

21 - 39 / 39

[ Back to top ]