Fターム[5H740HH03]の内容

電力変換一般 (12,896) | 主回路スイッチング素子制御回路用電源 (495) | 主回路スイッチング素子の両端からとるもの (40)

Fターム[5H740HH03]に分類される特許

1 - 20 / 40

電力変換装置用部品

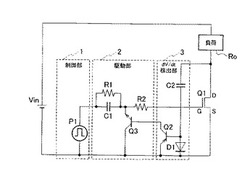

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減できるゲート駆動回路を提供する。

【解決手段】双方向に導通可能なスイッチング素子Q1のゲートに正電圧を印加してオンさせ、ゲートに負電圧を印加してオフさせる駆動部2と、スイッチング素子Q1に逆方向電流が流れる前にゲートへの負電圧の印加を解除する負電圧解除部3とを備える。

(もっと読む)

ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

(もっと読む)

スイッチ両端の電圧を制限するためのシステム、方法、および装置

【課題】電圧クランプ回路構成を用いてスイッチ両端の電圧を制限するためのシステム、方法、および装置を提供する。

【解決手段】電圧クランプ回路構成125は、入力227および出力229を備えた整流器回路225であって、入力227は動作回路構成に渡って並列に連絡する整流器回路225と、整流器回路225の出力229と並列に連絡する電子能動スイッチング素子205と、電子能動スイッチング素子205と並列に連絡する少なくとも1つのツェナー・ダイオード210と、を備えていても良い。電子能動スイッチング素子205およびツェナー・ダイオード210に渡る電圧が所定の値を満たすかまたは超えた場合には、電流が電子能動スイッチング素子205を通って流れて、動作回路構成に渡る電圧を電圧クランプ回路構成125の電圧制限内に制限する。

(もっと読む)

レベルシフト回路及びスイッチング電源装置

【課題】dv/dt印加時に誤動作を防止し且つローサイド側からハイサイド側へ信号を伝達し低電圧でも広い範囲で動作するレベルシフト回路。

【解決手段】トランジスタMN3とトランジスタMN4とをオン/オフさせるパルス発生回路10、第1抵抗R1の両端に第3抵抗R9と非線形特性を有し且つ一定以上のdv/dt過渡信号が印加された場合にオンするダイオードD3〜D6とが接続された直列回路、第2抵抗R2の両端に第3抵抗と同じ抵抗値を有する第4抵抗R10とダイオードとが接続された直列回路、MN3がオンである場合にセット信号、MN4がオンである場合にリセット信号を生成し、MN3のドレインにおける電位とMN4のドレインにおける電位との間において電圧差が生じていない場合にはいずれの信号も生成しない制御部、セット信号とリセット信号とに基づいて入力信号をレベルシフトした出力信号を出力するフリップフロップ12を備える。

(もっと読む)

電力変換装置

【課題】半導体スイッチング素子を用いたセルを複数カスケード状に接続して構成される電力変換装置を制御する場合、複数のセルと中央制御装置間で通信を行う必要があるがセル数の増大により通信の情報量および情報処理の負荷が増大する。本発明の課題は、各セルと中央制御装置との間で通信する情報量を低減することである。

【解決手段】本発明の電力変換装置は、複数のセルをカスケード状に接続して構成されるアームを複数備え、前記セルを構成する中央制御装置と通信を行うセル制御装置への電力供給を主回路から供給する機能を備えるものである。

【効果】本発明の電力変換装置では、各セルのセル制御装置の電力を主回路から供給することにより、各セルの主要部品が故障した時に該当セルのセル制御装置と通信ができなくなることにより、該当セルが故障したことを中央制御装置が認識できる。

(もっと読む)

半導体装置

【課題】本発明は、ブートストラップダイオードを備える半導体装置の省エネルギー化ができる半導体装置を提供することを目的とする。

【解決手段】トーテムポール接続された高圧側パワーデバイスと低圧側パワーデバイスの駆動を制御する半導体装置であって、回路負荷を有し、該高圧側パワーデバイスを制御する高圧側駆動回路と、該低圧側パワーデバイスを制御する低圧側駆動回路と、該低圧側駆動回路と接続され該低圧側駆動回路の電源電位であるVCC電位を該低圧側駆動回路に与えるVCC端子と、アノードが該VCC端子と接続されカソードが該高圧側駆動回路と接続され、該高圧側駆動回路の電源電位であるVB電位の充電に用いられるブートストラップダイオードと、該VB電位が該VCC電位よりも小さくなる前に該回路負荷を遮断する手段とを備えたことを特徴とする。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ノーマリーオン型の第5の電界効果トランジスタ16,17を含み、入力信号処理部65から受けたスイッチング制御信号の基準電圧をシフトした信号を出力するためのレベルシフト部62と、ノーマリーオン型の第1の電界効果トランジスタ51および第3の電界効果トランジスタ53と、ノーマリーオフ型の第2の電界効果トランジスタ52および第4の電界効果トランジスタ54とを備え、レベルシフト部62、第1の電界効果トランジスタ51および第3の電界効果トランジスタ53は第1の半導体チップ71に含まれている。

(もっと読む)

負荷制御装置

【課題】負荷への電力投入時における突入電流による素子の破壊又は劣化を防止しうる負荷制御装置を提供する。

【解決手段】操作スイッチ4から起動信号を受信したときに、制御部13は、第1電源部14への電力を供給する電源が第2電源部15から第3電源部16に切り替わる前に、主開閉部11に対して主スイッチ素子11aを導通させるための初期駆動信号を出力する。

(もっと読む)

ゲート駆動回路

【課題】スイッチング損失低減のためにゲート抵抗を小さくすると、ゲート・ソース間電圧が振動しスイッチング素子が誤動作すること、ゲート駆動回路用電源が大型になることなどが問題となる。

【解決手段】トランス6aとコンデンサ7の直列回路をスイッチング素子と並列に接続し、前記トランスと磁気結合した第1の巻線を第1のダイオード8を介して前記スイッチング素子の正極端子とゲート端子との間に、前記トランスと磁気結合した第2の巻線を第2のダイオード9を介して前記スイッチング素子の負側端子とゲート端子との間に、各々接続する。

(もっと読む)

電力用半導体素子の駆動制御回路およびインテリジェントパワーモジュール

【課題】供給される電源電圧が変動する場合であっても、電力用の半導体スイッチング素子を安定に動作させることが可能な駆動制御回路を提供する。

【解決手段】半導体スイッチング素子(IGBT)2の駆動制御回路1は、分圧回路20と、駆動部10と、定電圧回路30とを備える。分圧回路20は、直流電源40から供給された電源電圧VSを分圧し、分圧された電源電圧VSを取出すための分圧ノードNDを有する。分圧ノードNDは、IGBT2のエミッタEと接続される。駆動部10は、外部から入力された制御信号SGに応じて、ゲート電極Gを、直流電源40の正極側の電源ノードNPおよび分圧ノードNDのいずれかと電気的に接続することによってIGBT2をオンまたはオフにする。定電圧回路30は、正極側の電源ノードNPと分圧ノードNDとの間に接続され、これらのノードNP,ND間の電圧を一定に保つ。

(もっと読む)

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

スイッチング回路及び電力変換回路

【課題】スイッチング回路や電力変換回路について、単アーム構造の場合でも導通制御端子電源の自給化を可能とする。

【解決手段】スイッチ素子17と制御端子電源用コンデンサ21を備え、制御端子電源用コンデンサの放電によりスイッチ素子のゲート端子に電圧を印加するようにされているスイッチング回路について、制御端子電源用コンデンサの負側端子は、主電源5の基準電圧端子18に接続するとともに、ハーフブリッジ回路22を介してゲート端子に選択的に接続できるようにし、制御端子電源用コンデンサの正側端子は、ハーフブリッジ回路24を介して主電源の正側端子15とスイッチ素子のソース端子に対して選択的に接続できるようにする。そして制御端子電源用コンデンサは、正側端子が主電源に接続することで充電がなされる一方で、負側端子がゲート端子に接続し、正側端子がソース端子に接続することで放電する。

(もっと読む)

電力用半導体素子のゲート回路

【課題】損失が少なく且つ適切なゲート電圧得ることが可能な電力用半導体素子のゲート回路を提供する。

【解決手段】電力用半導体素子1用のゲート駆動回路3と、ゲート駆動回路3の制御電源と並列に接続された入力コンデンサ4と、入力コンデンサ4と電力用半導体素子1の正極間に接続された可変抵抗器10と、入力コンデンサ4と並列に接続された電圧安定化回路5と、入力コンデンサ4の電圧を検出する電圧検出器8と、可変抵抗器10及び電圧安定化回路5を制御するための電圧制御手段20とで構成する。電圧制御手段20は、起動時には可変抵抗器10が第1の抵抗値となるように制御し、定常運転時には、制御電源電圧が所定の電圧範囲となるように可変抵抗器10を平均して前記第1の抵抗値より大きい第2の抵抗値となるように制御し、制御電源電圧が過電圧レベルを超えたとき、電圧安定化回路5を投入する。

(もっと読む)

故障検出回路および電力調整器

【課題】カレントトランスを用いることなく、高価なICや規模の大きな回路構成を必要とすることなく、半導体素子の故障を検出できるようにする。

【解決手段】交流電源2とヒータ3との間の電力供給ラインに設けられてオンオフ制御されるスイッチング素子としてのサイリスタ4,5の故障を検出する回路12であって、サイリスタ4,5の両端電圧を、波形整形し、閾値と比較してデジタル信号に変換する変換部としての波形整形・比較部13と、変換されたデジタル信号を、電気的に絶縁して判定部としてのマイコン8に伝達する光結合部14と、伝達されたデジタル信号およびサイリスタ4,5に対するオンオフの制御指令に基づいて、故障の有無を判定する前記判定部としてのマイコン8とを備えている。

(もっと読む)

ゲート駆動装置

【課題】本発明は、外付け部品を要することなく、出力トランジスタのゲート電圧を適切にクランプすることが可能なゲート駆動装置を提供することを目的とする。

【解決手段】本発明に係るゲート駆動装置は、出力トランジスタTrのゲート電圧VGを駆動するものであって、ゲート電圧VG(図1ではゲート電圧VGの分圧電圧Va)と所定の閾値電圧Vbとの高低関係を検出する電圧検出回路41と、電圧検出回路41の検出結果に基づいて出力トランジスタTrのゲートと電源電圧VCCの印加端との間を導通/遮断するスイッチ51と、を有して成る構成とされている。

(もっと読む)

電圧駆動型半導体素子の過電圧保護装置

【課題】半導体素子を用いて電力変換装置を構成する場合、ターンオフ時半導体素子に印加される過電圧を電圧値が一定値になるようにゲート電圧を制御すると損失が大きくなる課題がある。

【解決手段】ターンオフ信号が入力されてからの素子電流を検出してターンオフ時の電流値に応じて過電圧抑制値を可変にする。即ち電流が所定値に減少するまでは過電圧抑制値を低く制御し、その後は高く制御することにより、損失を低減する。

(もっと読む)

スイッチング装置

【課題】抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、容量素子が過充電されないように放電経路を確保することができる、スイッチング装置の提供を目的とする。

【解決手段】半導体スイッチング素子Q1のスイッチング装置であって、半導体スイッチング素子Q1のコレクタ−ゲート間に設けられ、並列接続された抵抗素子R1と容量素子C1とを有する並列回路と、前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流すツェナーダイオードZ1,Z2と、前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流すツェナーダイオードZ3とを備えることを特徴とする、スイッチング装置。

(もっと読む)

インダクタ負荷ドライブ回路の逆起電力吸収回路

【課題】 実装面積が小さいサージ吸収保護回路の提供。

【解決手段】 インダクタ負荷(RL)を駆動するバイポーラトランジスタ(TR)のサージ吸収保護回路(100)において、前記インダクタ負荷はバイポーラトランジスタのコレクタ(C)に接続され、前記バイポーラトランジスタに対して双方向ツェナーダイオード(ZD)と第一抵抗(RB)を導線(104)により並列に設け、前記バイポーラトランジスタのエミッタ(E)により導線(103)をアース(GND)し、前記第一抵抗(RB)の他端側は導線(105)により導線(103)に接続し、双方向ツェナーダイオードと第一抵抗間の導線(104)にバイポーラトランジスタのベース(B)に接続する導線(106)を分岐させ、この導線(106)の他端に第二抵抗(R2)を設けた構造のインダクタ負荷ドライブ回路の逆起電力吸収回路。

(もっと読む)

インダクタ負荷ドライブ回路の逆起電力吸収回路

【課題】実装面積が小さいサージ吸収保護回路の提供。

【解決手段】インダクタ負荷RLは導線101に接続され、他端は導線102により電界効果トランジスタFETのドレインDに接続され、電界効果トランジスタに対して双方向ツェナーダイオードZDと第一抵抗RGSを導線104により並列に設け、電界効果トランジスタのソースSより導線103をアースし、第一抵抗RGSの他端側は導線105により前記導線103に接続し、双方向ツェナーダイオードと第一抵抗RGS間の導線104に電界効果トランジスタのゲートGに接続する導線106を分岐させ、この導線106の他端に第二抵抗R2を設けたインダクタ負荷ドライブ回路の逆起電力吸収回路100。

(もっと読む)

1 - 20 / 40

[ Back to top ]