Fターム[5J001BB09]の内容

Fターム[5J001BB09]に分類される特許

1 - 20 / 70

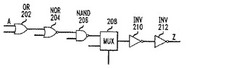

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

半導体装置及び遅延量調整方法

【課題】クロック信号の位相を遅延させる遅延回路とその遅延量を調整する回路とを備えた半導体装置において遅延量がクロック信号の周期的なジッタの影響を受けないようにする半導体装置及び遅延量調整方法を提供する。

【解決手段】第1のクロック信号を遅延させた第2のクロック信号を出力する可変遅延回路と、可変遅延回路における遅延量を制御する制御信号を出力する遅延量調整回路と、遅延量調整回路が制御信号を更新するタイミングを決定するタイミング信号を出力するタイミング信号発生回路と、を備えた半導体装置であって、タイミング信号発生回路は連続してタイミング信号を出力するものであって、互いに隣接するタイミング信号の間隔の内、少なくとも2つの間隔が互いに異なる。

(もっと読む)

クロックジェネレータ

【課題】従来の調節可能な遅延回路と用いることにより、異なるクロック領域のクロック信号のうちの1つが出力される調節可能な遅延回路の時間遅延が変更されても、それらのクロック信号間の同期位相関係を維持することが可能なクロックジェネレータを提供する。

【解決手段】クロックが入力される遅延回路の入力と出力を切り離した後に、遅延回路の遅延時間を変更して遅延回路の入出力を再び接続させる。同期回路は、遅延回路の入力と出力が切り離された状態においても、クロックの位相関係を追跡し、適切なタイミングで遅延回路を再接続させるための指示を与える。

(もっと読む)

デジタル遅延回路及びデジタル遅延回路の制御方法

【課題】クロック信号のジッタを低減すること。

【解決手段】マスタDLL回路11は、基準クロック信号CLKrを所定の位相まで遅延させるために使用する遅延素子の段数を示す第1段数データDs1を生成する。スレーブDLL回路12は、第1段数データDs1に基づいて使用する遅延素子の段数を示す第2段数データDs2を生成し、第2段数データDs2に応じた段数の遅延素子にて第1クロック信号CLK1を遅延させて第2クロック信号CLK2を生成する。スレーブDLL回路12の位相調整回路31は、第1段数データDs1が2つの値の間で遷移している場合、第1段数データDs1の変化に応じた補正を行って第2段数データDs2を生成する。

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

遅延装置

【課題】精度良く信号を遅延する。

【解決手段】遅延対象信号を遅延した遅延信号を出力する遅延装置であって、遅延対象信号を遅延させた信号を出力する遅延回路と、少なくとも一部の期間において遅延対象信号とは異なる論理値の信号を遅延回路へと入力させて、遅延回路に入力される信号の論理値毎の割合を基準割合に近付ける調整部と、を備え、調整部は、遅延対象信号および遅延対象信号を論理反転した反転信号を切り替えて遅延回路へと入力させる、遅延装置を提供する。

(もっと読む)

フリップフロップ、半導体集積回路、半導体デバイスおよびブレードサーバ

【課題】

回路オーバヘッドが小さく、かつ、ソフトエラーへの耐性が高い、高ソフトエラー耐性のフリップフロップおよび、それを用いた半導体集積回路を提供する

【解決手段】

ソフトエラーに対する耐性の異なる複数のラッチ回路と、前記複数のラッチ回路にクロックを供給するクロック分配部と、を備えたフリップフロップであって、前記複数のラッチ回路は、第一のラッチ回路と、前記第一のラッチ回路よりもソフトエラーに対する耐性の低い第二のラッチ回路の少なくとも2つのラッチ回路であることを特徴とするフリップフロップ。

(もっと読む)

信号伝送装置及び信号伝送方法

【課題】簡易な回路構成で信号のパルス幅やデューティ比を一定に保つことができるよう

にする。

【解決手段】エッジ抽出回路1は、入力パルス信号Dinの立ち上がりエッジ及び立ち下り

エッジを抽出し、抽出した立ち上がりエッジ及び立ち下りエッジを正パルス信号又は負パ

ルス信号のいずれかに統一したパルス信号n2を生成する。これにより、信号伝送回路2

における入力パルス信号Dinの立ち上がりの遅延と立ち下りの遅延による変動を入力パル

ス信号Dinの立ち上がり又は立ち下りで同じ条件にできる。従って、信号伝送回路2にお

ける入力パルス信号Dinの立ち上がりと立ち下がりにおける伝播遅延時間差が生じない。

信号伝送回路2は、エッジ抽出回路1により生成されたパルス信号n2を伝送する。波形

再生回路3は、信号伝送回路2により伝送されたパルス信号n2から波形を再生して出力

パルス信号Doutを得る。

(もっと読む)

半導体集積回路およびその動作方法

【課題】クロック選択回路の最終選択出力でのメタステーブルの障害の発生確率を低減する。

【解決手段】半導体集積回路に内蔵のクロック選択回路は、デコーダDEC、制御ユニットCnt、マルチプレクサMpxを有する。DECに選択信号SELが供給され、Cntに第1と第2のクロック信号CKIN0、1とデコーダDECの第1と第2の選択出力信号が供給され、MpxにCntの第1と第2の選択制御信号Q´0、1が供給される。Cntの第1と第2のゲートAND0、1の一方の入力にDECの第1と第2の選択出力信号が供給される。第1ゲートAND0の出力と第2ゲートAND1の他方の入力の間に直列接続の第1と第2のD型フリップフロップD−FF0、2と、第2ゲートAND1の出力と第1ゲートAND0の他方の入力の間に直列接続の第3と第4のD型フリップフロップD−FF1、3を含む。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

遅延回路及び可変遅延回路

【課題】簡単な構成で様々な遅延値を有する遅延回路を設計する技術及び遅延回路の電力消費量を減らす技術を提供すること。

【解決手段】直列に接続される複数の第1の遅延部210〜230と、複数の第1の遅延部210〜230の各々の出力端A〜Cに備えられ、対応する第1の遅延部210〜230の出力信号A〜Cまたは外部入力信号INを選択して出力する複数の第1の選択部250〜270と、最後段の第1の選択部270の出力信号を受信し、遅延設定情報SELに応じて設定される遅延値の分だけ、受信した信号を遅延して出力する第2の遅延部240とを備える。

(もっと読む)

パルス発生回路およびパルス幅変調器、遅延回路ならびにそれらを利用したスイッチング電源の制御回路

【課題】消費電力を低減する。

【解決手段】パルス発生部42は、所定の周波数のクロックCLKを受け、そのポジティブエッジと同期して遷移するパルス信号PWM1を発生する。インバータ44は、クロックCLKを反転する。フリップフロップ46は、インバータ44からの反転クロックCLK#のポジティブエッジのタイミングで、パルス信号PWM1を取り込む。論理ゲート48は、パルス信号PWM1とフリップフロップ46の出力PWM2を多重化する。セレクタ50は、論理ゲート48の出力と、パルス信号PWM1のいずれかを選択する。

(もっと読む)

PWMパルス生成装置

【課題】低クロック周波数のディジタル回路により高S/Nが確保できるPWMパルス生成装置を提供すること。

【解決手段】アナログの振幅変換信号Mをアナログ・ディジタル変換器11によりディジタル信号に変換し、パルス変換部13でパルス幅変調されたパルス信号を得るようにしたPWMパルス生成装置において、ディジタル信号により遅延時間が制御されるアナログ遅延器20を設け、ディジタルのパルスに更にディジタルの分解能の0/16〜15/16の遅延時間が付加されるようにして、パルスの分解能を16倍に細かくでき、1/16の周波数のクロックで同等の分解能が確保できるようにし、このとき変換テーブル14を設け、アナログ遅延器20を構成している回路素子の特性バラツキが補正されるようにしたもの。

(もっと読む)

1 - 20 / 70

[ Back to top ]