Fターム[5J001BB17]の内容

Fターム[5J001BB17]に分類される特許

1 - 20 / 52

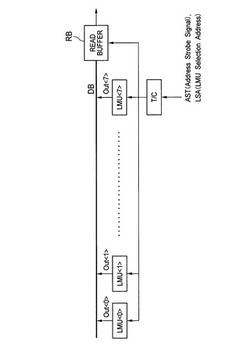

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システム

【課題】簡易な構成で時間制御を制御することができる可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システムを提供する。

【解決手段】可変遅延デバイス240は、飛行時間ガンマ線検出システムの光センサ140に接続され、複数の導電性ピン210、215が搭載された基板205を含む。複数の導電性ピンのうちの第1に接続している第1の端子、及び複数の導電性ピンのうちの第2に接続している第2の端子もまた、基板205に搭載されている。ジャンパ220は、基板205に対して所定の距離で複数の導電性ピンを電気的に接続し、可変遅延デバイス240の時間遅延は、複数の導電性ピン210、215とジャンパ220とによって形成される第1及び第2の端子間の電気経路に基づいて決定される。

(もっと読む)

半導体装置、シフトレジスタ、表示装置

【課題】非選択期間においてノイズが少なく、且つトランジスタを常時オンすることのない半導体装置、シフトレジスタ回路を提供することを目的とする。

【解決手段】第1〜第4のトランジスタを設け、第1のトランジスタの、ソースとドレインのうち一方を第1の配線に接続し、他方を第2のトランジスタのゲート電極と接続し、ゲート電極を第5の配線に接続し、第2のトランジスタの、ソースとドレインのうち一方を第3の配線に接続し、他方を第6の配線に接続し、第3のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第2のトランジスタのゲート電極に接続し、ゲート電極を第4の配線に接続し、第4のトランジスタの、ソースとドレインのうち一方を第2の配線に接続し、他方を第6の配線に接続し、ゲート電極を第4の配線に接続する。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号が入力され、入力されたクロック信号の波形の立ち上がりに合わせて波形が立ち上がりパルス幅が一定の幅であるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力が一方の入力側に入力される否定論理和回路120と、否定論理和回路120の出力信号を遅延させる第1遅延回路130を有し、第1遅延回路130により遅延された否定論理和回路120の出力を否定論理和回路120の他方の入力側にフィードバックする帰還回路140と、否定論理和回路120の出力信号が入力される第2ローパスフィルタ150と、を備える。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

パルス幅変調回路及びそれを用いたスイッチングアンプ

【課題】 温度係数によって直流バイアス電流Icおよび放電電流Idの電流値が変動する場合であっても、入力信号に正確に対応するパルス幅変調信号を出力する。

【解決手段】 電流生成回路14は、定電流I1を生成する定電流回路31と、定電流I1の1/2の電流値である電流I2と交流電圧esを電流に変換した電流Δiとを加算した電流I2+Δiを生成する差動回路32と、定電流I1を電圧Vb2に変換する電流電圧変換手段33と、電流電圧変換手段33から供給された電圧Vb2を電流に変換し、放電電流Idを生成する電圧電流変換手段34と、電流I2+Δiを電圧Vb1に変換する電流電圧変換手段35と、電流電圧変換手段35から供給された電圧Vb1を電流に変換し、充電電流Ic+Δiを生成する電圧電流変換手段36とを備える。

(もっと読む)

ノイズを補償するためにクロック信号を調節する技法

【課題】 クロック信号を調節してノイズを補償することである。

【解決手段】 第1の集積回路(IC)は、調節可能な遅延回路と第1のインターフェイス回路とを有する。第1のインターフェイス回路に与える遅延クロック信号を作り出すために、調節可能な遅延回路に第1のクロック信号が与えられる。第2のICは、電源電圧検知回路と、第1のICを相手にデータを転送する第2のインターフェイス回路とを有する。電源電圧検知回路は、第2のICの電源電圧内のノイズを示すノイズ信号を第1のICに与える。そのノイズ信号に基づいて、調節可能な遅延回路が遅延クロック信号の遅延を調節する。他の実施形態では、エッジが着色されたクロック信号が、集積回路(IC)間で高周波ジッタを共通にすることにより、それらのIC間のデータ伝送における高周波ジッタの影響を減らす。他の実施形態では、電源電圧を使用して複数のIC上でクロック信号を生成する。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

半導体装置

【課題】保護回路において、所望の遅延時間を実現する。また、遅延回路の小型化を図り、消費電力を低減させる。

【解決手段】遅延回路100は、第1のインバータ101〜第3のインバータ103、第4のpチャネルMOSFET7、第4のnチャネルMOSFET8、遅延抵抗121およびキャパシタ122で構成されている。遅延抵抗121は、第1のインバータ101の出力端子と第2のインバータ102の入力端子の間に接続されている。第4のnチャネルMOSFET8のゲート端子は、遅延抵抗121と第2のインバータ102の入力端子の間のノード113に接続されている。第4のnチャネルMOSFET8のゲート端子とドレイン端子の間には、キャパシタ122が接続されている。第4のnチャネルMOSFET8の帰還容量を用いることで、キャパシタ122の容量を、キャパシタ122の物理的な静電容量よりも擬似的に大きくする。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路の出力の相対的な遅延時間の分解能を高くする。

【解決手段】

信号発生装置(1)は、複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する複数の積分回路(111,112)と、前記複数の積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する複数の比較回路と(121,122)、前記各比較信号を入力し、これらの入力信号の全部または一部を、セットされた時間だけ遅延させた遅延信号を出力する少なくとも1つの遅延回路と(131,132)、前記各遅延信号、および前記遅延回路によっては遅延されていない比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた信号を出力する信号処理回路(14)とを備える。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

可変遅延回路

【課題】 本発明は、所定の遅延時間を設定可能な可変遅延回路を提供することを目的とする。

【解決手段】 可変遅延回路は、第1遅延回路6、第2遅延回路7、検出回路8、および選択回路9を備えている。第1遅延回路6は、複数の第1遅延段6aを縦続接続して構成されており、入力信号を初段で受けている。第2遅延回路7は、第1遅延段6aと同一の複数の第2遅延段7aを縦続接続して構成されており、第1タイミング信号を初段で受けている。検出回路8は、第2タイミング信号を受け、各第2遅延段7aから出力される遅延タイミング信号のうち、第2タイミング信号の遷移エッジに隣接する遷移エッジを有する遅延タイミング信号を求める。選択回路9は、検出回路8が求めた遅延タイミング信号を出力する第2遅延段に対応する第1遅延段から出力される遅延信号を選択する。

(もっと読む)

DLL回路

【課題】高精度な同期特性を有するDLL回路を提供する。

【解決手段】第1クロック信号CLK1が入力され、第1クロック信号CLK1を遅延した第2クロック信号CLK2を出力するとともに、制御信号Vcにより遅延時間が可変される可変遅延回路11と、第1クロック信号CLK1および第2クロック信号CLK2が入力され、第1クロック信号CLK1と第2クロック信号CLK2との位相を比較して、その位相差ΔΦに応じた信号を出力する位相検出回路12と、位相検出回路12の出力V1を積分する積分回路13と、積分回路13の出力V2を予め定めた基準値Vrefと比較し、比較結果を出力する比較回路14と、比較回路14の出力V3を平均化し、高周波成分を除去した信号を、制御信号Vcとして可変遅延回路11に出力するローパスフィルタ15と、を具備する。

(もっと読む)

三分周直交位相周波数分周器

【解決手段】局部発振器は、VCOの出力に結合されたプログラム可能な周波数分周器を備える。周波数分周器は、3で周波数分周するためにセットされることができる。除数に関係なく、周波数分周器は、90度で位相が互いに異なる直交位相信号(I、Q)を出力する。3で分周するために、周波数分周器は、三分周周波数分周器を備える。三分周周波数分周器は、三分周回路、遅延回路、及びフィードバック回路を備える。三分周回路は、VCOから信号を周波数分周し、それから、120度で位相が互いに異なる三つの信号C、A´、及びBを生成する。遅延回路は、信号A´の遅延バージョンAを生成するために、信号A´を遅延する。フィードバック回路は、遅延バージョンA(I)が、信号C(Q)に関して90度位相がずれるように遅延回路を制御する。 (もっと読む)

移相回路

【課題】入力信号の周波数に依存せずに入力信号に対して所定の位相差を有する出力信号を生成する。

【解決手段】VDDから定電流を供給する定電流回路201aと、入力電流に対してn倍の出力電流を流すカレントミラー回路204a、205aと、矩形波の入力信号1Aaの論理レベルによって定電流回路に流れる電流をカレントミラー回路に流すか、出力端子1Baに流すか切り替えるスイッチ回路202a、203aとを備えた波形生成回路102aにより、立ち上がり勾配1に対してn倍の立ち下がり勾配波形を有する三角波を生成する。これと反転信号1Abを入力した波形生成回路102bにより生成した三角波の電圧をコンパレータ103で比較し出力信号を生成する。入力信号のデューティー比が50%である場合には、1/(2+2n)周期遅延した出力信号が得られる。

(もっと読む)

デューティ補正回路

【課題】プロセスバラツキや、プロセス変更によりN型トランジスタ及びP型トランジスタ双方の特性が設計段階に対してずれても、デューティ比を所望の数値に補正するデューティ補正回路を提供する。

【解決手段】本発明のデューティ補正回路は、第1電源及び第1出力間に設けられ、第1信号をゲートに受ける第1チャネル型第1MOSトランジスタ(以下Tr)と、第2の電源及び第1出力間に設けられ、第1信号をゲートに受ける第2チャネル型第2MOSTrと、第1電源及び第1出力間に第1MOSTrと直列に設けられた第1チャネル型第3MOSTrと、第1電源及び第2の出力間に設けられ、第1出力線がゲートに接続された第1チャネル型第4MOSTrと、第2電源及び第2出力間に設けられ、第1出力線がゲートに接続された第2チャネル型第5MOSTrと、第1電源及び第2出力間で第4MOSTrと直列に設けられた第1チャネル型第6MOSTrと、第3及び第6MOSTrのゲートに其々バイアス電圧を印加するバイアス回路を備える。

(もっと読む)

位相制御装置、位相制御プリント板、制御方法

【課題】出力信号の位相を微小に制御することを課題とする。

【解決手段】第1の遅延ラインでは、入力信号の入力を受け付けると、信号の位相に対して遅延量を加える遅延器各々によって当該入力信号の位相に対して遅延量を加えるとともに当該遅延器ごとの遅延信号を出力し、DLL回路では、第2の遅延ラインが、外部にて周波数の異なる信号に切り替えることが可能である外部信号の入力を受け付けると、遅延器各々によって当該外部信号の位相に対して遅延量を加え、第2の遅延ラインの複数の遅延器すべてによって遅延された遅延信号と、当該第2の遅延ラインにて遅延量が加えられていない外部信号との位相差を比較し、位相比較器によって比較される遅延信号を外部信号に同期させる電圧であって、当該位相比較器によって出力された位相差から生成された制御電圧を、第1の遅延ラインおよび第2の遅延ラインの複数の遅延器各々に入力する。

(もっと読む)

半導体装置及び半導体装置のタイミング調整方法

【課題】遅延回路における製造ばらつきの影響を含む遅延時間の変動を抑制することが可能な半導体装置を提供する。

【解決手段】半導体装置は、遅延回路11と、遅延判定部5と、プログラム部6とを具備する。遅延回路11は、内部設定に基づいて、入力信号C1を遅延させてタイミング信号Sとして出力する。遅延判定部5は、タイミング信号Sを遅延させた複数の遅延信号T1〜T3に基づいて、複数の遅延信号T1、T2、T3の各々の遅延状態を判定する。プログラム部6は、遅延状態に基づいて、内部設定を変更する。

(もっと読む)

1 - 20 / 52

[ Back to top ]