Fターム[5J001DD04]の内容

Fターム[5J001DD04]の下位に属するFターム

抵抗又はコンデンサの値を変えるもの (127)

電圧により制御(基準電圧の可変を含む) (114)

出力パルス幅が入力パルス振幅、幅と関連 (14)

複数の制御手段を持つもの (70)

デジタル制御によるもの (469)

Fターム[5J001DD04]に分類される特許

21 - 40 / 75

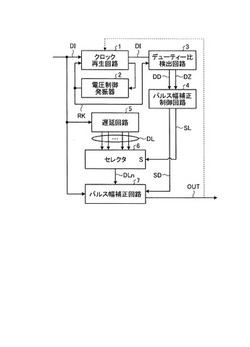

パルス幅補正装置およびパルス幅補正方法

【課題】二値化のコンパレートレベルを調整することなく、データが誤って取り込まれるのを防止すること。

【解決手段】デューティー比検出回路3は、二値化信号DIのデューティー比の基準値からのずれを検出し、遅延回路5は、二値化信号DIを所定の遅延量だけ順次遅延させた遅延信号DLを生成し、セレクタ6は、デューティー比検出回路3にて検出された二値化信号DIのデューティー比のずれに対応した遅延信号DLnを遅延信号DLから選択し、パルス幅補正回路7は、セレクタ6にて選択された遅延信号DLnを用いることにより、二値化信号DIのパルス幅を補正する。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

遅延発生回路の調整回路及び調整方法

【課題】 短時間かつローコストで遅延発生回路のスパン調整を可能とする遅延発生回路の調整回路及び調整方法を提供する。

【解決手段】 信号源1から出力される基準スパンに等しい周期の繰り返し信号と、同信号が遅延発生回路2及び調整用遅延発生回路3で遅延された信号とが位相比較器41で比較され、位相差に対応した信号は切替スイッチ71を介して調整用遅延発生回路3の遅延設定2及び遅延発生回路2のスパン設定1に交互にフィードバックされ、それぞれ位相差が0となるように制御される。連続する調整サイクルで得たスパン設定1の差が基準値以下になるまで切替スイッチ71,72を切り替えて位相ロック動作を繰り返す。

(もっと読む)

集積遅延回路を有する半導体スイッチ

【課題】位相シフトPWM信号を生成する回路を低価格で実現するための集積半導体スイッチを提供する。

【解決手段】PWM入力信号により変調される負荷電流に加え、PWM入力信号と比べ周期時間に所定の分数をかけて算出される時間だけ遅延するPWM出力信号を供給する遅延回路を負荷段のPWM制御のための出力段に具備する。出力段は、遅延回路と実際のパワー半導体スイッチと関連する監視制御回路を単一の部品として集積化する。このような出力段をカスケード接続することにより、正確な時間ベースに依存しない、多段負荷の位相シフトPWM制御のためのコントローラが簡単な方法で実現できる。

(もっと読む)

発振器

【課題】電流ロビング発振器を提供する。

【解決手段】電流ロビング発振器10は、リング状に接続した複数の反転形遅延素子12,14,16,18,20を備える。各反転形遅延素子は、出力ノード24を有するインバータ44を備える。また、発振器は、インバータの出力ノードから可変の量の電流を奪い取ることによりこの遅延素子に関連した遅延周期τの持続時間を制御するよう動作可能なプログラマブル電流回路50を備える。

(もっと読む)

デューティ・サイクルひずみを減少させる回路

【課題】デューティ・サイクルひずみを補正する方法および回路を提供する。

【解決手段】デューティ・サイクルひずみを補正する方法および回路。遅延挿入ゲートは、CMOSフリップ−フロップ回路で生じたデータ依存遅延ひずみを補正する。遅延挿入ゲートは、2つの電界効果トランジスタおよびカレント・ミラーを含む。2つのトランジスタのそれぞれは、上流の回路から入力信号をそれぞれ受け取る。これらのトランジスタの少なくとも1つは出力ノードに結合される。出力ノードは、遅延挿入ゲートの中の電圧状態を一時的に保持し、入力信号のデューティ・サイクルのひずみがあればそれを補正する。

(もっと読む)

遅延調整回路及び遅延調整方法

【課題】立ち上がりエッジの信号遅延の遅延量及び立ち下がりエッジの信号遅延の遅延量を、各々、他方の遅延量に影響を与えることなく、独立に調整可能な遅延調整回路及び遅延調整方法を提供する。

【解決手段】信号伝播経路301〜310の経路中に、遅延調整回路303が挿入される。前記遅延調整回路303の内部には、Rise信号調整部316とFall信号調整部317とを備えている。前期遅延調整回路303に入力された信号は整形される。そして、前記Rise信号調整部306において、その整形信号のうちRise信号のみについて遅延が調整され、その後に、前記Fall信号調整部307において、Rise信号が調整された信号のFall信号についてのみ遅延が調整される。ここで、一方の信号に遅延量を与えて遅延を調整するときに他方の信号にはその遅延調整の影響が及ぶことが抑制される。

(もっと読む)

インバータ回路および遅延回路

【課題】遅延回路などに適用した場合に、回路規模を小さくでき、貫通電流を防止でき、

かつ、消費電力を低減できるインバータ回路の提供

【解決手段】この発明は、入力信号IN1でオンオフするMOSトランジスタP11と、

入力信号IN2でオンオフするN型のMOSトランジスタN11と、直列接続されるとと

もにゲートとドレインが接続される2つのMOSトランジスタP12、N12とを備えて

いる。MOSトランジスタP11、MOSトランジスタP12、N12、およびMOSト

ランジスタN11は、第1電源VDDと第2電源VSSとの間に直列に接続されている。

MOSトランジスタP11とP12の共通接続部から出力信号OUT1を取り出し、MO

SトランジスタN11とN12の共通接続部から出力信号OUT2を取り出すようになっ

ている。

(もっと読む)

パルス発生回路

【課題】発振周波数が数MHz〜GHzの高周波用に適用可能であり、かつ消費電力が少ない、定電流回路を用いたパルス発生回路を提供すること。

【解決手段】パルス発生回路は、電源間に定電圧回路1を有し、電流制御素子7と波形発生部9とを直列に接続して、それらを定電圧回路1と並列に接続して構成されている。そして、波形発生部9は、平滑回路2と、水晶発振回路4と、水晶発振回路4からの出力を受けて最終出力波形のデューティ比を調整する出力デューティ調整回路5と、水晶発振回路4の発振波形と最終出力波形との位相差を調整する位相調整回路6と、を並列に接続して構成されている。使用する水晶振動子の周波数によっては、位相調整回路6の替わりに分周回路を並列に接続して構成されている。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

飛行時間式PET用の集積複数チャネル時間−デジタル変換器

飛行時間式の陽電子放出型断層撮影(PET)スキャナ2の放射線検出器10にて、放射線検知部20が放射線検出事象を表す信号22を生成する。時間−デジタル変換器34は、リング発振器36,36’として動作可能に相互接続されたデジタル遅延素子40と、少なくとも信号22が生成された時のリング発振器の状態に基づいて、放射線検出事象のタイムスタンプを生成するように構成された読み出し回路50,52,60,82,84,86,88とを含む。デジタル遅延素子に動作的に接続された遅延調整素子46が、デジタル遅延素子に実質的に共通の遅延を設定する。更に或いは代替的に、デジタル遅延素子40は、自身の遅延より実質的に長い移行時間を有する読み出しバッファ48’と、遅延素子の値をデジタル化するアナログ−デジタル変換器82,84と、デジタル化された値に基づいてリング発振器36’の状態を計算するデコード回路86,88とを含む。  (もっと読む)

(もっと読む)

入力回路および該入力回路を有する半導体集積回路

【課題】定常状態になるまでに所定の時間を要する内部回路を予め動作させることで無駄な時間(ロックオン時間)の低減を図る。

【解決手段】入力する外部制御信号CLKを受け取って内部制御信号S1を出力する入力バッファ210と、前記外部制御信号が動作しているか否かを検知する制御信号検知回路220とを具備し、前記入力バッファは、該入力バッファを制御する回路251〜253を介した前記制御信号検知回路の出力により、前記外部制御信号が動作している時には前記内部制御信号を出力するように構成する。

(もっと読む)

半導体集積回路装置

【課題】様々なパルス発生仕様に柔軟に対応することが可能な半導体集積回路装置を提供する。

【解決手段】例えば、外部クロック信号CLKのパルスを受けて、これよりも細いパルス幅を備えた基準パルス信号RPULを発生し、単位遅延ブロックDLYBKがリング状に接続されたディレイリング部DLYRG内でこのRPULを巡回させる。そして、各単位遅延ブロックDLYBK[1]〜[n]からの出力信号OUT[1]〜[n]を用いて、所定のパルス幅を備えた内部パルス信号IPULを連続して生成する。また、OUT[1]〜[n]の発生回数をカウントし、所定の回数となった際にストップ信号STPを発生する。STPは、DLYRGに供給され、RPULの巡回が停止する。これによって、IPULの発生回数が設定できる。

(もっと読む)

ダブルデータレート・インタフェース

本発明は、プロセッサとランダムアクセスメモリとの間で使用されるダブルレート・インタフェース及び方法に関するものであり、このダブルレート・インタフェースは、ランダムアクセスメモリからのデータストローブ信号に遅延を生じさせる手段を含む遅延線を備え、この遅延線は、データストローブ信号の遅延がセットアップ時間とデータバスの立上り時間の合計に等しくなるように構成されている。上記インタフェースは、遅延ロックループを備えた遅延線を含み、この遅延ロックループはリング発振器を備えている。

このリング発振器はバッファ及びバーニア遅延回路を含む。  (もっと読む)

(もっと読む)

デジタルDLL回路

【課題】信号の立ち上がり側と下がり側の遅延は個別に制御でき、クロックのデューティーずれやデータ信号の立ち上がり/立ち下がりの遅延差を補償することができるデジタルDLL回路を提供する。

【解決手段】信号の立ち上がりエッジ側遅延指定のための第1遅延指定値を保持する第1レジスタ11、信号の立ち下がりエッジ側遅延指定のための第2遅延指定値を保持する第2レジスタ12、信号の立ち上がり側と下がり側の遅延を個別に制御可能なデジタル制御可変遅延回路13、および可変遅延回路13の立ち上がり側遅延と立ち下がり側遅延をそれぞれ第1レジスタ11の第1遅延指定値および第2レジスタ12の第2遅延指定値に維持するよう制御を行う制御回路14を有する。

(もっと読む)

プログラム可能時間遅延装置

【課題】半導体チップが製造された後において、制御信号により遅延時間を調整することができるプログラム可能時間遅延装置とその方法を提供する。

【解決手段】本発明によるプログラム可能時間遅延装置は複数個の同等の部品10を有し、これらの部品により全時間遅延が決定される。これらの部品はそれらに接続されたゲート装置31、32、33、34を有する。これらのゲート装置はそのおのおのに加えられる制御信号に応答して、これらの部品がプログラム可能時間遅延装置に電気的に接続されるか、またはこれらの部品がプログラム可能時間遅延装置から電気的に取り除かれるか、のいずれかを決定する。電気的に接続された部品の時間遅延の合計が、このプログラム可能時間遅延装置の全時間遅延である。

(もっと読む)

A/D変換回路

【課題】TAD方式のA/D変換回路において、パルス遅延回路を再起動するまでの待ち時間を短縮して高速な連続動作を可能とすること、更には、高速な連続動作を可能としつつ回路規模を削減すること。

【解決手段】A/D変換を実行する毎に、休止期間を挿入してパルス遅延回路10及び周回数カウンタ13を初期化するため、ラッチ&エンコーダ11及びラッチ回路14が出力する数値データをそのままA/D変換データとして使用することができる。また、パルス遅延回路10の起動,休止を制御する起動制御信号RR及び周回数カウンタ13を初期化するカウンタ初期化信号RCを生成する制御信号生成回路15は、遅延回路16と論理回路17〜19により構成されたエッジ検出回路からなり、サンプリングクロックCKSの周期より短い休止期間を設定できるため、高速な連続動作が可能となる。

(もっと読む)

DLL回路及びその試験方法

【課題】通常時の基準クロックより周波数の低い1本の試験用クロックによるディレイ・ライン回路の動作試験を可能とする。

【解決手段】ディレイ・ライン回路101は、遅延量を変更可能であり、基準クロック信号RCLKに遅延を与えることができる。位相比較回路102は、基準クロック信号RCLKとディレイ・ライン回路101の出力信号との間又は基準クロック信号RCLKより周波数の低い試験クロック信号TCLKとディレイ・ライン回路101の出力信号との間の位相差を検出可能である。また、制御回路103は、位相比較回路102の検出結果に応じて制御信号を出力し、ディレイ・ライン回路101の遅延量を制御する。さらに、ディレイ・ライン回路101に対して、ディレイ・ライン回路101の出力信号と基準クロック信号RCLKとのいずれかを選択して入力できるよう構成されている。

(もっと読む)

プログラマブル遅延発生装置の調整方法及び調整装置並びに半導体検査装置

【課題】 タイミング精度の悪化並びに回路面積及び消費電力の増大を招かずに、必要な長さの共通遅延設定スパンを確保することができるプログラマブル遅延発生装置の調整方法及び調整装置、並びに当該装置を備える半導体検査装置を提供する。

【解決手段】 プログラマブル遅延発生装置に設けられる複数の遅延素子A,B,Cを調整して遅延素子A,B,Cの各々の遅延設定スパンの長さを所定の設定値T0に設定する。次に、設定可能な最短遅延時間である固定遅延時間と設定値T0に設定された遅延設定スパンの長さとの和である最大遅延時間が最大となる遅延素子を遅延素子A,B,Cから選択する。そして、選択された遅延素子以外の遅延素子の最大遅延時間が、選択された遅延素子の最大遅延時間と等しくなるように、選択された遅延素子以外の遅延素子を調整する。

(もっと読む)

21 - 40 / 75

[ Back to top ]