Fターム[5J022CF03]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 積分器(ランプ電圧発生) (152)

Fターム[5J022CF03]に分類される特許

21 - 40 / 152

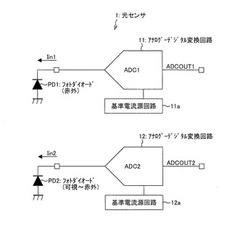

光センサおよびそれを備えた携帯電話ならびにデジタルカメラ

【課題】低照度から高照度までの入力に対してリニアな出力を得ることが可能であるとともに、フォトダイオードの出力電流の温度依存性を補正することができる光センサを実現する。

【解決手段】光センサ(1)において、第1のアナログ−デジタル変換回路(11)に、第1のフォトダイオード(PD1)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第1の基準電流源が備えられ、第2のアナログ−デジタル変換回路(12)に、第2のフォトダイオード(PD2)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第2の基準電流源が備えられ、第1の基準電流源を用いて出力された第1の検出結果(ADCOUT1)と、第2の基準電流源を用いて出力された第2の検出結果(ADCOUT1)とから、第2のフォトダイオード(12)による可視波長域の受光強度を検出することによって照度を測定する。

(もっと読む)

半導体装置

【課題】AD変換器及びそれを用いた電子回路において、回路規模を縮小及び消費電力を低減することを課題の一とする。

【解決手段】参照電圧に応じた第1の周波数を出力する第1の発振器と、入力電圧に応じた第2の周波数を出力する第2の発振器と、第1の周波数を測定する第1のカウンタと、第2の周波数を測定する第2のカウンタと、第1の周波数の測定結果と第2の周波数の測定結果を比較して、入力電圧に応じたデジタル値を出力する比較器とを有するAD変換器である。

(もっと読む)

AD変換回路、光電変換装置、撮像システム、およびAD変換回路の駆動方法

【課題】より簡単な回路構成で高分解能な変換が実現できるAD変換回路を提供する。

【解決手段】参照信号とアナログ信号とを比較する比較部107と、増幅部106と、を有し、1段階目のAD変換によってi−bit(i≧2の整数)のデジタルコードを得、2段階目のAD変換によってj−bit(j≧2の整数)のデジタルコードを得ることで、前記アナログ信号を(i+j)−bitのデジタル信号に変換するAD変換回路であって、該AD変換回路は、前記1段階目のAD変換において、前記比較部で前記アナログ信号と前記参照信号との比較を行い、前記増幅部は、前記アナログ信号と、前記i−bitのデジタルコードに対応するアナログ信号と、の差分を増幅した増幅残差信号を出力し、前記2段階目のAD変換において、前記増幅残差信号を前記参照信号と前記比較部で比較する。

(もっと読む)

AD変換器、ダイヤル式入力装置、及び抵抗−電圧変換回路

【課題】ポテンショメータの抵抗値や電流源による電流が変化した場合でも、製造バラツキや使用環境等の影響を受けないデジタル出力を得ることができるAD変換器を提供する。

【解決手段】被第1積分電圧Vinが入力されているときに被第1積分電圧Vinと基準電圧Vcomとの差分の電圧を積分する第1積分を行い、第1積分の実行後、被第2積分電圧Vrefが入力されているときに被第2積分電圧Vrefと基準電圧Vcomとの差分の電圧を積分する第2積分を行い、少なくとも第2積分に応じた積分電圧を出力する積分器12と、第2積分を開始してから積分電圧と基準電圧Vcomとが等しくなるまでの時間を計測して出力するコンパレータ13及びLOGIC14と、を備えた2重積分型ADコンバータ10と、被第1積分電圧Vinを変化させるとともに、被第2積分電圧Vref及び基準電圧Vcomを変化させる抵抗−電圧変換回路30と、を備える。

(もっと読む)

A/D変換装置、A/D変換方法、並びにプログラム

【課題】消費電力を低減させる。

【解決手段】時間とともに電圧値が線形に変化するランプ波形の参照電圧と入力電圧とを比較する比較器と、比較器の出力が反転したことをトリガとして動作開始もしくは動作停止し、クロック信号の周期毎に計数する上位ビットカウンタと、位相の異なる複数のクロック信号を用いて比較器の出力が反転したタイミングで位相情報をラッチしその値をデコードすることでクロック信号周期より分解能が高い下位ビットを出力する時間量子化器を有する積分型A/D変換装置において、照度に応じて分解能を減じることで、位相情報を持つクロック信号を停止させ、消費電流を減らす。本発明は、イメージセンサに適用できる。

(もっと読む)

AD変換回路および撮像装置

【課題】誤カウントの発生を抑制することができるAD変換回路および撮像装置を提供する。

【解決手段】上位カウンタ101は、遅延回路から出力される第1の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ103から出力されるカウントクロックに基づいてカウントを行って第1の上位計数値を取得する。第1の上位計数値を構成する各ビットの値が反転された後、上位カウンタ101は、遅延回路から出力される第2の下位位相信号を構成する1つの出力信号をカウントクロックとしてカウントを行い、さらに下位カウンタ103から出力されるカウントクロックに基づいてカウントを行って第2の上位計数値を取得する。また、上位カウンタ101は、カウントクロックの切換えの際に保持している上位計数値を保護するデータ保護機能を有する。

(もっと読む)

アナログデジタル変換器

【課題】広い範囲のアナログ信号を高精度でデジタル信号に変換するためには前段に可変ゲインアンプが必要であるが、このため高価なアナログ部品が必要であった。本発明は簡単な構成でゲインを可変できるアナログデジタル変換器を提供することを目的にする。

【解決手段】アナログ信号とフィードバック信号の差分信号を積分し、この積分信号をそのレベルに対応するデューティ比を有する信号に変換して、この信号のデューティ比をゲイン設定器で(1/ゲイン)に変換した信号をデューティ/レベル変換してフィードバック信号を生成するようにした。高価なアナログ部品を使用しなくてもよい。

(もっと読む)

A/D変換装置

【課題】積分器の前段に増幅回路を追加することなく、ダイナミックレンジの広範囲化および高精度化が可能なA/D変換装置を提供する。

【解決手段】積分器1の出力電圧Voutを基準電圧Vrefと比較するコンパレータ2と、コンパレータ2の後段に設けられクロックパルスをカウントするカウンタ3と、カウンタ3のカウント値を積分器1の出力電圧Voutの振幅に応じたディジタル値に変換して出力する変換回路4と、積分器1の出力電圧Voutの振幅に応じたディジタル値を出力する比較型A/D変換器5と、選択回路6と、タイミング制御回路7とを備える。タイミング制御回路7は、積分器1を積分動作させる積分期間の終了直前の所定時までにコンパレータ2の出力Vcpが反転しない場合には、比較型A/D変換器5にA/D変換を行わせてディジタル値を選択回路6から出力させ、反転した場合には、変換回路4から出力されるディジタル値を選択回路6から出力させる。

(もっと読む)

AD変換装置およびDA変換装置

【課題】デジタル処理の負担を少なくする。

【解決手段】出力データの上位側から1ビットずつ特定される対象ビット毎に、対象ビットの重みに応じたパルス幅またはパルス数のパターン信号を発生するパターン発生部と、パターン信号の発生毎に対象ビットの値を判定するための判定値に応じてパターン信号を積分し、パターン信号毎の積分値を累積した参照信号を出力する積分部と、各々のパターン信号の発生が終了する毎に、入力信号と参照信号とを比較する比較部と、各ビットの値を対応するパターン信号の発生が終了した後の比較結果に応じた値とした出力データを出力する出力部と、を備えるAD変換装置を提供する。

(もっと読む)

A/D変換器

【課題】より一層の高精度化が可能なA/D変換器を提供する。

【解決手段】制御回路(制御手段)5は、積分器1において入力電圧Vinを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第1の二重積分と第1の基準電圧(グラウンド電圧)VAGNDを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第2の二重積分とが選択的に行われるように入力切替部2を制御する機能を有する。第1の二重積分における第2積分期間に対応したカウント値からなる第1のカウント値と第2の二重積分における第2積分期間に対応したカウント値からなる第2のカウント値とが入力されるディジタル回路7を備える。ディジタル回路7は、第1のカウント値ごとに、第1のカウント値の前後1つずつの第2のカウント値の平均値を第1のカウント値から減算した差分値を求めてディジタル値として出力する機能を有する。

(もっと読む)

A/D変換器

【課題】従来の四重積分型A/D変換器に比べて、精度の低下を防止しつつ単位時間当たりの変換回数を増やすことが可能なA/D変換器を提供する。

【解決手段】積分器1において入力電圧Vinを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第1の二重積分と第1の基準電圧(グラウンド電圧)VAGNDを第1積分期間だけ積分した後に参照電圧VREFを第2積分期間だけ積分する第2の二重積分とが選択的に行われる。ディジタル回路7は、第1の二重積分における第2積分期間に対応した第1のカウント値を被減数、第2の二重積分における第2積分期間に対応した第2のカウント値を減数として被減数から減数を減算して得た差分値をディジタル値として出力する機能を有し、差分値を求めるにあたり、第2のカウント値を時系列で入力される2つの第1のカウント値に対する減数として共用する。

(もっと読む)

二重積分型A/D変換器

【課題】両極性の入力電圧を変換可能であり、且つ、ディジタル値として異常値が出力されるのを防止することが可能な二重積分型A/D変換器を提供する。

【解決手段】両極性の入力電圧を変換可能な二重積分型A/D変換器であって、入力電圧Vinを積分する第1積分期間が終了する直前において積分器1の出力電圧Voutが基準電圧VAGNDよりも高い第1の比較基準電圧VHと基準電圧VAGNDよりも低い第2の比較基準電圧VLとの範囲VH〜VL内にあり、且つ、基準電圧VAGNDよりも高い第1の参照電圧VREF+あるいは基準電圧VAGNDよりも低い第2の参照電圧VREF-を積分する第2積分期間において一定周期のクロックパルスをカウントし積分器1の出力電圧Voutが基準電圧VAGNDに戻るまでのカウント値をディジタル値として出力するカウンタ4がオーバーフローしたときに、カウンタ4のカウント値をゼロにリセットさせる補正手段8を備えている。

(もっと読む)

二重積分型A/D変換器

【課題】両極性の入力電圧を変換可能であり、且つ、カウンタのカウント値が異常値であるか否かを判定することが可能な二重積分型A/D変換器を提供する。

【解決手段】第1積分期間の終了時におけるコンパレータ3の出力に基づいて積分器1の出力電圧Voutの基準電圧VAGNDに対する大/小に基づく極性を“H”/“L”として判定して出力するとともに極性判定結果に応じて入力切替部2を制御する制御回路(制御部)5と、積分器1の出力電圧Voutを基準電圧VAGNDよりも高い第1の比較基準電圧VH、基準電圧VAGNDよりも低い第2の比較基準電圧VLそれぞれと比較して各比較結果ごとに大/小に応じて“H”/“L”の出力を発生する比較手段7とを備える。ディジタル回路8は、カウンタ4のカウント値が最大値であり、且つ、制御回路5での極性判定結果と比較手段7による両方の比較結果とが異なるときに、カウント値を異常値と判定する異常判定手段を有する。

(もっと読む)

多チャネル量子化器および量子化の方法

【課題】多チャネル量子化器および量子化の方法を提供する。

【解決手段】1つの量子化器は、入力アナログ信号を受け取る複数のチャネル102と、各チャネル内の演算増幅器104と、演算増幅器に接続された比較器106とを有するアナログ−デジタル変換器(ADC)100を含む。ADCはさらに、比較器に接続され、比較器から受け取った比較器信号に基づいて出力を発生するように構成された、各チャネル内の論理回路108を含む。ADCはまた、複数のチャネルに接続され、時間的に変化する基準信号を供給するように構成されたランプ発生器116を含む。

(もっと読む)

AD変換方法およびAD変換装置

【課題】AD変換装置を同一チップ上に搭載した固体撮像装置において、回路規模、消費電力、消費電流、インタフェース用配線数、ノイズなどの問題を解消する。

【解決手段】電圧比較部252とカウンタ部254とを有するカラムAD回路25を垂直信号線19ごとに設ける。電圧比較部252は、行制御線15ごとに垂直信号線19を経由し入力される画素信号と参照電圧RAMPとを比較し、リセット成分や信号成分の各大きさに対応した時間軸方向に大きさを持つパルス信号を生成する。カウンタ部254は、電圧比較部252の比較完了までパルス信号の幅をクロックCK0でカウントし、比較完了時点のカウント値を保持する。通信・タイミング制御部20は、1回目は電圧比較部252でリセット成分を比較処理しカウンタ部254がダウンカウントする一方、2回目は電圧比較部252で信号成分を比較処理しカウンタ部254がアップカウントするように制御する。

(もっと読む)

固体撮像装置

【課題】AD変換の分解能を変更する際に、変更が必要なパルスのみの変更を、より簡単な構成で行うことができるようにする。

【解決手段】AD変換の分解能のモードが9ビットモードである場合には、デコーダ102は、Hカウンタ104のみを動作させる。AD変換の分解能のモードが10ビットモードまたは12ビットモードである場合には、デコーダ102は、Hカウンタ104のカウント値がレジスタ101に記憶されている開始カウント値となったときに、Hカウンタ104のカウント動作を停止させるとともに、アイドルカウンタ106のカウントを開始させ、アイドルカウンタ106のカウント値がレジスタ101に記憶されたカウント数となったときにHカウンタ104のカウントを再開させる。本発明は、例えば、カラムAD変換方式を採用したイメージセンサに適用できる。

(もっと読む)

アナログ−デジタル変換器、受信器、及び無線通信装置

【課題】

電流モード入力を有するアナログ−デジタル変換器(ADC)を備えた受信器が提供される。

【解決手段】

受信器は、変調された無線信号を復調して電流モードベースバンド信号を生成するように構成されたダウンコンバータ228と、該電流モードベースバンド信号をデジタル出力信号に変換するように構成されたアナログ−デジタル変換器(ADC)224とを有する。ダウンコンバータ228は介在フィルタ素子なくADC224に接続される。

(もっと読む)

ハイブリッド・アナログ/デジタル変換器、イメージセンサおよび複数のデジタル信号を提供するための方法

【課題】パワーおよびエリア比により良い変換率を有するアナログ/デジタル変換器を提供する。

【解決手段】ハイブリッド・アナログ/デジタル変換器100は、複数の変換回路101a〜101nを含む。それぞれの変換回路は、逐次近似変換の結果として、デジタル信号103a〜103nの第1の数のビットを得るために逐次近似変換を実行することによって、さらに、デジタル信号の第2の数のビットを得るために共通可変基準電圧105に基づいて傾斜変換をその後に実行することによって、アナログ入力信号104a〜104nに基づいてデジタル信号を提供するように構成され、第2の数のビットは、アナログ入力信号および逐次近似変換の結果間の残差に対応する。ハイブリッド・アナログ/デジタル変換器は、複数の変換回路のそれぞれの変換回路に共通可変基準電圧を提供するように構成される共通可変基準電圧プロバイダ102をさらに含む。

(もっと読む)

比較回路及び信号変換装置

【課題】アナログデジタル変換の分解能を向上させる比較回路及び信号変換装置を提供する。

【解決手段】比較回路22は、コンパレータ22aが、第1の入力端子に接続される第1の電圧源により、第1の入力端子に印加される電圧と、第2の入力端子に入力される入力信号の電圧とを比較する。コンデンサ22bが、第1の入力端子に一方の端子が接続され、第1の電圧源側に他方の端子が接続される。スイッチ22cが、第1の入力端子への基準電圧源22の接続を選択的に遮断する。スイッチ22dが、コンデンサ22bの他方の端子への第1の電圧源の接続を選択的に遮断する。基準電圧源22fが、コンデンサ22bの他方の端子に接続される。スイッチ22eが、基準電圧源22fによりコンデンサ22bの他方の端子に印加される電圧を選択的に遮断する。

(もっと読む)

二重積分型AD変換器および積分型AD変換器

【課題】本発明によれば、クロックパルス発生器の周波数が比較的低い場合にも、自身の積分回路のコンデンサの静電容量を、ICに内蔵可能となる程度に小さくすることが可能な二重積分型AD変換器を実現することができる。

【解決手段】本発明は、測定電圧またはこの測定電圧と逆極性の標準電圧のいずれかを選択し出力するセレクタと、このセレクタの出力を積分する積分回路と、クロックパルスを発生するクロックパルス発生器とを有し、前記積分回路の積分値が予め定められた値となるまでの時間を前記クロックパルスで計測し、計測した時間に基づいてアナログデジタル変換する二重積分型AD変換器において、前記クロックパルスに基づいてこのクロックパルスよりもパルス幅の小さい微小パルスを生成する微小パルス発生回路と、前記セレクタと前記積分回路との間に設けられ、前記微小パルスを入力し、そのパルス幅に相当する期間においてのみ前記セレクタと前記積分回路とを接続するスイッチと、を備えたことを特徴とする。

(もっと読む)

21 - 40 / 152

[ Back to top ]