Fターム[5J024DA04]の内容

フィルタ、等化器 (7,537) | 構造 (2,588) | コンデンサを有するもの (811) | 支持基板等に電極を形成するもの (380)

Fターム[5J024DA04]の下位に属するFターム

他方の電極がコイル、抵抗等をかねるもの (81)

Fターム[5J024DA04]に分類される特許

1 - 20 / 299

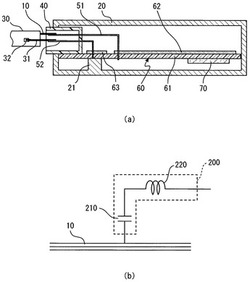

ノイズフィルタ及びノイズフィルタが搭載された電子装置

【課題】フィルタ特性の自由度が高いノイズフィルタ及びノイズフィルタが搭載された電子装置を提供すること。

【解決手段】金属ケース20と、金属ケース20内に収納されたIC70と、金属線11と金属線11を被覆する誘電体12とを含み金属線11がIC70に電気的に接続された配線10と、金属ケース20の外部において誘電体12の表面に取り付けられるものであり金属線11及び誘電体12と共にキャパシタを構成する金属からなるキャパシタ構成部材30と、インダクタを構成するものでありキャパシタ構成部材30と金属ケース20とを電気的に接続するフィルタ用配線31,52,63とを備える。そして、キャパシタ210とインダクタ220とは、直列に接続されて、配線10に対して並列に接続されたノイズフィルタ200を構成する。

(もっと読む)

電子部品

【課題】回路設計において高い自由度を得つつ、鳴きを低減することができる電子部品を得る。

【解決手段】互いに対向する底面S2及び上面S1、並びに、互いに対向する第1の端面S3及び第2の端面S4を有する直方体状の積層体11と、誘電体層と共に積層されることによってコンデンサを形成し、かつ、第1の端面S3又は第2の端面S4に引き出されている複数のコンデンサ導体30a〜30d,32a〜32dと、第1の端面S3及び底面S2に跨って設けられ、かつ、コンデンサ導体32a〜32dと接続されている第1の外部電極12aと、第2の端面S4及び底面S2に跨って設けられ、かつ、コンデンサ導体30a〜30dと接続されている第2の外部電極12bと、を備える電子部品。底面S2と該底面S2に最も近いコンデンサ導体32dとの間の距離H5は、上面S1と該上面S1に最も近いコンデンサ導体30aとの間の距離よりも大きい。

(もっと読む)

静電容量素子、及び共振回路

【課題】電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、電気的特性を向上させることを目的とする。また、その静電容量素子を用いることにより、信頼性に優れた共振回路を提供することを目的する。

【解決手段】誘電体層3と、誘電体層3を介して積層され、静電容量をなす電極本体の中心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサにより容量素子本体2を構成する。この容量素子本体2では、該2つ以上のコンデンサが内部電極の積層方向に直列接続される。そして、容量素子本体2の側面に、静電容量をなす電極本体に電気的に接続された外部端子20〜23を形成する。

(もっと読む)

静電容量素子、及び共振回路

【課題】静電容量素子において、焼成時に発生する残留応力を利用することで誘電率を向上させ、静電容量を増大する。

【解決手段】容量素子(可変容量素子1)は、誘電体層と、誘電体層を挟んで形成される少なくとも一対の内部電極10とを備える容量素子本体2と、容量素子本体2の側面に形成され、内部電極10に電気的に接続される外部端子3,4とを備える。そして、誘電体層5及び内部電極の線膨張係数の違いに起因して発生する応力が、誘電体層5と誘電体層5を挟む一対の内部電極10とで構成されるコンデンサCの中心に集中するように構成されている。

(もっと読む)

帯域通過フィルタ

【課題】特別な素子を設けなくても、インピーダンスの不整合を抑えることができる帯域通過フィルタを提供する。

【解決手段】本発明に係る帯域通過フィルタは、入力端子T1と、出力端子T2と、一端が接地され、入力端子T1と出力端子T2の間に配置されたLC並列共振器LC2、LC3、LC4と、LC並列共振器LC2、LC3、LC4と入力端子または出力端子との間に配置され、LC並列共振器LC2、LC4と電磁界結合するように設けられるトラップ共振器LC1、LC5と、を備えることを特徴とする。

(もっと読む)

ローパスフィルタ

【課題】Q値の低下を抑制しつつ、コイルのインダクタンス値を大きくすることができるローパスフィルタを提供することである。

【解決手段】積層体12は、複数の絶縁体層16が積層されて構成され、かつ、z軸方向の負方向側において実装面を有している。外部電極は、積層体12の下面に設けられており、接地される。コイルL10は、積層体12に内蔵され、かつ、z軸方向に延在する中心軸を有する螺旋状のコイルである。ビアホール導体v15〜v21は、コイルL10のz軸方向の正方向側の端部からz軸方向の負方向側に向かって延在している。外部電極とコイルL10のz軸方向の正方向側の端部とは、ビアホール導体v15〜v21を介して電気的に接続されている。

(もっと読む)

LCモジュールおよびDC−DCコンバータ

【課題】寄生インダクタンスが小さく、かつ平坦性を確保することができるLCモジュールを提供する。

【解決手段】実装用基板31に直接コンデンサを搭載することで、インダクタ11上部から実装用基板31までの配線が不要となり、寄生インダクタンスの影響がなくなる。また、実装用基板31に実装される側のコンデンサには、1チップ内に複数のコンデンサが内蔵されたコンデンサアレイ21を用い、平坦性を確保する。さらに、コンデンサアレイの各端子電極のうち、Vin、Vout、およびGND以外の端子電極をLX(スイッチング素子に接続する側のインダクタの端部)とし、LXをVoutに隣接および対向しない箇所に配置する。これにより、LXから遠い側のコンデンサを出力コンデンサとして機能させることになり、LXに現れるスイッチングノイズがVoutに漏れ出すことを防止することができる。

(もっと読む)

LC複合部品及びLC複合部品の実装構造

【課題】実装方向性がなく、インダクタンス成分を増加させることができるLC複合部品及びLC複合部品の実装構造を提供する。

【解決手段】LC複合部品は、コンデンサ部とインダクタ部とは積層方向に交互に積層され、かつコンデンサ部とインダクタ部とのいずれか一方が第1の素体主面側と、第2の素体主面側との両方に配置され、第1のコイル線路部と第2のコイル線路部とは、第1の外部導体群の第1の素体端面寄りの外部導体と第2の素体端面寄りの外部導体との間にある外部導体、又は第2の外部導体群の第1の素体端面寄りの外部導体と第2の素体端面寄りの外部接続導体との間にある外部導体に接続され、第1のコイル線路部及び第2のコイル線路部が積層方向へ螺旋状に巻回されるコイルとなる。

(もっと読む)

電子部品

【課題】所望の容量値を有するコンデンサを内蔵している電子部品を提供することである。

【解決手段】積層体12は、複数の絶縁体層16が積層されてなる。ランド電極14a,14cは、積層体12の底面に設けられている。内部導体18l,18mはそれぞれ、積層体12内においてランド電極14a,14cと絶縁体層16iを介して対向し、ランド電極14a,14cの面積よりも大きな面積を有し、かつ、z軸方向から平面視したときに、ランド電極14a,14cを包含している。コンデンサ導体19は、コンデンサ導体18l,18mよりもz軸方向の正方向側に設けられ、かつ、コンデンサ導体18l,18mと対向している。

(もっと読む)

フィルタ回路

【課題】誘電体層間に積層ずれが生じた場合に及ぼすフィルタ特性への影響を抑制することができるフィルタ回路を提供する。

【解決手段】BPFは、複数の誘電体層が積層された積層体からなり、直列接続されたインダクタL1及びインダクタL2と、インダクタL1,L2の接続点及びグランド電位それぞれに接続されたインダクタL3とを備えている。インダクタL1は、誘電体層PL1,PL2,PL3に設けられた開ループ状の電極パターン101A,102A,103Aが積層体の積層方向に重畳して形成されている。インダクタL2及びインダクタL3も、それぞれ誘電体層PL1,PL2,PL3に設けられた電極パターン101B,102B,103B及び電極パターン101C,102C,103Cが積層方向に重畳して形成されている。

(もっと読む)

積層型共振器及び積層型共振器の製造方法

【課題】小型で低損失の改良された積層型共振器を提供する。

【解決手段】積層型共振器10は、上面に複数の凹部がそれぞれ形成された基板20と、前記凹部に設けられ、入力端子電極12と電気的に接続された第1インダクタ下部電極32と、一部が前記凹部に設けられ、接地電極16と電気的に接続された第1、第2コンデンサ下部電極34、36と、前記凹部に設けられ、出力端子電極14と電気的に接続された第2インダクタ下部電極38と、前記基板上に形成された誘電体層24と、前記誘電体層上に、前記第1インダクタ下部電極に電気的に接続されるとともに、一部分が前記第1コンデンサ下部電極と対向するように形成された第1上部電極48と、前記誘電体層上に、前記第2インダクタ下部電極に電気的に接続されるとともに、一部分が前記第2コンデンサ下部電極と対向するように形成された第2上部電極50と、を備える。

(もっと読む)

積層型共振器及び積層型共振器の製造方法

【課題】小型で低損失の改良された積層型共振器を提供する。

【解決手段】積層型共振器10は、上面に複数の凹部が形成された基板20と、前記凹部に設けられ、入力端子電極12と電気的に接続された第1インダクタ下部電極32と、一部が前記凹部に設けられ、接地電極16と電気的に接続された第1、第2コンデンサ下部電極35、36と、前記凹部に設けられ、出力端子電極14と電気的に接続された第2インダクタ下部電極38と、前記基板上に形成された誘電体層24と、前記誘電体層上に、前記第1インダクタ下部電極に電気的に接続されるとともに、一部分が前記第1コンデンサ下部電極と対向するように形成された第1上部電極48と、前記誘電体層上に、前記第2インダクタ下部電極に電気的に接続されるとともに、一部分が前記第2コンデンサ下部電極と対向するように形成された第2上部電極50と、を備える。

(もっと読む)

高周波回路、高周波部品およびそれらを用いた通信装置

【課題】 NF(雑音指数)が小さく、受信感度の向上と、通過帯域外での高減衰量を得ながら、低消費電力の高周波回路を得る。

【解決手段】 増幅器の入力段に接続された第1の帯域通過フィルタと、増幅器の出力段に接続された第2の帯域通過フィルタのどちらか一方が、通過帯域の低周波数側に共振点を有する容量性の帯域通過フィルタであり、他方が通過帯域の高周波数側に共振点を有する、誘導性の帯域通過フィルタである高周波回路。

(もっと読む)

積層セラミック電子部品およびその製造方法

【課題】内部電極の隣り合う露出端の間隔が広くても、複数の内部電極の露出端間を接続するように連続した、外部電極の少なくとも一部としてのめっき膜を形成することを可能にする。

【解決手段】複数のセラミック層95および複数の内部電極91〜93を備え、複数の内部電極の各一部が露出している、部品本体2として、複数の内部電極の隣り合う露出端間に位置するセラミック層95の端面に、内部電極に含まれる導電成分が拡散して形成された導電領域96〜98が存在しているものが作製される。セラミック層は、ガラス成分を10重量%以上含むガラスセラミックからなることが好ましい。外部電極3〜6を形成するため、内部電極の露出端および上記導電領域をめっき析出の核としてめっき成長させることによって、めっき膜を部品本体2上に直接形成する。

(もっと読む)

積層型フィルタ

【課題】減衰特性の調整が容易で、かつグランドからのノイズの戻りを防止できる積層型フィルタを提供する。

【解決手段】積層型フィルタ1では、互いに磁気結合する一対のコイル部11,11間に、グランドには接続されないキャパシタ部12,12が接続されている。このような構成により、この積層型フィルタ1では、コイル部11の巻数を変化させることに加え、キャパシタ部12,12の静電容量を変化させることによっても減衰特性を変化させることができる。また、キャパシタ部12,12がグランドに接続されないので、グランドからのノイズの戻りを防止できると共に、グランドを通って信号が漏れてしまうことを防止でき、特定の周波数における減衰特性のピークを急峻なものとすることができる。

(もっと読む)

積層型フィルタ

【課題】減衰特性の調整が容易で、かつグランドからのノイズの戻りを防止でき、さらに、コイル部で形成される磁束の流れの阻害を抑制できる積層型フィルタを提供する。

【解決手段】積層型フィルタ1では、一対のコイル部11,11間に、グランドには接続されないキャパシタ部12,12が接続されている。また、キャパシタ部12,12がグランドに接続されないので、グランドからのノイズの戻りを防止できると共に、特定の周波数における減衰特性のピークを急峻なものとすることができる。また、積層型フィルタ1では、キャパシタ部12,12の電極パターン18a,18bが、コイル部11,11の導体パターン16a〜16hの中心軸Aに重ならないように配置されている。これにより、コイル部11,11で形成される磁束の流れがキャパシタ部12,12で阻害されることを抑制できる。

(もっと読む)

コモンモードノイズフィルタ

【課題】本発明は、コモンモードノイズおよびノーマルモードノイズを広い周波数帯域で大きく減衰させることができるコモンモードノイズフィルタを提供することを目的とするものである。

【解決手段】本発明のコモンモードノイズフィルタは、第1のコイル導体11と第2のコイル導体12とを接続する第1のローパスフィルタ部15と、第3のコイル導体13と第4のコイル導体14とを接続する第2のローパスフィルタ部16を形成し、さらに、この第1、第2のローパスフィルタ部15、16を、所望の周波数において、第1のコモンモードフィルタ17と第1、第2のローパスフィルタ部15、16との接続点の位相を、第2のコモンモードフィルタ18と第1、第2のローパスフィルタ部15、16との接続点の位相よりも0度より大きくかつ90度以下の位相量で変化させることができる位相調整機能をもたせるようにしたものである。

(もっと読む)

積層型電子部品及び電子部品の実装構造

【課題】低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品を提供する。

【解決手段】フェライトビーズインダクタ12,13は、磁性体層24と内部電極25a〜25dとが積層されるフェライトビーズ素体18と、フェライトビーズ素体18の第1及び第2の側面18c,18dに配置される第1及び第2の外部電極19,20とを備えている。内部電極25a〜25dは、長辺よりも短い短辺の方向に伸びて第1及び第2の外部電極19,20に接続される。また、フェライトビーズ素体18は、磁性体層24上において内部電極を形成可能な内部電極領域S内に、積層方向に隣接する磁性体層24同士が接合するための空隙27a〜27c(接合部)を有している。

(もっと読む)

積層型電子部品及び電子部品の実装構造

【課題】低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品を提供する。

【解決手段】フェライトビーズインダクタ12,13は、磁性体層24と内部電極25a〜25hとが実装基板に対して略垂直になるように主面18aの長辺方向に積層されているフェライトビーズ素体18と、フェライトビーズ素体18の主面18bに互いに離間して配置される第1及び第2の外部電極19b,20bとを備えている。内部電極25a〜25hは、主面18aの短辺方向に伸びる主電極部31と、主電極部31を第1及び第2の外部電極19b,20bそれぞれに接続する引き出し電極部33,35とを有し、主面18a,18bの対向方向において主電極部31の幅t1がフェライトビーズ素体18の厚みTの50%以上の長さとなっている。

(もっと読む)

電子部品および電子装置

【課題】 所望する電気的特性が変化することを抑制した、電子部品を供給することにある。

【解決手段】 複数の絶縁体層5a〜5iが積層された直方体状の積層体2と、積層体2の積層方向に沿った四側面のうち一側面2cに設けられた外部接続端子3と、外部接続端子3と電気的に接続され、絶縁体層5間に設けられた回路パターン6とを備えていることから、回路パターン6と配線基板の複数のランドとは互いに広い面積で対向する位置関係ではなくなる。その結果、回路パターン6と複数のランド間で不要な容量の発生を抑制でき、所望の電気的特性を得ることが可能な電子部品1を提供することができる。

(もっと読む)

1 - 20 / 299

[ Back to top ]