Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

261 - 280 / 321

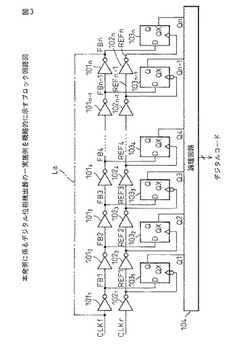

デジタル位相検出器

【課題】 従来、デジタル位相検出器における位相検出限界は、遅延素子の遅延時間により決定されるため、例えば、PLL回路に低ジッタ特性が要求される場合には、全デジタルPLL回路は不適当であった。

【解決手段】 第1のクロックCLKfを遅延する複数の第1の遅延素子1011〜101nと、第2のクロックCLKrを遅延する複数の第2の遅延素子1021〜102nと、前記第2の遅延素子により順次遅延された前記第2のクロックREF1〜REFnに従って、前記第1の遅延素子により順次遅延された前記第1のクロックFB1〜FBnを取り込み、相対的な位相関係を表すデジタル値Q1〜Qnを保持する複数のデータ保持回路1031〜103nと、を備えるように構成する。

(もっと読む)

ダイレクトチャージ型スイッチト・キャパシタ回路を含む電気回路

【課題】スイッチト・キャパシタ回路における寄生容量の影響を抑制する。

【解決手段】 キャパシタCの第1の端子に入力信号を供給し、第2の端子を基準電位に維持させることによってキャパシタCに入力信号の強度に応じた電荷を蓄積させる第1のモードと、キャパシタCの第1の端子をオペアンプ50bの出力端子TbOUTに接続し、第2の端子をオペアンプ50bの反転入力端子Tb(−)に接続する第2のモードとを選択可能とするスイッチング素子Toa,Tia,Tob,Tibとを含むメモリ単位52を少なくとも1つ備え、メモリ単位52に含まれるキャパシタCは、半導体基板の表面のウェル、ウェル上に形成された絶縁膜及び電極層とによって構成され、電極層をキャパシタの第1の端子とし、ウェルをキャパシタの第2の端子とすることによって上記課題を解決することができる。

(もっと読む)

集積化シリアルデータデコーダ

【課題】集積化シリアルデータデコーダを提供する。

【解決手段】本発明は、コンデンサを含まないシリアルデータデコーダを提供し、シリアルデータデコーダを集積回路に設計し、いかなる外部装置も必要としない。本発明の集積化可能なシリアルデータデコーダは、クロック生成器と、周期検出器と、チャネルデコーダと、からなり、コンデンサは含まない。復調されたシリアルデータを入力し、シリアルデータを、周期的に、繰り返し、並列データに転換する。

(もっと読む)

ノイズフィルタ及びフィルタリング方法

【課題】 本発明は、ノイズ除去時間をハードウエアにより決定し、プロセッサが使用される環境に最適なノイズ除去時間を決定することが出来るノイズフィルタ及びフィルタリング方法を提供することを課題とする。

【解決手段】 選択回路18はフィルタの段数が1段の信号Xをフィルタ出力信号OUTとして選択出力している。波形チェック部18は、フィルタ出力信号OUT上のパルス幅が、最小パルス幅指定レジスタ20の設定値より小さいとき、選択回路19にフィルタの段数が2段の信号Y、3段の信号Zを選択出力させる。段数の最適化処理が終了するとフィルタ値最適化完了フラグ(STATUS BIT)21をセットする。

(もっと読む)

多相デジタルサンプリングのための装置および方法

【課題】入力信号周波数と基準信号周波数との間の関係を決定する方法および装置を提供する。

【解決手段】本システムは、基準信号から複数の内部基準信号を得る。内部基準信号は、レベル検出回路20aに与えられる。レベル検出回路20aは、入力信号をある期間内にある回数サンプリングする。これらのサンプルに関連付けられた値は、前回の期間からのサンプルの1つの値と同様に記憶される。記憶されたサンプルの相関が取られ、入力信号周波数と基準信号周波数との間の関係が得られる。

(もっと読む)

半導体集積回路と半導体集積回路設計方法

【課題】 誤動作の虞の無いクロックゲーティング手法が適用されたクロック供給回路を含む半導体集積回路を提供すること。

【解決手段】 複数のバッファ101からなるバッファツリーを用いてレジスタとなる各々のフリップフロップ104a〜104dにクロック信号CLKを供給するクロック供給回路において、クロック信号CLKの供給を制御するためのイネーブル論理105を与えるためのクロックゲーティング回路を、各フリップフロップ104a〜104dと同じ個数のクロックゲーティング回路104a〜104dに複製し、これらを各フリップフロップ104a〜104dに物理的に隣接して配置し、各クロックゲーティング回路104a〜104dの出力を各々のフリップフロップ104a〜104dに直接接続させたもの。

(もっと読む)

周波数逓倍装置

【課題】出力信号の精度を維持することが可能な高精度の周波数逓倍装置を低コストに提供する。

【解決手段】第2実施形態では、基準信号PREFの1周期おきに出力されると共に論理反転の関係にある2つのカウント許可信号UCE1,UCE2を補正対象とし、同一構成の2つのカウンタ・データラッチ回路4a,4bを基準信号PREFの1周期分ずつずらして動作させる。そして、基準信号PREFの1周期毎に周波数制御データCD1〜CD12(c)の補正を繰り返すことにより、基準信号PREFの周波数を多相クロックR1〜R16の総数倍に逓倍した出力信号POUTを発生させる。そのため、出力クロックRCK(=R13)をカウントしてから、そのカウント値が周波数制御データCD1〜CD12(c)に反映され、新たな周波数制御データが生成されるまでに要する時間である補正遅延時間tは、基準信号PREFの1周期分の時間になる。

(もっと読む)

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

半導体デバイス

【課題】 クロックやデータの分配において、SKEWを小さくできるとともに、動作依存の消費電力(AC成分)を小さくでき、また、分配回路自身が発生するノイズを抑制できる。

【解決手段】 一又は二以上の回路ブロック10−1〜10−nを有するデジタル回路1aが搭載された半導体デバイスにおいて、クロックを分配するクロック配線20と、データを分配するデータ配線30とを備え、クロック配線20のクロック主経路21が、クロック分岐路22の各分岐点間に接続されたクロック用バッファ25を有し、データ配線30のデータ主経路31が、データ分岐路32の各分岐点間に接続されたデータ用バッファ35を有し、それらクロック用バッファ25及びデータ用バッファ35にBIAS信号を与えるバイアス配線40と、BIAS信号を生成する遅延ロックループ回路(DLL)60とを備えた。

(もっと読む)

位相同期ループ回路及び位相同期方法

【課題】 電源電圧のレベルが低くなっても高周波数の多様なクロック信号を発生することが可能な位相同期ループ及び方法を提供すること。

【解決手段】 位相同期ループ回路は外部クロック信号と帰還クロック信号を受信し、外部クロック信号の位相が帰還クロック信号の位相より先行するとアップ信号を発生し、外部クロック信号の位相が帰還クロック信号の位相より遅れるとダウン信号を発生する位相検出器と、アップ信号に応答して制御電圧が増加し、ダウン信号に応答して制御電圧を減少するループフィルタ回路と、制御電圧を受信してn(nは4以上の整数)個の内部クロック信号を直接発生する電圧制御発振器回路とを含むこともできる。また、位相同期ループ回路は少なくとも4個のループを含み制御電圧を受信して複数の内部クロック信号を発生する電圧制御発振器回路も含むことができる。

(もっと読む)

半導体集積回路

【課題】多雑音環境であったり、サンプリング周期に同期して雑音が発生しやすい状況下においても、その雑音信号を誤入力しない半導体集積回路を提供する。

【解決手段】半導体集積回路は、サンプリング部と、遅延部と、第1演算部と、第2演算部とを具備する。サンプリング部は、外部から入力される入力信号をクロック信号に同期してサンプリングし、第1信号として出力する。遅延部は、第1信号をクロック信号に基づいて遅延させ、第2信号として出力する。第1演算部は、第1信号と第2信号に基づいて、入力信号が所定の時間以上信号レベルが持続しているか否かを演算する。所定の時間以上信号レベルが持続するとき、第1演算部は、所定の時間以上持続する信号レベルを有する出力信号をクロック信号に同期して出力する。第2演算部は、入力信号と出力信号とに基づいて、サンプリング部を非同期に制御する。

(もっと読む)

クロック周波数制御装置

【課題】 入力クロックの周波数に対する出力クロックの周波数の比が分数であっても、周期が一定である出力クロックを小規模回路で生成するクロック周波数制御装置を提供する。

【解決手段】 クロック周波数制御装置100は、第1のクロックCK1の周波数と第2のクロックCK2の設定周波数比f2/f1を、約分した後の除算の商mと剰余rと分母dとして記憶する周波数比率記憶部1と、剰余rの累積加算値が分母d以上になることにその値からdを減算するとともに桁上げ信号を出力する累積加算部2と、商mを累積加算部2からの桁上げ信号とともに累積加算する累積加算部3と、CK2の周波数を計数するカウンタ5と、累積加算部3の出力とカウンタ5の出力の差分を算出する差分算出部6と、その差分値に応じて発振周波数を制御するための差分値評価部7Aと、差分値評価部7Aの制御により発振周波数が制御されるCK2出力用VCXO9とを有する。

(もっと読む)

パルス幅変調回路及び多相クロック生成回路

【課題】

周波数の微調整を行うことが可能なパルス幅変調回路及び多相クロック生成回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路は、基準クロックに基づいて多相クロック信号を生成する多相クロック生成手段と、入力データと、多相クロック信号とに基づいてパルス幅変調信号を生成するパルス幅変調信号生成手段とを備えたパルス幅変調回路であって、多相クロック生成手段は、位相ロックループ回路を有し、多相クロック信号のうち任意のクロック信号を選択し、帰還クロックとして前記位相ロックループ回路に出力するパルス幅変調回路である。このような構成によれば、多相クロック生成回路の生成する多相クロックのクロック周波数が変更可能となり、クロック周波数及びパルス周波数の微調整を行うことが可能となる。

(もっと読む)

オフセット補正回路

【課題】 頻繁なリフレッシュを必要とせず、小さな回路規模でオフセットばらつきを吸収してオフセット補正を行うことのできるオフセット補正回路を実現する。

【解決手段】 オペアンプ回路1において、スイッチ素子S1を閉じてスイッチ素子S2を開く。ラッチ回路DLはオペアンプ1aの出力電圧をラッチしてそれに応じたQ出力を行い、制御回路2aはオフセット補正用信号s1をオペアンプ1aのオフセット調整入力端子ORに入力する。それによってオフセット補正された出力電圧をさらにラッチ回路DLによりラッチし、残りのオフセットを補正するためにオフセット補正用信号s1を微調整していく。このようにして、そのときのラッチが何回目であるかに応じて重み付けされた補正量でオペアンプ1aの出力電圧のオフセットを量子化し、2値の論理信号として制御回路2a内に記憶する。

(もっと読む)

波形グリッチ防止方法

本発明におけるシステム開発目的は、発止させるパルス列の位相をグリッチやスプリアスパルスやデューティサイクルのスプリアス的変化なしで任意に変化させられるようにすることにある。この目的を達成すべく、本ゲート済周期波形発生システムにおいては、可調位相周期波形を発生させる発生器と、この周期波形の位相に基づき遅延イネーブル信号を提供するデバイスと、遅延イネーブル信号及び可調位相周期波形に基づきゲート済周期波形を発生させる論理素子と、を設け、遅延イネーブル信号によりゲート済周期波形をその不要変化なしで発止可能としている。  (もっと読む)

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

回路装置およびこれを備えた電子機器

【課題】 入力信号に対して基準電圧に基づいた処理を施して出力する回路装置に、基準電圧の切替機能を持たせることにより、安定した出力が得られる回路装置を提供する。

【解決手段】 外部より与えられる入力電圧と、互いに異なる複数の電圧値を含む基準電圧セットから選択された基準電圧とを比較するコンパレータ1と、入力電圧が昇圧の方向にて基準電圧に到達したことを検知すると前記基準電圧セットから当該基準電圧より低い電圧値を選択し、前記入力電圧が降圧の方向にて基準電圧に到達したことを検知すると前記基準電圧セットから当該基準電圧より高い電圧値を選択し、選択した電圧値をコンパレータ1の基準電圧として設定する基準電圧設定回路20を備えた回路装置である。

(もっと読む)

半導体装置

【課題】 タイミングマージンの改善を図った同期化回路を備えた半導体装置を提供する。

【解決手段】 第1導電型の第1と第2MOSの共通ソースと第1電位との間に第1導電型第3MOSを設け、第2電位と上記第1と第2MOSのドレインと間に第2導電型の第4と第5MOSを設け、上記第4と第5MOSに並列形態にゲートとドレインが交差接続された第2導電型の第6と第7MOSを設ける。上記第1MOSのゲートに入力信号を供給し、上記第2MOSのゲートを上記第1MOSのドレインに接続し、上記第3MOSのゲートにクロックを供給し、上記第4と第5MOSのゲートに上記クロックと同相クロックを供給して、上記第1と第2MOSのドレインから第1、第2信号を出力してRSフリップフロップ回路に伝える。

(もっと読む)

半導体集積回路

【課題】 クロックスキューを低減し、動作マージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】 遅延回路8による遅延時間DL1とクロックツリー11による遅延時間DL11との和が、遅延回路9による遅延時間DL2とクロックツリー12による遅延時間DL12との和と等しくなるように、遅延回路8,9の遅延時間DL1,DL2が調整される。このように、予め任意に遅延時間をプログラムすることができるプログラマブル遅延回路8,9を設けたことによって、機能ブロック3,4に供給される内部電源電圧V1,V2の差が大きい場合でも、機能ブロック3,4間のクロックスキューを低減することができる。したがって、低消費電力の半導体集積回路において、クロックスキューを低減することができ、動作マージンを十分に確保することが可能になる。

(もっと読む)

半導体集積装置

【課題】内部の機能切替における必要なクロックの切替にかかる煩雑さを解消し、外部から内部の機能切替の命令のみで精密なクロック設定を実現する半導体集積装置を提供する。

【解決手段】外部から入力される内部機能の切替の命令100の内容を判別し、特定の機能ブロック118に対して必要なクロックの周波数を判別するクロック周波数判定回路114と、切り替え前後の周波数の関係により、機能切り替えとクロック切り替えのタイミングを制御し、切り替えの状態を表す機能切替・クロック切替完了フラグ110を外部に出力するクロック切替制御回路113とを備えることにより、クロック切り替えの制御を外部から行う必要がなくなるようにした。

(もっと読む)

261 - 280 / 321

[ Back to top ]