Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

161 - 180 / 321

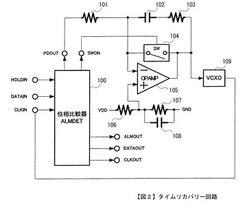

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

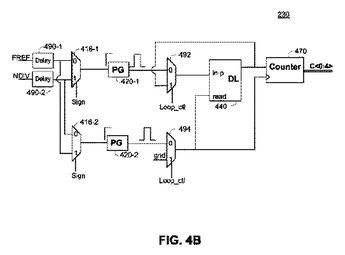

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinのデューティの変動に応じてパルス幅が増減するパルス信号Errと基準パルス幅を示すパルス信号Refとを出力するパルス信号生成回路1と、パルス信号Errまたはパルス信号Refのいずれかを選択的に出力するセレクタ2と、パルス信号Refの遷移がない場合はセレクタ2にパルス信号Refを選択させ、パルス信号Refの遷移がある場合にはセレクタ2にパルス信号Errを選択させるパルス信号遷移判定回路3と、セレクタ2から出力された信号の平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を表す検出信号Outとして出力する出力回路4とを備える。

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

位相調整回路

【課題】大きな位相ずれにも対応可能な位相調整回路を提供する。

【解決手段】基準となるクロック信号CLKeに同期して与えられる画像データDATAeとデータイネーブル信号DEeは、このクロック信号CLKeで動作するFF31,33,38,40で2クロック分遅延され、画像データDTeと共通のデータイネーブル信号DEとして出力される。位相調整の対象となるクロック信号CLKoに同期して与えられる連続する2つの画像データDATAoは、それぞれFF34,35によって2クロック周期の間保持される。FF34,35の保持データは、セレクタ37によっていずれか一方が選択出力され、基準となるクロック信号CLKeのタイミングでFF39に保持されて画像データDToとして出力される。これにより、位相のずれがクロック周期よりも小さければ、2系統の画像データは同位相になるように位相調整ができる。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

グリッチ除去回路

【課題】誤動作の原因となるグリッチを除去すると共に転送スループットを悪化させることなく通信することが可能なグリッチ除去回路を実現する。

【解決手段】バスを使用して通信を行う信号のグリッチを除去するグリッチ除去回路において、信号が入力されクロック信号に同期して出力する第1のフリップフロップと、第1のフリップフロップの出力が入力されクロック信号に同期して出力する第2のフリップフロップと、第1のフリップフロップおよび第2のフリップフロップのそれぞれの出力がハイレベルまたはローレベルであることを検出してイネーブル信号を有効にする一致検出回路と、イネーブル信号が有効な時は第2のフリップフロップの出力をクロック信号に同期して出力し、イネーブル信号が無効な時は出力を保持する第3のフリップフロップとを備える。

(もっと読む)

高速時間ディジタル・コンバータ

【解決手段】 時間ディジタル・コンバータ(TDC)がサブ・インバータ遅延分解能でサンプリングすることを可能にするための手法が開示されている。一実施形態では、TDC中の差動型D−Qフリップフロップへの入力は、シングルエンド型信号、およびこの信号の遅延された形態および反転された形態に接続されてこの信号の時間補間を可能にする。さらに、TDC中の第1遅延ラインおよび相補な遅延ラインの負荷の平衡を保つための手法が開示されている。 (もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

信号伝送回路及びこれを用いた信号伝送システム

【課題】差動伝送方式の信号伝送回路の消費電力を低減する。

【解決手段】電源電位Vtermが供給される電源配線とグランド電位GNDが供給される電源配線との間に直列接続された差動出力回路10,20,30及び定電流源4を備える。このように、一つの定電流源4が3つの差動出力回路10,20,30に対して共用されており、差動出力回路10の動作に用いられた電流Iは差動出力回路20の動作に再利用され、さらに、差動出力回路20の動作に用いられた電流Iは差動出力回路30の動作に再利用される。これにより、Vterm×Iの消費電力で3つの差動出力回路10,20,30を動作させることが可能となるため、全体的な消費電力が1/3に低減される。

(もっと読む)

位相同期装置

【課題】本発明は、短いロッキングタイムを有しながらも、安定的に動作できる位相同期装置を提供する。

【解決手段】本発明の位相同期装置は、入力クロックを所定の分周比で分周した後、順次遅延させる動作により周波数を判別し、前記判別された周波数情報を用いて発振器ゲイン設定信号を生成する発振器ゲイン設定手段と、前記入力クロックに応じて、前記発振器ゲイン設定信号に対応する周波数を有する出力クロックを発振させるPLL回路を含むことを特徴とする。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波のタイミングジッタを有するジッタ重畳信号を容易に生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を並列に受け取り、それぞれ予め設定される遅延量で遅延させる複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、それぞれの遅延回路に、ジッタ重畳信号の各エッジに印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号が有するべき平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

電子回路、情報再生装置

【課題】 セットアップ違反に対するより一般的な検出技術を提供する。

【解決手段】 外部からの入力データを受ける第1のフリップフロップと、前記入力データを受けるラッチと、このラッチの出力と前記第1のフリップフロップの出力との排他的論理和を入力する第2のフリップフロップとを備えた電子回路。また前記第1のフリップフロップの出力を入力とし前記第2のフリップフロップの出力に基づく通知信号を抑制信号入力として用いる電子回路を具備した情報再生装置。

(もっと読む)

半導体集積回路装置及びクロックスキュー計測方法

【課題】クロックスキューをより正確に計測できる半導体集積回路装置及びクロックスキュー計測方法を提供する。

【解決手段】LSI100内部のクロック信号を入力するクロック入力端子1と、クロックスキューを計測するためのクロックスキュー計測信号を入力する計測信号入力端子2と、クロック信号とクロックスキュー計測信号とが入力される複数のF/F3と、計測信号入力端子2から複数のF/F3にクロックスキュー計測信号を分配する複数の計測信号分配ドライバ7と、を備え、複数のF/F3は、複数のF/F群5に分けられ、F/F群5内の全てのF/F3は、同一の計測信号分配ドライバ7と直接に信号線のみを介して接続され、複数のF/F3の出力信号に基づいて、複数のF/F3間におけるクロックスキューを計測するように構成した。

(もっと読む)

クロック伝搬回路

【課題】クロックスキューをより確実に抑制することが可能なクロック伝搬回路を提供する。

【解決手段】クロック伝搬回路10内のクロック伝搬ドライバ11及び12は、クロック停止制御信号SCSに応じてクロック信号CLKの伝搬を停止する。経時劣化検出回路20は、クロック伝搬ドライバ11及び12の内で動作状態にある一方のクロック伝搬ドライバ11から伝搬されたクロック信号CLKにより動作して自分自身の遅延劣化を検出する。動作状態切替部30は、経時劣化検出回路20による遅延劣化の検出に応じて、クロック伝搬ドライバ11に代えてクロック伝搬ドライバ12を動作状態とし、クロック信号CLKの論理回路ユニット2内の各回路への伝搬を継続する。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

161 - 180 / 321

[ Back to top ]