Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

201 - 220 / 321

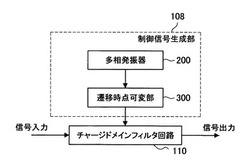

信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法

【課題】信号生成装置、フィルタ装置、信号生成方法およびフィルタ方法を提供すること。

【解決手段】信号レベルが第1のレベルと第2のレベルの間で遷移し、各々が同一の周波数および所定の位相の差分を有する複数の基礎信号であって、任意の基礎信号の信号レベルが第1のレベルである期間、および該任意の基礎信号に対して前記所定の位相遅れを有する次の基礎信号の信号レベルが第1のレベルである期間が重複する複数の基礎信号を生成する多相発振部と、前記各基礎信号の第1のレベルから第2のレベルへの遷移時点を、前記各基礎信号の前記次の基礎信号の第2のレベルから第1のレベルへの遷移時点以前に変化させてパルス信号を生成する遷移時点可変部300と、を備える信号生成装置。

(もっと読む)

ノイズ除去回路及びそれを備えたコンパレータ回路

【課題】 コンパレータの比較信号からノイズ成分に起因する信号変化を確実に除去すること。

【解決手段】 コンパレータ回路はコンパレータ20とタイマー回路30を備えている。タイマー回路30は、コンパレータ20の比較信号VCOMPがローレベルからハイレベルに反転してから少なくとも第1のタイミングと第2のタイミングの間に亘ってそのハイレベルが維持されたときに出力信号VOUTをローレベルとハイレベルの間で反転して出力する。タイマー回路30は、第1のタイミングで比較信号VCOMPがローレベルからハイレベルに反転したのを確認したときに、そのことを記憶する記憶状態に移行させる記憶手段38を有している。記憶手段38は、第1のタイミングと第2のタイミングの間で前記比較信号VCOMPが反転したときに、前記記憶状態を解除する。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックに応答して1ビットずつレベル遷移する複数のビットの周波数制御信号を生成する周波数制御信号生成部と、及び前記複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。また、他の発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び複数のビットの周波数制御信号に応答して、入力される基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

半導体集積回路装置及びデューティ制御方法

【課題】動作速度を向上出来る半導体集積回路装置及びデューティ制御方法を提供すること。

【解決手段】第1クロックCLK1に同期して動作し、該第1クロックCLK1が“H”レベルでアクティブとなる第1クリティカルパス12と、“L”レベルでアクティブとなる第2クリティカルパス13とを含むプロセッサコア2と、第2クロックCLK2のデューティを制御して前記第1クロックCLK1を生成する第1クロック生成部3と、前記第1クロックCLK1と、前記第1クリティカルパス12で生じる遅延時間Δtd1だけ遅れた第3クロックCLK3との第1位相差UPと、前記第1クロックCLK1と、前記第2クリティカルパス13で生じる遅延時間Δtd2だけ遅れた第4クロックCLK4との第2位相差DNとが最小となるように前記デューティを制御するよう、前記第1クロック生成部3に命令する制御部4とを具備する。

(もっと読む)

半導体装置及びその駆動方法

【課題】クロック信号の生成を制御することにより低消費電力の半導体装置及びその駆動方法を提供することを課題とする。

【解決手段】外部と信号の送受信を制御する送受信制御回路と、受信信号に含まれるエッジを検出し、且つリングオシレータの動作を制御するリングオシレータ制御回路と、リングオシレータの動作に基づいてクロック信号を生成するクロック生成回路と、クロック信号により動作を行うロジック回路とを設け、外部と信号の送受信を行う期間において、リングオシレータ制御回路が受信信号に含まれるエッジを検出した場合に、リングオシレータの動作を開始させてクロック生成回路からクロック信号を出力させ、送受信制御回路から外部への応答信号の送信が終了することにより、リングオシレータの動作を停止させてクロック生成回路からのクロック信号の出力を停止させる。

(もっと読む)

ジッタ発生装置

【課題】安価な集積回路を用いた場合であっても、所望のジッタが付加されたシリアルデータ信号を発生することができるジッタ発生装置を提供する。

【解決手段】ジッタ測定装置1は、ジッタを有するクロック信号CK11を発生するクロック発生部11と、クロック信号CK11が有するジッタの振幅及び位相の少なくとも一方を制御可能なジッタ制御部12a,12bと、ジッタ制御部12aからのクロック信号を用いて内部クロック信号CK14を生成するPLL回路15aを有し、内部クロック信号CK14に同期して所定のデータパターンS1を出力する集積回路15と、集積回路15から出力されるデータパターンS1を入力とし、ジッタ制御部12bからのクロック信号に同期してデータパターンS1に応じたデータをシリアルデータ信号D1として出力するDフリップフロップ回路16とを備える。

(もっと読む)

適応型ホールドを用いる、デジタル・シングル・イベント過渡に対して強化されたレジスタ

【課題】デジタル・シングル・イベント過渡に対してレジスタを強化する。

【解決手段】レジスタの捕捉クロック・エッジのタイミングを調整して、データが正しい状態に戻ったときにレジスタがデータを捕捉するようにすることにより、レジスタをDSETの混乱状態から保護することができる。データ・グリッチがクロック・エッジ付近で発生した場合、レジスタ出力における有効時間が増加される(CLKからQ)。この有効時間の増加は、DSET過渡の存在がクロック・エッジ付近で検出されたときに、行われる。

(もっと読む)

位相差計測回路

【課題】2つの信号の進み遅れに関係なく、遷移タイミングの差を測定することができる位相差計測回路を提供する。

【解決手段】EXOR11により、デジタル信号S1,S2の位相差に対応したパルス幅の信号S3が出力される。信号S3は、インバータ12で反転された信号S4と共にセレクタ13に与えられ、選択信号SELに従っていずれか一方が選択され、ゲート制御用の信号S5としてADN14に与えられる。AND14には連続したクロック信号CLKが与えられており、信号S5でゲート制御されたクロック信号CLKが、信号S6としてカウンタ15に与えられる。カウンタ15は、信号S6のパルス数をカウントし、カウント値CNTを出力する。選択信号で信号S3,S4を選択することにより、デジタル信号S1,S2の進み遅れに関係なく、遷移タイミングの差を測定できる。

(もっと読む)

測定量を測定するためのホイール電子回路およびタイヤ監視システム

【課題】本発明は、タイヤ監視システムにおいて、測定すべき測定量の測定に及ぼされる妨害パルスおよび/または信号ノッチの影響を少なくとも低減するという課題を基礎とする。

【解決手段】車両のタイヤ監視システム内または車両のタイヤ監視システム用に設けられ、変調された搬送波信号から包絡線を検出することによって、搬送波周波数を有する受信された振幅変調問い合わせ信号を復号化するための評価装置と、該問い合わせ信号を入力結合するためのカウンタ入力側を有するデジタルカウンタと、入力側で該デジタルカウンタのカウンタ出力側に接続されているシフトレジスタと、該シフトレジスタの出力側に接続された論理回路とを有する、ホイール電子回路。

(もっと読む)

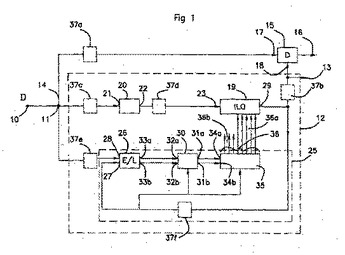

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

半導体集積回路およびイコライザの制御方法

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

同期損失防止方法及び同期損失防止装置

【課題】CDR回路側の原因による接続ノード間の同期化の非成立を抑制し、接続失敗を抑制することができる同期損失防止方法及び同期損失防止装置を提供する。

【解決手段】受信データから同期化クロックを生成するCDR(Clock Data Recovery )回路と、受信データの受信開始から同期化検出時間Nを経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、接続失敗処理を行う接続失敗処理段階(S15)と、受信データの受信開始から同期化リトライ判定時間(N/2)を経過しても同期化クロックに基づく接続ノード間の同期化が非成立のときに、CDR回路の動作を補正処理する補正処理段階(S13)とを備える。

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

デューティ検出回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】入力データDinと、該入力データDinと周波数および位相が同期したクロックCKとを入力とし、前記入力データDinのデューティの100%からの差分δを表す信号Errを、前記入力データDinに遷移が生じた時だけ出力する。前記信号Errは、前記入力データDinのデューティの100%からの差分δに対応する時間を単位時間Tに対して増減した時間幅のパルス信号である。

(もっと読む)

クロックスキューコントローラ及びそれを備える集積回路

【課題】クロックスキューを補償することができるコントローラを備える集積回路を提供する。

【解決手段】第1クロックマッシュに入力される第1クロックと第2クロックマッシュに入力される第2クロックとの間のスキューを調節するためのクロックスキューコントローラを備える。クロックスキューコントローラは、第1出力クロックと第2出力クロックとの間の遅延時間に対応するパルス信号を発生するパルス発生器と、パルス信号のパルス幅に対応するデジタル信号を出力するパルス幅検出器と、デジタル信号に対応する時間だけ、第1及び第2クロックのうちのいずれか一つを遅延させるクロック遅延調節器と、を備えて、クロックマッシュの間のクロックスキューを検出し、該検出されたスキューに対応する遅延時間だけクロックマッシュに供給されるクロック等の遅延時間を調節することができる。

(もっと読む)

半導体集積回路

【課題】クロック信号が高周波数であってもクロック信号を高精度に検査することができる半導体集積回路を提供することを課題とする。

【解決手段】第1のクロック信号を分周し、かつ2相以上に多相化した第2のクロック信号を出力する複数のラッチ回路(11〜18)を有することを特徴とする半導体集積回路が提供される。例えば、前記複数のラッチ回路は、ループ状に接続され、クロック端子には前記第1のクロック信号又は前記第1のクロック信号の論理反転信号が入力される複数のフリップフロップである。

(もっと読む)

フィルタ回路

【課題】連続する複数のサンプリングタイミングで混入する幅狭のノイズを除去する。

【解決手段】フィルタ回路1は入力信号処理回路2と信号レベル判定回路3とを備える。入力信号処理回路2は、クロック信号CLKでデジタル入力信号Dinをサンプリングして保持し、隣り合うサンプリングタイミングの間においてデジタル入力信号Dinにレベル変化が生じた場合、その保持した信号を反転する。信号レベル判定回路3は、サンプリング入力信号Dsをクロック信号CLKで複数段に順次遅延させ、遅延させた各段の信号が全て一致したときに、その一致したレベルを持つ信号Doutを出力する。

(もっと読む)

クロック同期システム及び半導体集積回路

【課題】クロック同期システムにおいて、LSIチップの大規模化・高集積化・高密度化に因る物理現象の複雑化に伴いギガ・ヘルツ級の高い周波数を持つ被分周クロックあるいは分周クロックをLSIチップ全面に渡り長距離配線を分配し且つシグナルインテグリティを確保することが困難である。

【解決手段】基準クロックに基づき逓倍クロックを生成する位相同期回路と、逓倍クロックに基づき分周クロックを生成する分周回路と、基準クロックを分周してフレームパルスを生成するフレームパルス生成回路とを備え、前記分周クロックは前記フレームパルスにより位相同期化がなされることを特徴とする。

(もっと読む)

201 - 220 / 321

[ Back to top ]