Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

81 - 100 / 321

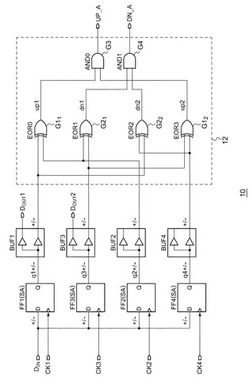

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

半導体集積回路装置

【課題】ノーマルなクロックとSSCとを生成するクロック発生回路における回路面積を低減しながら、高精度のSSCを生成する。

【解決手段】電圧制御発振器から出力されたクロック信号vco1は、分周器13によって分周され、分周クロックph0としてセレクタ15に出力される。分周器13は、制御回路12の制御信号Pconに基づいて、周期の1/mずつ位相のシフトした分周クロックph1〜phmを出力する。セレクタ15は、分周クロックph0〜phmのうち、最も近い位相シフトをもつ2つの分周クロックphj,phj+1を選択する。位相補間回路16は、制御回路12から出力される重み付けデータ信号Aに基づいて、分周クロックphj,phj+1間の位相差の間を更に細分化した位相シフト量で位相シフトさせ、出力クロックfout1として出力する。

(もっと読む)

雑音除去回路及び雑音除去回路を備えた半導体装置

【課題】高い周波数のクロックを用いずに雑音を除去できる雑音除去回路及び雑音除去回路を備えた半導体装置を提供する。

【解決手段】データ入力信号がロウレベル又はハイレベルになると活性化しハイレベル又はロウレベルを維持するとクロック信号に同期して非活性化する第一及び第二のリセット信号を生成する第一及び第二のリセット信号生成回路と、クロック信号の反転信号を計数し第一又は第二のリセット信号によりリセットされる第一及び第二のカウンタ回路と、セレクタ回路とセレクタ回路の選択した信号をクロックに同期して出力する出力フリップフロップ回路とを備え、セレクタ回路がハイレベル又はロウレベルに固定された信号、出力フリップフロップの出力信号のいずれかを第一及び第二のカウンタ回路の出力信号の論理レベルにより選択して出力するデータ出力回路と、を備える。

(もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

ノイズ除去装置

【課題】使用環境状況の影響を受けずに、ノイズを確実に除去する。

【解決手段】n個のD型フリップフロップを直列に接続し、各D型フリップフロップの出力した信号の論理積を出力とするデジタル・フィルタ20と、m×2個のプリミティブ素子を有するインバータを直列に接続したディレイ・フィルタ30を並列に接続する。入力信号INPUTを両フィルタに入力し、AND回路40が各フィルタの出力する信号DELAYと信号ANDの論理積である信号FILTを出力する。発生期間がクロック信号の周期とDFF回路の段数に対応する期間より短いノイズをデジタル・フィルタ20が除去し、インバータ回路の遅延時間より周期の短いノイズをディレイ・フィルタ30が除去する。

(もっと読む)

パラレル−シリアル変換器及びパラレルデータ出力器

【課題】パラレル−シリアル変換器において、データ信号をラッチするフリップフリップ(FF)に供給されるクロック信号の位相ずれを調整する。

【解決手段】FF1−1〜1−5によるデータ信号D0,D1を選択回路2で選択出力したデータ信号D[0+1]をFF4によりラッチ出力するパラレル−シリアル変換器において、レプリカのデータ信号repIN0,repIN1を選択回路10で選択出力したデータ信号repDをラッチしたFF11によるデータ信号repOUTに基づき位相ずれ検出回路12,13が生成する位相調整指示値信号に従い、分周回路3による分周クロック信号の位相を調整してクロック信号divCLKを発生する任意位相生成回路15を備えると共に、クロック信号ffCLKとrepCLKとを位相比較し、クロック信号repCLKを移相させる位相設定回路16,17を備える。

(もっと読む)

コンパレータ回路およびモータ駆動回路

【課題】 コンパレータ回路から、高耐圧特性を必要とするコンデンサを削減する。

【解決手段】 一端が共通に接続されたコンデンサC1〜C3と、C1に電圧VrefまたはVinの何れか一方を順次印加する第1スイッチ回路と、入力端がC1〜C3の接続点に接続されたインバータと、C1にVrefが印加される第1期間に、インバータの入力端と出力端とを接続する第2スイッチ回路と、第1期間の次に、C1にVinが印加される第2期間には、インバータの出力レベルを出力し、第1期間には、第2期間の最後におけるインバータの出力レベルを保持して出力する第1ラッチ回路と、第1期間には、C3にLレベルの電圧を印加するとともに、C2にHレベルの電圧を印加し、第2期間には、C3にHレベルの電圧を印加するとともに、C2にLまたはHレベルの電圧を印加する制御回路と、を有する。

(もっと読む)

精密三角波形生成器

【課題】三角波形の品質をさらに正確に制御するためのシステムおよび方法を提供すること。

【解決手段】三角波形生成器は、容量素子、調整器、および制御回路を含むものとして規定される。調整器は、第1の制御信号に応答して容量素子を充電し、第2の制御信号に応答して容量素子を放電するように構成される。制御回路は、基準波形に応答し、第1および第2の制御信号を生成する。一例において、制御回路は、基準波形の振幅、周波数、位相、および対称性に応答して、第1および第2の制御信号を生成する。

(もっと読む)

スペクトラム拡散クロック生成装置

【課題】生成されたスペクトラム拡散クロックを、各種タイミングを制御するカウンタのクロックとしても用いることのできるスペクトラム拡散クロック生成装置の提供。

【解決手段】SSC源クロック発生回路3,基準クロック発生回路5が発生するSSC源クロック,基準クロックは、16bitカウンタ7,9に入力されて、そのクロック数がカウンタ値cnt1,cnt2として計数される。カウンタ値cnt1,cnt2は、比較回路10に入力され、カウンタ値cnt1がカウンタ値cnt2よりも1以上大きくなると、比較回路10は比較結果cmpとしてLレベルの信号を出力する。すると、パルス生成回路21がLレベルの矩形パルス(間引き要求pls_cg)を出力し、AND回路31によりその間引き要求pls_cgとSSC源クロックとの論理積が計算されることによって、SSC源クロックが1クロック分間引かれる。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

スイッチングドライバ回路

【課題】ディスクリート部品を用いることなく、パルス時間が長く、しかも、電圧変動が大きいノイズを確実に除去可能とする。

【解決手段】

入力信号の立ち上がり、立ち下がりを検出し、エッジ検出信号を出力するエッジ検出回路101と、入力信号を所定シフト時間t1シフトして出力するシフトレジスタ回路106と、エッジ検出回路101のエッジ検出信号の入力時点から所定入力時間t2経過後にカウントアップ信号を出力するカウンタ回路102と、シフトレジスタ回路106の出力信号を、カウンタ回路102のカウントアップ信号に同期して出力するDFF回路103と、DFF回路103の出力信号を外部へ出力する出力回路104と、シフトレジスタ回路106とカウンタ回路101のクロック信号を生成、出力する発振回路105とを具備してなり、所定入力時間t2に満たない入力信号が出力されないようになっている。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

デジタルノイズ保護用回路及び方法

【課題】コンパレータによって生成されたデジタル信号をノイズからの保護方法を提供する。

【解決手段】コンパレータ1によって生成されたデジタル信号(Vcomp)のロジック状態の第1スイッチングにおいて第1ロジック状態から第2ロジック状態へと切り替える出力信号(Vout)の生成ステップと、前記出力信号(Vout)の第1ロジック状態から第2ロジック状態への変更の検出ステップと、第1ロジック状態から第2ロジック状態への変更後の第1時間間隔に対する前記出力信号(Vout)のさらなる切り替えの禁止ステップとにより前記デジタル信号(Vcomp)をノイズから保護する。

(もっと読む)

半導体装置、半導体装置のノイズ除去方法

【課題】より確実にノイズ除去のできるノイズ除去回路を搭載する半導体装置、ノイズ除去方法を提供する。

【解決手段】半導体装置は、ノイズ検知回路(21)と、入力信号遅延回路(22)と、マスク回路(23)とを具備する。ノイズ検知回路(21)は、入力信号(RESETB)に重畳するノイズを検知して、所定時間のマスク信号(NE_FLG)を出力する。入力信号遅延回路(22)は、入力信号(RESETB)を遅延させて遅延信号(RES_DLY)を出力する。マスク回路(23)は、マスク信号(NE_FLG)に基づいて、前記遅延信号(RES_DLY)をマスクした出力信号(RESB)を出力する。

(もっと読む)

可変遅延回路、及びスペクトル拡散回路

【課題】従来技術と比較して、簡易な構成でスペクトラム拡散機能を有する可変遅延回路及びスペクトル拡散回路を提供する。

【解決手段】第1の直列回路の遅延セル14の各々及び第2の直列回路の遅延セル14の各々に対応して設けられると共に、対応する遅延セル14から出力されたクロック信号が入力され、かつ切換信号が入力され、入力されたクロック信号に同期させて入力された切換信号を保持し、保持した切換信号を選択信号として対応する遅延セルに出力し、かつ保持した切換信号を出力するフリップフロップ28が直列接続された第3の直列回路と、入力されたクロック信号に同期させて入力された切換信号を保持し、保持した切換信号を出力するフリップフロップ28と、第3の直列回路の最後段に設けられたフリップフロップ28から出力された切換信号を反転して、第1の直列回路の最前段に設けられた遅延セル14に入力するインバータ30とを含む。

(もっと読む)

ディジタルノイズフィルタ回路

【課題】入力信号のノイズをディジタル的に除去して出力するディジタルノイズフィルタ回路において、消費電力を低減する。

【解決手段】入力信号と出力信号との論理レベルを比較し、両者が不一致の場合にゲーティングクロックを供給し、一致の場合にゲーティングクロックの供給を停止するゲーティングクロック生成回路と、ゲーティングクロックが動作クロックとして供給され、入力信号のノイズを除去して出力信号として出力するノイズフィルタ回路と、を備える。入力信号と出力信号の論理レベルが一致しているときにゲーティングクロックを停止するので消費電力が低減できる。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

同期信号発生回路

【課題】 PWM信号からその同期信号を発生する。

【解決手段】 三角波発生回路101は、PWM信号PWMINの立ち上がりエッジおよび立ち下がりエッジの各々を検出する度に、先行して開始した三角波信号の発生と並行して三角波信号を発生する手段であり、立ち上がりエッジまたは立ち下がりエッジの検出後、三角波信号を基準レベルから一定の時間勾配で変化させ、その後、同種のエッジが検出された以降、同じ大きさの逆方向の時間勾配で三角波信号を変化させる。同期信号発生部160は、三角波発生回路101が発生する三角波信号TRIA、TRIB、TRICに基づいてPWM信号PWMINに同期した同期信号SYNCを発生する手段であり、相前後して発生を開始した2個の三角波信号の大小関係が逆転したとき、同期信号SYNCのレベルを反転させ、先行して発生を開始した三角波信号を基準レベルに初期化する。

(もっと読む)

81 - 100 / 321

[ Back to top ]