Fターム[5J039KK11]の内容

Fターム[5J039KK11]に分類される特許

1 - 20 / 141

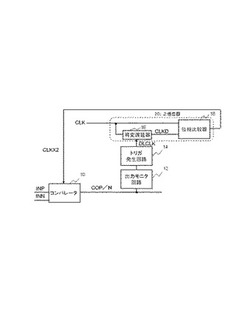

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

クロック診断回路

【課題】単一のクロックから、クロック周期、及びクロックパルス幅の変動の異常を確実に検出することができるクロック診断回路を提供することを目的とする。

【解決手段】クロックs10を予め設定されるクロックパルス幅以下の所定時間、遅延させる遅延回路2と、遅延回路2から出力された遅延クロックを所定の周期数倍遅延させる整数倍遅延回路3と、クロックを、遅延クロックを用いて符号化する第1の排他的論理和回路4と、第1の排他的論理和回路4の出力を、整数倍遅延回路3の出力を用いて復号化する第2の排他的論理和回路5と、クロックs10と第2の排他的論理和回路5の出力とを比較して、クロックの異常を検出する比較回路6と、を備え、クロックパルス幅、及びクロック周期の変動を、自身の単一のクロックに基づいて検出するようにしたことを特徴とするクロック診断回路1。

(もっと読む)

時間差増幅回路

【課題】時間差増幅回路の時間差オフセットを低減する。

【解決手段】複数の時間差増幅器が多段接続された時間差増幅回路100であって、複数の時間差増幅器は、第1の正入力端子1a、第1の負入力端子1b、第1の正出力端子1c及び第1の負出力端子1dを有する第1の時間差増幅器TDA1と、第2の正入力端子2a、第2の負入力端子2b、第2の正出力端子2c及び第2の負出力端子2dを有し、第1の時間差増幅器の出力信号が入力される第2の時間差増幅器TDA2と、第2の正入力端子2aに第1又は第4の配線I1,I2を接続させる第1の選択素子S1と、第2の負入力端子2bに第2又は第3の配線I2、I3を接続させる第2の選択素子S2を有する選択回路10aと、選択回路10aを制御する制御回路50を具備する。

(もっと読む)

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

遷移検出回路

【課題】

簡潔な構成でコード信号の遷移を検出する遷移検出回路を提供する。

【解決手段】

1ビットずつ遷移するグレイコードの遷移を検出する検出回路において、グレイコードのビットに含まれる1の個数が偶数であるか奇数であるかによって変化する信号を出力する組み合わせ論理回路と、組み合わせ論理回路の出力が変化したときに有効となる遷移検出信号を生成する比較回路とを備える。

(もっと読む)

差動入力インターフェース回路、表示ドライバIC、表示パネルモジュールおよび画像表示装置

【課題】高速に伝送されてくるデータを安定して受信する差動入力インターフェース回路を提供する。

【解決手段】一対の差動信号を受信して正相データ信号PA11を出力する第1の差動アンプ103と、一対の差動信号を受信して負相データ信号NA11を出力する第2の差動アンプ104と、一対の差動クロック信号を受信して正相クロック信号FX11を出力する第3の差動アンプ105と、正相データ信号PA11と負相データ信号NA11とを正相クロック信号FX11に同期してラッチすることにより、ラッチ出力信号PDを出力するデータラッチ回路303と、ラッチ出力信号PDよりシングルエンドのデータ信号L13を生成するデータ生成回路302とを備える。

(もっと読む)

比較器及びAD変換器

【課題】高速に、かつ高精度で動作する比較器及びADC等を構築すること。

【解決手段】従来の比較器は、比較器に入力される2つの入力電圧の差が小さいほど、安定した比較結果を得るまでに時間がかかり、また、2値の出力しか得られない。安定した比較結果が得られるまでの状態を、通常メタステーブル状態と呼んでいる。本発明は、このメタステーブル状態を積極的に利用する。すなわち、メタステーブル状態を検出することで、ハイとロウの中間レベルの判定を合わせて行える。これによって、3値以上を出力する比較器が容易に実現できる。本発明の比較器は、比較器の数を減少させることができると同時に、通常では判定が終了していない状態で比較動作を終了させることが可能になるため、速度向上にも役立ち、高速、高精度のADC(アナログデジタル変換器)等の機器に応用できる。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

(もっと読む)

制御回路及びこれを用いたデータ保持装置

【課題】セットの部品点数削減や低消費電力化を実現することが可能な制御回路及びこれを用いたデータ保持装置を提供する。

【解決手段】制御回路10は、トリガ信号TRIGGERに特定の信号パターンが現れたときに制御部11の動作に必要な内部クロック信号LCLKの生成を開始し、少なくとも制御部11において所定の処理が完了するまで内部クロック信号LCLKの生成を継続した後、内部クロック信号LCLKの生成を停止する内部クロック生成部12と、内部クロック信号LCLKを用いて前記所定の処理を実行する制御部11と、を有する。

(もっと読む)

1 - 20 / 141

[ Back to top ]