Fターム[5J042DA00]の内容

論理回路 (4,317) | 目的、効果 (948)

Fターム[5J042DA00]の下位に属するFターム

Fターム[5J042DA00]に分類される特許

1 - 20 / 86

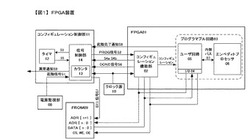

FPGAのコンフィギュレーション制御回路、FPGA装置及び方法、並びに、コンフィギュレーションデータ更新方法

【課題】メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGAのコンフィギュレーションを高い信頼性をもって確実に行えるコンフィギュレーション制御回路、FPGA装置及び方法を提供する。

【解決手段】FROM12には、同じ内容のコンフィギュレーションデータが複数個格納されている。信号制御部08が、FPGA01にコンフィギュレーションのトリガを与えると、FPGA01は、FPGA01がデータの読み出し先として指定するFROM12の指定領域に格納されているデータを読み出して、コンフィギュレーションを行う。コンフィギュレーションが失敗した場合には、信号制御部08は、FROM12の指定領域を切り替え、FPGA01がFROM12の切り替え後の指定領域から別のデータを読み出してコンフィギュレーションするためのトリガをFPGA01に与える。

(もっと読む)

プログラマブルデバイス、プログラマブルデバイスのリコンフィグ方法および電子デバイス

【課題】

プログラマブルデバイスでソフトエラーが発生した際に、コンフィグメモリを書き直す場合、その間動作を停止しなければならないが、通信装置等、装置停止が及ぼす影響が大きなシステムでは、システムの動作を停止せずに復旧することが必要である。

【解決手段】

複数の制御回路と、前記複数の制御回路からの出力を比較してエラーの発生を検査する比較部と、前記比較部にてエラーが発生していると判断された場合に、前記複数の制御回路のうちエラーが発生していない制御回路の内部状態を記憶する記憶部と、前記比較部にてエラーが発生していると判断された制御回路をリコンフィグするリコンフィグ部と、前記記憶部に記憶されたエラーが発生していない制御回路の内部状態を、前記比較部にてエラーが発生していると判断された制御回路に入力する制御部と、を備えるプログラマブルデバイスである。

(もっと読む)

電子回路網の信頼性を向上させるための装置および関連する方法

【課題】電子回路網の信頼性を向上させるための装置および関連する方法を提供すること。

【解決手段】上記装置は、装置の第1の構成に使用される第1のセットの回路要素と、装置の第2の構成に使用される第2のセットの回路要素とを含み、装置の第1の構成は、装置の信頼性を向上させるために、装置の第2の構成に切り替えられる。上記方法は、第1の構成に割り当てられた第1のセットの回路要素を使用することによって、第1の構成で集積回路(IC)を動作させることと、第2の構成に割り当てられた第2のセットの回路要素を使用することによって、第2の構成でICを動作させることとを含み、第1の構成でICを動作させた後に第2の構成でICを動作させるのは、ICの信頼性を向上させる。

(もっと読む)

制御装置、処理装置、処理システム、制御プログラム

【課題】処理の途中に、再構成が行われたとしても、処理ブロックは、当該処理の処理を続行することが出来る。

【解決手段】データに対してそれぞれが所定の処理を行ない、再構成可能な複数の処理手段と、前記複数の処理手段間をデータ転送可能に接続し、再構成可能な接続手段と、を含む処理装置の当該処理手段または当該接続手段のうち何れか一方を、当該処理手段の状態に基づいて、再構成する構成手段を有することを特徴とする制御装置。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後の論理ブロックの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】プログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

スピン・トランスファ・トルク磁気抵抗デバイスを用いるソフトウェア・プログラマブル・論理

【課題】スピン・トランスファ・トルク磁気抵抗ランダムアクセスメモリ技術を用いるソフトウェア・プログラマブル・論理のためのシステム,回路および方法を提供する。

【解決手段】磁気トンネル接合(MTJ)素子と、MTJ素子に結合されるプログラマブル・ソースと、書込み及び読出し部を備え、前期読出し部は、書込み動作の間中、高インピーダンス状態に設定されるように構成されるMUXドライバを具備し、前記MTJ素子の第一グループを入力プレーンに配列し、第二グループを出力プレーンに配列し、入力プレーンおよび出力プレーンを、各々のMTJデバイスの自由層の相対的な極性に基づいた論理関数を形成するために組み合わせられるプログラマブル・論理アレイを提供する。

(もっと読む)

プログラマブルデバイスを過電圧攻撃から守るためのシステムおよび方法

【課題】レジスタ、過電圧検出回路およびロジック回路を有しているプログラマブル集積回路デバイスを提供すること。

【解決手段】少なくとも1ビットの値を格納するように構成されているレジスタであって、該レジスタは、印加された電圧源に結合されている、レジスタと、過電圧検出回路であって、該過電圧検出回路は、該印加された電圧源によって発生された電圧を検出することと、検出された電圧がトリガー電圧よりも高いか、または等しい場合に、過電圧信号を生成することとを行うように構成されている、過電圧検出回路と、ロジック回路であって、該ロジック回路は、該生成された過電圧信号に応答して、該レジスタをクリアにするように構成されている、ロジック回路とを含む、プログラマブル集積回路デバイス。

(もっと読む)

FPGA、FPGAを用いた回路再構成システム、方法およびプログラム

【課題】回路の一部に不具合が生じて新たな回路を同一基板内に再構成する場合に、この新たな回路との関係で伝送される信号のタイミングに不具合が生じないようにすることが可能なFPGA、FPGAを用いた回路再構成システム、方法およびプログラムを得ること。

【解決手段】回路ブロック監視手段12が回路ブロックを構成する論理部に不具合があることを検出すると、これに代わる新しい回路ブロックを構成するとき最適化処理実行手段13は論理部同士を接続する接続部による信号の伝達タイミングを前の回路ブロックの接続部と可能な限り同一になるように最適化する。回路ブロック交代手段14は新しい回路ブロックの運用を開始させる。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、前記充電用トランジスタのソース−ドレイン間の電圧が電源の電圧Vddと同値の電圧であるときに、これらソース−ドレイン間を流れる電流が1×10−9A以下となる範囲の電圧をこの充電用トランジスタのゲートに印加する定電圧印加手段を接続する。

(もっと読む)

再構成可能な論理装置

【課題】再構成可能な論理装置を提供する。

【解決手段】第1論理ブロックと、第2論理ブロックとを含む少なくとも2つの論理ブロック;第1論理ブロックに連結される複数の第1グローバル配線と、前記第2論理ブロックに連結される複数の第2グローバル配線と、を含むグローバル配線グループ;複数の第1グローバル配線と、複数の第2グローバル配線とが交差する領域にそれぞれ配される複数の第1不揮発性メモリ素子を含み、論理装置の動作をリアルタイムで再構成するために、複数の第1不揮発性メモリ素子それぞれに保存された第1データを基に、複数の第1グローバル配線及び第2グローバル配線のルーティングを制御するグローバル制御部;を含む再構成可能な論理装置である。

(もっと読む)

多値ハザード除去回路

【課題】ディジタル信号から多値ハザードを除去する。

【解決手段】トランジスタ1、2、17と抵抗20、21が構成する多値判別手段、この判別手段の出力信号に基づいて動作するトランジスタ22〜25とダイオード36が構成するオン・オフ駆動手段、及びこのオン・オフ駆動手段がオン・オフ駆動するトランジスタ3、5が構成する双方向性プル・スイッチング手段、が『フージ(Hooji)代数』を具体化した1多値論理回路を構成する。この多値論理回路、プル・ダウン用抵抗26及びD型フリップ・フロップ27の入力部に有る2値判別手段の組合せが、多値信号を2値信号に変えると同時に多値ハザードを2値ハザードに変える。同期信号により制御されたD型フリップ・フロップ27がその2値ハザードを除去した2値信号を出力する。

(もっと読む)

半導体装置

【課題】外部クロック信号CL、チップセレクト信号CE等の制御信号のノイズを適切に除去する。

【解決手段】半導体装置内部において生成される内部クロック信号ICLの立ち上がり及び立ち下がりのタイミングに同期して入力信号INの値を複数の異なるタイミングで保持する第1保持回路20及び第2保持回路22を備え、保持された値に応じて入力信号INのノイズを除去するノイズ除去回路を設ける。

(もっと読む)

情報処理装置及び書換方法

【課題】FPGAの回路情報を含むメモリの書き換えを行う際に、電源遮断等の異常が発生しても安全に元の状態に復旧できる情報処理装置及び書換方法を提供する。

【解決手段】回路の書き換えが可能な集積回路と、集積回路の回路情報を記憶する第1の記憶領域と第2の記憶領域とを備える記憶手段と、電源が投入されたときに、第1の記憶領域に記憶された回路情報に基づき、集積回路の回路を構成する回路構成手段と、電源が投入されたときに、第2の記憶領域に正常な回路情報が記憶されているのかを確認する確認手段と、を有し、回路構成手段は、確認手段により、第2の記憶領域に正常な回路情報が記憶されていると確認されたときは、第2の記憶領域に記憶された回路情報に基づき、集積回路の回路を書き換える。

(もっと読む)

信号保持回路およびこれを使用したシステム保護装置

【課題】電源電圧が低下したときに信号保持回路での信号保持を確実に解除する。

【解決手段】出力端子toを複数の入力端子のうちの1つtbに接続し、残りの外部入力端子taに外部信号が入力される論理和回路14と、該論理和回路14の出力端子に接続された単一パルスを生成するパルス生成回路15とを備え、前記論理和回路14の前記外部入力端子tbにハイレベルのパルス信号が入力されたときに、当該論理和回路14の出力をハイレベルに保持する信号保持回路13であって、前記論理和回路14の前記出力端子toと前記入力端子tbとの間に、電源電圧低下時に当該論理和回路14によるハイレベル保持状態を解除する電圧を高めるダイオードDを介挿した。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

論理回路および該論理回路を有する表示装置

【課題】デプレション型の単極性のトランジスタでも動作可能な論理回路を提供することを課題とする。

【解決手段】ソースフォロワ回路と、該ソースフォロワ回路の出力部が入力部に接続され、具備するトランジスタのすべてが単極性の論理回路と、を有し、ソースフォロワ回路に接続されている低電位側の配線の電位は、該トランジスタのすべてが単極性の論理回路に接続されている低電位側の配線よりも低くして論理回路を構成する。このようにすることで、デプレション型の単極性のトランジスタでも動作可能な論理回路を提供することができる。

(もっと読む)

多数決回路付きフリップフロップ回路

【課題】ソフトエラーに対する耐性向上と回路規模の縮小を両立させることができない。

【解決手段】クロック調整回路7は、入力クロック信号CLKのハイ状態とロウ状態の比

率を、1つのマスタラッチ1のデータ保持時間帯を狭めるように調整し、ハイ状態(マスタラッチ1のデータ保持時間)を可及的に狭めて出力する。インバータ6はクロック調整回路7の出力を極性反転する。マスタラッチ1のトランスファーゲート4およびスレーブラッチ2−1〜2−3のトランスファーゲート5−1〜5−3は、クロック調整回路7およびインバータ6の出力により、データの通過を制御する。スレーブラッチ2−1〜2−3の出力は3入力多数決回路3で多数決をとられた後に出力信号Qとなる。

(もっと読む)

リコンフィギュラブル回路及びリコンフィギュラブル回路システム

【課題】内部動作が停止した場合に外部バッファと適切にデータのやり取りが可能なリコンフィギュラブル回路を提供する。

【解決手段】リコンフィギュラブル回路は、複数の演算器と該演算器間を再構成可能に接続するネットワーク回路とを含むリコンフィギュラブル演算器アレイと、リコンフィギュラブル演算器アレイの動作の実行及び停止を制御する停止制御回路と、リコンフィギュラブル演算器アレイの動作の停止時に外部から供給されるデータを一時的に格納し、リコンフィギュラブル演算器アレイの動作の再開時に格納されたデータをリコンフィギュラブル演算器アレイに供給するバッファ回路とを含むことを特徴とする。

(もっと読む)

1 - 20 / 86

[ Back to top ]