Fターム[5J043AA01]の内容

Fターム[5J043AA01]に分類される特許

1 - 20 / 60

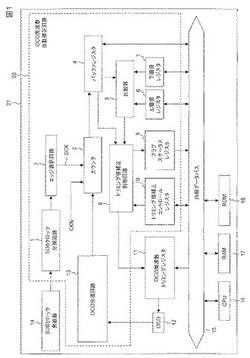

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

シュミットインバータ回路及び半導体装置

【課題】チャタリング抑制の特性を維持したまま、電源電圧や温度の影響による出力周波数の変化を抑制する。

【解決手段】スイッチSWH及びSWLがオフ状態で、入力信号がVthLより大きくVDD/2未満の場合、第1インバータ12の閾値電圧はVDD/2となり、出力信号OUTはハイレベルとなる。入力信号がVDD/2〜VthHとなると、出力信号OUTが立ち下がり、制御信号CSLが立ち上がって、スイッチSWLがオンされ、閾値電圧は低電位側に変化する。入力信号がVthHを超えると、信号SLHが立ち下り、入力信号が再びVthH未満となると、信号SLHが立ち上がり、制御信号CSLが立ち下がって、スイッチSWLがオフされ、閾値電圧は再びVDD/2に変化する。入力信号がVDD/2〜VthLとなると、出力信号OUTが立ち上がり、制御信号CSHが立ち上がって、スイッチSWHがオンされ、閾値電圧は高電位側に変化する。

(もっと読む)

発振回路

【課題】高精度発振が必要な場合には発振周波数の温度依存性を低減して高精度発振を可能とすると共に、高精度発振が不要な場合には発振回路の消費電流を低減することができる発振回路を提供する。

【解決手段】発振回路は、温度依存性が調整された出力電圧を出力するバンドギャップ回路と、第1の可変抵抗を備え、バンドギャップ回路から出力された出力電圧を第1の可変抵抗の抵抗値に応じた出力電流に変換し、変換された出力電流に基づいてバイアス電流を出力する電圧−電流変換回路と、第2の可変抵抗、容量及び比較部を備え、第2の可変抵抗の抵抗値と容量の容量値とに基づく発振周波数で発振すると共に、比較部が電圧−電流変換回路から入力されたバイアス電流の電流値に応じて動作するCR発振回路と、を備える。

(もっと読む)

デュアルパスマルチモード順次記憶素子

【課題】デュアルパスマルチモード順次記憶素子

【解決手段】本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。

(もっと読む)

VCO回路

【課題】 位相雑音の発生や発振周波数のずれを抑制することのできるVCO回路を提供する。

【解決手段】 実施形態のVCO回路は、3個のインバータIV1〜IV3をリング状に接続したリングオシレータ1を備え、制御電流生成部2が、入力された制御電圧Vctを電圧−電流変換した制御電流Ictを生成し、リングオシレータ1へ電源電流として供給する。また、このVCO回路では、定電流生成部3が、定電流Iaを生成し、制御電流Ictに重畳する電源電流としてリングオシレータ1へ供給する。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

発振回路

【課題】安定したクロック信号を生成可能な発振回路を提供する。

【解決手段】発振回路は、第1の比較回路と、第2の比較回路と、第1の電圧制御回路と、第2の電圧制御回路と、クロック生成回路を備える。第1の比較回路は、第1の電圧と第1の閾値電圧とを比較して、第1の比較結果を生成する。第2の比較回路は、第2の電圧と第2の閾値電圧とを比較して、第2の比較結果を生成する。第1の電圧制御回路は、前記第1の比較結果が変化するタイミングに同期して前記第1の電圧を第1の電圧値だけ減少させ、その後、前記第2の比較結果が変化するタイミングに同期して前記第1の電圧を上昇させる。第2の電圧制御回路は、前記第2の比較結果が変化するタイミングに同期して前記第2の電圧を第2の電圧値だけ減少させ、その後、前記第1の比較結果が変化するタイミングに同期して前記第2の電圧を上昇させる。

(もっと読む)

可変抵抗回路および発振回路

【課題】回路規模を比較的小さくすることができ且つ高精度な抵抗値調整が可能な可変抵抗回路を提供し、また、かかる可変抵抗回路を用いた比較的回路規模が小さく高精度な発振周波数を実現し得る発振回路を提供する。

【解決手段】

可変抵抗回路は、複数の抵抗素子からなる第1の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路の所定のノードのうちの1つを選択的に第1の端子に接続せしめる第1のスイッチ部と、を有する第1の抵抗調整回路と、第2の端子に接続された複数の抵抗素子からなる第2の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路を第2の直列抵抗回路の所定ノードのうちの1つに選択的に接続せしめる第2のスイッチ部と、を有する第2の抵抗調整回路と、を含む。

(もっと読む)

大きな温度変動に対する発信周波数の安定化方法

【課題】

超高温から極低温までの温度変動が極めて大きい環境に設置される無線機器に適用できる発信周波数の安定化方法を提供する。

【解決手段】

複数の発信回路を備え、筐体内の温度を測定する筐体内温度測定ステップと、測定した筐体内温度Tと予め定められた温度T0、T1、・、Tk、・Tnとの大小関係から測定した温度範囲を判定する温度範囲判定ステップと、 温度範囲判定ステップが判定した温度範囲に応じて複数の発信回路のいずれかを選択する回路選択ステップとを有し、筐体内温度TがTk−1≦T<Tkの範囲であった場合に、回路選択ステップは当該温度範囲において、発信器の発信周波数が希望の範囲に納まるように予め調整されている発信回路等を選択する。

(もっと読む)

半導体装置

【課題】クロック周波数の設定を変えた場合でも電源や温度などに変動があっても、高精度なクロック信号を生成する。

【解決手段】周波数電圧変換回路13は、スイッチSW1,SW2から構成されるスイッチ部、静電容量素子C,C10〜C13、およびスイッチCSW0〜CSW3から構成されている。静電容量素子C10〜C13は、容量の絶対値が異なるもので構成され、設計者が意図する周波数範囲をカバーするよう設ける。静電容量値は、たとえば、2の重み付けがされている静電容量素子C11〜C13は、たとえば、4ビットの周波数調整制御信号SELC0〜SELC3に基づいて、スイッチCSW0〜CSW3が選択し、周波数の切り替えを行う。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

発振回路

【課題】発振周波数の精度を改善することが可能な発振回路を提供すること。

【解決手段】PTAT出力とCTAT出力とを加算して出力する基準電圧発生回路と、加算割合を切り替え温度に依存した基準電圧発生回路の出力の変動を最小化する第1切替手段と、基準電圧発生回路の出力に基づいて定電流を発生させる電流源と、基準電圧発生回路の出力に基づいて定電圧を発生させるレギュレータ回路と、一端が電流源に接続され電流源の定電流によって充放電される第1容量及び第2容量と、レギュレータ回路から供給される定電圧を電源として第2容量の他端を駆動するインバータと、電流源の定電流の値を切り替え発振周波数を調整する第2切替手段と、第1容量の容量値を切り替え第1容量及び第2容量の一端における発振振幅を調整する第3切替手段と、を備え、第1切替手段、第2切替手段、第3切替手段のトリミングによって所望の大きさの一定周波数を生成する。

(もっと読む)

タイマ

【課題】タイマにおいて、簡易な構成を実現しつつ、実時間の計測精度をより向上させることにある。

【解決手段】次回の停止時間T11は、記憶部36に記憶される周波数(前回の周波数)と、周波数演算部31により演算された周波数(今回の周波数)との差分及び前回の停止時間に基づき算出される。従って、前回の周波数と、今回の周波数との差分が大きい場合、例えば、温度変化が大きい場合には、次回の停止時間が短く設定される。このため、周波数の差分が大きい場合には周波数の補正の頻度が上がる。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

不揮発性のラッチ回路及び論理回路及びそれを用いた半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振回路、及びメモリシステム

【課題】クロックの周波数変動又はデューティ比変動を補正する。

【解決手段】電流源と負荷素子とを用いて一定遅延時間を生成してクロックの周波数を決定する発振回路10であって、クロックを積分する積分器15と、積分器15の出力電圧と基準電圧Vrefとを比較するコンパレータ16と、コンパレータ16の比較結果に応じて電流が変化する可変電流源PTとを含む。そして、発振回路10は、可変電流源PTの電流に応じてクロックの周波数を補正する。

(もっと読む)

発振回路

【課題】従来のゲート発振器のゲート発振器と入力信号間に内在する周波数オフセットの効果的な校正技術を提供する。

【解決手段】発振回路200は、ゲート発振器201と較正回路202とを備える。ゲート発振器201は、制御信号Sctrlに従って発振信号を生成し、ゲート信号SGを受信して、発振信号のエッジとゲート信号SGのエッジを配列させる。較正回路202は、ゲート発振器201に結合されて、第一クロック信号と第二クロック信号を受信し、第一クロック信号と第二クロック信号に従って、ゲート発振器201の配列操作を検出し、検出された配列操作に従って、制御信号Sctrlを生成する。

(もっと読む)

1 - 20 / 60

[ Back to top ]