Fターム[5J055AX22]の内容

Fターム[5J055AX22]の下位に属するFターム

外来ノイズ対策 (60)

チャタリング対策 (6)

スイッチングノイズ対策 (555)

Fターム[5J055AX22]に分類される特許

41 - 60 / 69

ホールドフリーレジスタセル

【課題】汎用的に使用することのできるホールドフリーレジスタセルを提供する。

【解決手段】ホールドフリーレジスタセル1は、クロック信号CKを切り替え信号として2つの入力信号の切り換えを行うマルチプレクサ11と、マルチプレクサ11の出力遅延時間に応じてクロック信号CKを遅延させ、クロック信号CKdとして出力する遅延回路12と、遅延回路12から出力されたクロック信号CKdの立ち下りでマルチプレクサ11から出力されるデータをラッチするラッチ回路13と、を備える。マルチプレクサ11は、クロック信号CKがデータ取り込みエッジ前のレベルである‘1’のときはデータ入力信号Dを出力し、クロック信号CKがデータ取り込みエッジ後のレベルである‘0’のときはラッチ回路の出力信号Q1を出力する。

(もっと読む)

出力回路

【課題】従来の出力回路は、出力端子から入力するノイズに対する耐性が低い問題があった。

【解決手段】本発明にかかる出力回路は、入力信号を受ける入力端子と、第1の電源gndと出力端子との間に接続される出力トランジスタMNoutと、入力端子及び出力トランジスタMNoutのゲートに接続され、入力信号に基づいて出力トランジスタMNoutのゲートに対する電流の吐き出し又は引き込みを制御する電流制御回路10と、第1の電源gndに接続される電圧生成回路11と、出力トランジスタMNoutのゲートと電圧生成回路11との間に接続され、入力信号により開閉状態が制御されるスイッチ回路S1とを備え、出力トランジスタMNoutのゲートと第1の電源gndとの電位差が所定の値以下になると、入力信号の電圧レベルにかかわらず、スイッチ回路S1はオフ状態となることを特徴とするものである。

(もっと読む)

高周波スイッチ回路

【課題】高周波スイッチ回路を介して伝達される高周波信号の二次高調波歪みを低減する。

【解決手段】高周波スイッチ回路において、受信側トランスファー回路(8)を構成するFET(11−20)を奇数段の直列構成とする。各FET段は、ソース電極とドレイン電極(S,D)の位置が交換されたMOSFETの並列体で構成するとともに、各MOSFET(11−20)のゲート幅を、一列のMOSFETで受信側トランスファー回路を構成する場合に比べて半減する。

(もっと読む)

ステートマシン

【課題】安全性と高速性を両立できるステートマシンを提供する。

【解決手段】状態保持部2は、動作開始トリガ信号「IO_RD」が入力されていない場合には第1の状態に、動作開始トリガ信号「IO_RD」が入力されている場合には第2の状態に、それぞれ状態を設定する。制御信号出力部3は、設定されている状態が現在まで第1の状態にあり、かつ動作開始トリガ信号「IO_RD」が現在入力されているという条件が成立している場合に限り、出力信号「RD_ENB1」を出力する。状態保持部2は、クロックをトリガとして状態を設定し、制御信号出力部3は、当該クロックをトリガとして上記条件を判定する。

(もっと読む)

半導体回路

【課題】電源立ち上がり時には即座に入力信号を反映した出力を行ない、電源立ち上がり後の定常状態では従来通りの遅延処理を行うことでノイズのフィルタ機能と信号の遅延機能を実現する半導体回路を提供する。

【解決手段】コンデンサを含み、入力信号に応じて前記コンデンサを充電および放電することで前記入力信号の伝達を遅延させる遅延回路と、前記遅延回路における前記コンデンサを充電する時間より短い時間で前記コンデンサを充電する充電手段と、パワーオンリセット回路と、論理ゲートとを備えている。前期パワーオンリセット回路は、電源の立ち上がり時から一定期間パルス状の信号を出力する。また、前記論理ゲートは前記パワーオンリセット回路の出力と前記入力信号との論理演算を行ない、その出力により前記電源の立ち上がり時から一定期間のみ前記入力信号に応じて前記充電手段を動作させる。

(もっと読む)

半導体装置

【課題】 高耐圧電力用集積回路が、スイッチングデバイスの導通状態から非導通状態への遷移、または非導通状態から導通状態への遷移に伴い発生する過渡的な電圧ノイズに曝された場合においても、スイッチングデバイスの誤動作を防止できる半導体装置を提供する。

【解決手段】 高電位側パワーデバイス駆動回路HDは、スイッチングデバイス12の導通状態が変化するような信号を伝達した際、スイッチングに伴い発生する誤信号をフィルタ回路8にて的確に除去できるよう、前記信号の伝達直後から一定期間、2つのレベルシフト用高耐圧NMOSのオン/オフ状態を必ず同一状態にするためのマスク信号発生回路18を有する。

(もっと読む)

パワーオンリセット回路

【課題】電源ラインに印加されたノイズによる誤動作を防止することのできるパワーオンリセット回路を提供する。

【解決手段】パワーオンリセット回路1は、1番目に投入されるロジック用正電圧電源VDDの立ち上がりから3番目に投入されるLCDパネル用正電圧電源VGGの立ち上がりまでの時間を検知してセット信号Sを発生させるセット信号生成部11と、そのセット信号Sによりセットされて内部回路用リセット信号を出力するフリップフロップ回路12と、2番目に投入されるLCDパネル用負電圧電源VEEの立ち下りを検知して発生させた信号を、LCDパネル用正電圧電源VGGの投入完了後まで遅延させ、LCDパネル用正電圧電源VGGの投入完了後のフリップフロップ回路12をリセット状態のままにする、フリップフロップ用リセット信号Rとして出力するリセット信号生成部13と、を備える。

(もっと読む)

負荷駆動回路およびそれを用いた点火装置

【課題】トランジスタのベースの電位が不安定になることで、寄生動作により保護回路が誤作動することを防止する。

【解決手段】保護回路7を逆トランジスタ方式で構成すると共に、各トランジスタ10〜12のベースをコレクタに接続することで、ベースの電位がコレクタの電位に固定できるようにする。これにより、従来のようにベースを開放した場合と比べて、ベースの電位を安定させられ、寄生ベースに対してノイズ的に電位が印加されても、寄生動作によりトランジスタがONしてしまう等の誤動作を防止することが可能となる。また、ベースの電位を安定させられることにより、サージ電流が発生したときに確実に保護回路7のトランジスタ10〜12をONさせられるため、保護回路7にてサージ電流を吸収してGNDに流れさせることが可能となる。

(もっと読む)

絶縁ゲート型デバイスの駆動回路

【課題】ターンオン時における損失およびノイズの温度依存性を低減することが可能な絶縁ゲート型デバイスの駆動回路を提供する。

【解決手段】IGBT21の駆動回路には、定電流を発生させる定電流源1、ターンオン時に定電流源1を介してIGBT21のゲートを電源電位Vcc側に接続するとともに、ターンオフ時にIGBT21のゲートをグランド電位GND側に接続する切り替え回路2およびIGBT21をターンオフさせる放電回路3を設け、駆動信号がロウレベルになると、Pチャンネル電界効果型トランジスタ14はオンするとともに、Pチャンネル電界効果型トランジスタ15はオフし、定電流源1を介してIGBT21をターンオンできるようにする。

(もっと読む)

マトリクススイッチ

【課題】任意の出力端子がオープン状態であっても、その出力端子に導通された各入出力端子のインピーダンス整合が取れるマトリクススイッチを提供する。

【解決手段】マトリクススイッチの各出力端子がそれぞれシャントを具備する。出力端子がオープン状態の時、出力端子にシャントが導通する。オープン状態の出力端子に導通した各入出力端子は、オープン状態の出力端子のシャントのインピーダンスで終端される。

(もっと読む)

低電力センサシステム用の容量性インタフェース回路

本開示は、低電力システム用の容量性インタフェース回路を記載する。容量性インタフェース回路は、高分解能及び低電力で、微小電子機械システム(MEMS)ベースセンサのような静電容量ベース変換器のノイズが非常に低い検知を達成するように構成される。容量性インタフェース回路は、差動増幅器と、相関トリプルサンプリング(CTS)とを使用して、kT/Cノイズ、並びに増幅器オフセット及びフリッカ(1/f)ノイズを増幅器の出力から実質的に消去又は少なくとも低減する。容量性インタフェース回路は、増幅器出力における過渡現象を落ち着かせることを可能にすることによって出力信号におけるグリッチング、すなわち、クロック過渡現象を低減する出力段をさらに備えることができる。このように、低電力システムにおいて回路を使用して、安定した低ノイズ出力を生成することができる。 (もっと読む)

クロック切り替え回路

【課題】

クロック信号を切り替えるとき、ハザードの発生を防止するとともに、クロック信号を切り替えるタイミングを任意に設定することができるクロック切り替え回路を提供する。

【解決手段】

クロック信号を選択するクロック選択信号および基準クロック信号から第1のクロック信号と第2のクロック信号における出力停止の期間を設定する設定信号を生成し、これらの設定信号に基づいて第1のクロック信号から第2のクロック信号に切り替えるとき、クロック信号が出力しない期間を設定する。

(もっと読む)

ディジタルアンプ装置及びディジタルアンプ装置のリセット方法

【課題】本発明は、簡易な構成でリセット時にスピーカ出力を停止できるようにする。

【解決手段】本発明は、リセット信号R1の供給を受けたことに基づいてリセット命令を認識し、当該リセット命令を認識したとき、PCM信号S1のゲインを0レベルに絞った後、ディザの重畳を停止し、そのようなゲイン調整後のディジタルオーディオ信号S3に応じたPWM信号P1´(+)、P1´(-)、P2´(+)及びP2´(-)を生成した後、当該PWM信号P1´(+)、P1´(-)、P2´(+)及びP2´(-)を用いてPWM信号増幅部15におけるスイッチング素子Tr1〜Tr4の動きを止めることにより、リセット時にポップノイズを発生させることなくスピーカSPの音声出力を停止させる。

(もっと読む)

信号読出し回路

【課題】 2つのサンプルホールド容量に保持された信号の差分を求める回路において、読出しゲインを1未満に設定した場合においても、減算後の出力値がサンプルホールド容量から信号を読み出す演算増幅器のオフセット電圧に影響されないことを特徴とする読出し回路を提供する。

【解決手段】 2つのサンプルホールド容量に保持された信号を各々読み出すために設けられた2つの演算増幅器において、各々の演算増幅器がリセット動作において、他方のオフセット電圧双方をサンプリングすることに加えて、自身のオフセット電圧をもサンプリングし、前記サンプリングされたオフセット電圧を読出し動作時に各々の演算増幅器出力に加算する手段を有することとする。

(もっと読む)

サンプリング回路

【課題】本発明の目的は、経済的で、技術的に耐久性があり、多方面で且つ簡単な方法で使用可能であるサンプリング回路を提供する。

【解決手段】この発明は、ブロードバンドの周期的入力信号の連続したサンプリングを行うためのサンプリング回路に関するものであり、パルス状のサンプリング信号が供給される非線形要素を設け、サンプリングを活性化して出力信号を形成することにある。また、本発明は、前記非線形要素として、電界効果トランジスタを設けるものである。

(もっと読む)

検知回路

【課題】電源電圧の急激な変化(電源ノイズ)による誤動作を防止できる検知回路を提供すること。

【解決手段】固定電位点と、パワーオン時、固定電位点からの電位差が変化していく可変電位点との電位差が所定の電位差となったことを検知する、半導体基板に形成される検知回路であって、可変電位点の電位にバイアスされる第1の半導体領域に形成され、可変電位点に接続される第1の抵抗体(r3)と、固定電位点の電位にバイアスされる第2の半導体領域に形成され、可変電位点に接続されない第2の抵抗体(r1)とを具備する。

(もっと読む)

半導体回路装置および高周波電力増幅モジュール

【課題】 SPDTスイッチにおけるスイッチ特性を改善し、高調波歪みを大幅に低減する。

【解決手段】 SPDTスイッチ2において、トランジスタQtx1〜Qtx4,Qrx1は、2つのゲートが設けられたデュアルゲートFETよりなり、これらトランジスタQtx1〜Qtx4,Qrx1には、ゲート制御電圧供給用抵抗であるR2〜R5,R11〜R14,R20〜R22とは別に新たに設けられたゲート耐電力容量間の抵抗R6,R7,R15,R16,R23,R24がそれぞれ接続されている。これら抵抗R6,R7,R15,R16,R23,R24は、トランジスタQtx1〜Qtx4,Qrx1におけるゲート−ソース間容量Cgs、ゲート−ドレイン間容量Cgdにかかる電圧Vgs,Vgdの位相が変化させ、それにより高調波歪み量を低減させる。

(もっと読む)

ドライバ切換方法およびドライバ切換装置

【課題】 部品点数を増やすことなく、内蔵ドライバおよび外部ドライバのいずれか一方を他方に切換えることができ、不要な電流およびノイズの発生を抑制することができるドライバ切換方法およびドライバ切換装置を提供する。

【解決手段】 インバータ17によってグランド端子21の電圧を監視し、グランド端子21とグランドとが接続され、グランド端子21の電圧が閾値未満であるとき、内蔵MOSFET16が駆動されていればそのまま駆動させ、外部MOSFET22が駆動されていれば外部MOSFET22から内蔵MOSFET16に切換えて駆動させる。グランド端子21が電源側に接続され、グランド端子21の電圧が閾値以上であるとき、外部MOSFET22が駆動されていればそのまま駆動させ、内蔵MOSFET16が駆動されていれば内蔵MOSFET16から外部MOSFET22に切換えて駆動させる。

(もっと読む)

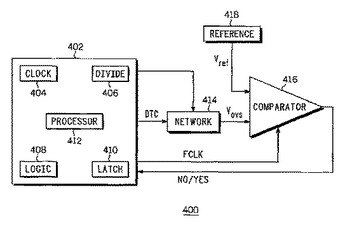

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

ゼロクロス検出回路

【課題】

商用電源の交流電圧に対する重畳ノイズ及び波形歪みに対して、ゼロクロスを定周期にかつ安定に検出することができるゼロクロス検出回路を実現する。

【解決手段】

交流電圧がゼロ電位をクロスするタイミングに同期したパルス信号を生成するゼロクロス検出回路において、前記交流電圧の正の半サイクル又は負の半サイクルの少なくともいずれかに同期した矩形波信号を生成する矩形波変換手段と、前記矩形波信号によりトリガされるモノステイブルマルチバイブレータ手段とを備える。

(もっと読む)

41 - 60 / 69

[ Back to top ]