Fターム[5J055AX64]の内容

Fターム[5J055AX64]に分類される特許

1 - 20 / 325

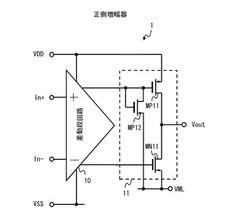

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

半導体チップ及びこれをパッケージングした半導体装置

【課題】サージ印加時における内部回路の誤動作を防止する。

【解決手段】半導体チップ(10)は、複数のパッド(P11、P12)と、複数のパッド(P11、P12)と電源ライン(15、16)との間に接続された複数の静電破壊保護素子(11H、11L、12H、12L)と、複数のパッドのうち少なくとも2つのパッド(P11、P12)に現れる印加電圧(S11、S12)が同一の論理レベルか否かを監視するサージ検出部(13)と、サージ検出部(13)の検出結果(S13)に応じてその動作が許可/禁止される内部回路(14)と、を有する。

(もっと読む)

低電圧検出回路

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

チョッパ型コンパレータ

【課題】動作時の貫通電流を低減させ、かつ動作スピードをあまり損なわないチョッパ型コンパレータを得る。

【解決手段】インバータと接地電圧端子間にNチャネル型MOSトランジスタ8を接続し、そのゲート端子に可変電圧源9を接続する。インバータと電源電圧端子間にPチャネル型MOSトランジスタ7を接続し、そのゲート端子に可変電圧源10を接続する。

(もっと読む)

スイッチ制御装置

【課題】互いにオンオフ状態が反転するように制御すべき2つのスイッチング素子の特性に応じて容易にデッドタイムを調整可能なスイッチ制御装置を提供する。

【解決手段】互いにオンオフ状態が反転するように制御する第1及び第2のスイッチング素子を備えるスイッチ制御装置であって、前記第1及び第2のスイッチング素子の内、一方のスイッチング素子に出力する制御信号をオフレベルに切替えた時点から、コンデンサの容量で設定される設定期間後に他方のスイッチング素子に出力する制御信号をオンレベルに切替える信号を出力する制御信号生成回路を備える。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

過電流検出装置

【課題】駆動に適した推奨値からずれた電気的特性を持つ負荷を駆動した場合でも誤検出を極力防止する。

【解決手段】しきい値生成回路11は、抵抗13、14にしきい値生成電流ITH、ITLを流してしきい値電圧VTH、VTLを生成し、コンパレータ12はシャント抵抗7の検出電圧Vaと比較して過電流検出信号Scを得る。しきい値補正回路17は、平均負荷電流、負荷電流の交流変化分、電源電圧VBが大きいほどしきい値電圧VTH、VTLを増やし、負荷4の温度が低いほどしきい値電圧VTH、VTLを増やす。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

ハイサイドスイッチ回路

【課題】所定のスイッチング動作を実行しつつ、破壊耐性を向上することが可能なハイサイドスイッチ回路を提供する。

【解決手段】電源電圧をスイッチングして出力するハイサイドスイッチ回路100は、電源電圧Vccが印加される電源端子1に一端が接続された第1の出力MOSトランジスタM1、第1の出力MOSトランジスタの他端に一端が接続され電圧出力端子2に他端が接続された第2の出力MOSトランジスタM2、第1の出力MOSトランジスタに流れる電流の検出信号を出力する電流検出回路6、第1の出力MOSトランジスタが線形領域で動作するように第1の出力MOSトランジスタのゲートに第1の制御電圧を印加する第1のゲートドライバ4、第2の出力MOSトランジスタが線形領域で動作するように第2の出力MOSトランジスタのゲートに第2の制御電圧を印加する第2のゲートドライバ5を備える。

(もっと読む)

トランジスタ回路、双方向スイッチ回路、ダイオード回路及びトランジスタ回路の製造方法

【課題】トランジスタのゲートへの電流を防ぐ。

【解決手段】ノーマリーオン型の第1トランジスタと、ドレインが、第1トランジスタのソースと接続され、第1トランジスタとカスコード接続されたノーマリーオフ型の第2トランジスタと、第2トランジスタのソースと第1トランジスタのゲートとの間に設けられた、第2トランジスタのソースから第1トランジスタのゲートへと流れる電流を抑制する第1電流抑制部とを備えるトランジスタ回路を提供する。

(もっと読む)

ゲート駆動回路

【課題】双方向に導通可能なスイッチング素子に逆電流が流れた場合であってもスイッチング素子の損失を低減させることができるゲート駆動回路。

【解決手段】双方向に導通可能なスイッチング素子SWと、スイッチング素子のオンオフを制御する制御部11と、スイッチング素子に流れる電流を検出する電流検出部12と、電流検出部によってスイッチング素子に逆方向の電流が流れたことが検出された時に、制御部によるオンオフの制御とは独立に、スイッチング素子をオン制御するゲート駆動部13とを備える。

(もっと読む)

半導体装置

【課題】駆動用のスイッチ素子によって出力端子からの出力を制御する半導体装置において、端子に静電気が印加されたときに、スイッチ素子をより確実に保護し得る構成を、装置構成の大型化を抑えて実現する。

【解決手段】半導体装置1は、高電位側電源又は低電位側電源の一方からなる基準部にスイッチ素子の第1端子が接続され、出力端子P1にスイッチ素子の第2端子が接続されている。また、スイッチ素子と並列に第1保護素子が設けられている。また、基準部とは逆側の電源(他方部)と出力端子の間には第2保護素子が接続されている。そして、基準部とは逆側の電源(他方部)側には無効化手段が接続され、出力端子へのサージ電圧の印加によって駆動電圧が発生した場合に、当該駆動電圧の発生後の所定時間、制御入力端子への通電信号の入力を無効化し、所定時間の経過後に無効化を解除するように機能している。

(もっと読む)

アクティブクランプ回路

【課題】アクティブクランプ動作期間を短縮するとともにESD耐量を向上させたアクティブクランプ回路を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第1のダイオードと、第1の抵抗と、第1および第2の制御回路と、を備えたことを特徴とするアクティブクランプ回路が提供される。前記第1のダイオードは、前記第1のスイッチ素子の両端にかかる過電圧によりブレークダウンする。前記第1の抵抗は、前記第1のダイオードの電流を検出する。前記第1の制御回路は、前記第1の抵抗の両端の電圧を増幅して前記第1のスイッチ素子の電流を制御する。前記第2の制御回路は、前記第1の抵抗の両端の電圧に応じて前記第1のスイッチ素子の導通を制御する。

(もっと読む)

トランジスタ駆動回路

【課題】より簡単な構成で、出力トランジスタを確実にオフ状態に維持できるトランジスタ駆動回路を提供する。

【解決手段】NチャネルMOSFET5とコイル2との共通接続点;出力端子OUTとグランドとの間にフライホイールダイオード3を接続する。FET5のゲートには、NPNトランジスタ6及びPNPトランジスタ7のプッシュプル回路により制御信号を出力し、トランジスタ7のベースとグランドとの間にNPNトランジスタ11を接続し、トランジスタ11のベースとグランドとの間にNチャネルMOSFET14を接続して、FET14にPWM信号を入力する。ダイオード13は、FET14がオフ状態になるとトランジスタ11のベースにベース電流を供給し、ダイオード15をダイオード13のアノードとトランジスタ6及び7のベースとの間に接続する。NPNトランジスタ22をFET5のゲートと出力端子との間に接続し、トランジスタ22をPWM信号に応じてFET5がオフする際にオンさせる。

(もっと読む)

電流駆動型半導体スイッチの駆動回路

【課題】従来の電流駆動型半導体スイッチ8の駆動回路は、駆動回路における電力損失を抑制するためにスイッチやスイッチを制御するための手段が必要となり部品点数が増える。

【解決手段】電源1と電流駆動型半導体スイッチ8のベース又はゲート端子の間に接続される負の温度特性を有する第1の可変抵抗10と、前記電流駆動型半導体スイッチ8のコレクタ又はドレイン電流による動作損失により過熱される熱伝導部11を備え、前記第1の可変抵抗10を前記熱伝導部11により熱が供給されるように配置する。

本発明により、簡単な構成で部品点数を増やすことなく駆動回路における電力損失を抑制することができる。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

半導体素子制御装置

【課題】駆動用半導体素子が意図せずに導通することを防止できる半導体素子制御装置を提供する。

【解決手段】駆動用トランジスタTr11は、一対の直流電源線13、14間に直流モータ12とともに直列に接続される。抵抗素子R13は、直流電源線13と駆動用トランジスタTr11のゲート端子との間に接続される。コンデンサC11および開路用トランジスタTr14の直列回路は、駆動用トランジスタTr11のゲート端子と直流電源線14との間に接続される。駆動制御回路15は、通常状態に設定されると、開路用トランジスタTr14をオンし、制御用トランジスタTr12、Tr13を通じて駆動用トランジスタTr11の導通状態を制御する。駆動制御回路15は、制御用トランジスタTr12、Tr13の双方がオフのとき、開路用トランジスタTr14をオフする。

(もっと読む)

高周波スイッチ回路、及び複合高周波スイッチ回路

【課題】 ゲート−ボディ間の電圧がMOSFETの耐圧以下とすることが可能な高い信頼性を有する高周波スイッチ回路を実現する。

【解決手段】 MOSFETと、前記MOSFETのゲート及びボディの電位を制御可能な制御回路を備えた高周波スイッチ回路であって、

前記制御回路はタイミング制御回路を備え、

前記タイミング制御回路は、前記高周波信号経路が接続状態から非接続状態に切り替わる時は、前記MOSFETのゲートの電位を切り替えた後にボディの電位を切り替えることが可能であり、かつ、非接続状態から接続状態に切り替わる時は、前記MOSFETのボディの電位を切り替えた後にゲートの電位を切り替えることが可能であることを特徴とする。

(もっと読む)

1 - 20 / 325

[ Back to top ]