Fターム[5J055DX16]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 主スイッチを構成する素子 (3,300) | 電界効果トランジスタ、FET (2,442) | 閾値 (83) | ディプレッション型(接合型ヲ除く) (50)

Fターム[5J055DX16]に分類される特許

1 - 20 / 50

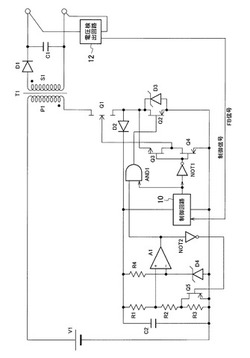

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置および電子機器

【課題】良好な逆回復特性と良好なEMCとを同時に実現することが出来て、かつ、従来の半導体装置よりも安価である半導体装置及び電子機器を提供する。

【解決手段】半導体装置1は、FET3のソースとMOSFET4のドレインとが接続されるとともに、一端が、FET3のゲートに接続され、他端が、MOSFET4のソースに接続される抵抗Rgsと、アノードが、FET3のゲートに接続され、カソードが、MOSFET4ソースに接続されるダイオードD1とを備える。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体スイッチ回路

【課題】一つの切替信号によってスイッチ動作を制御可能とする。

【解決手段】デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301が直列接続されて設けられ、デプレッション型電界効果トランジスタ201のゲートが第1のゲート抵抗器を介して接地される一方、エンハンスメント型電界効果トランジスタ301のゲートには、第2のゲート抵抗器を介して外部から切替信号が印加可能とされ、前記切替信号の電圧レベルを変化させることで、デプレッション型電界効果トランジスタ201とエンハンスメント型電界効果トランジスタ301の導通、非導通を相補的に切替可能にし、第1乃至第3の高周波入出力端子101〜103における高周波信号の入出力を制御可能としてなるものである。

(もっと読む)

駆動回路

【課題】 本発明の目的は、より小容量のキャパシタを同一チップ上に設けて半導体装置単体で負電源を必要とせずに、また部品点数を増加させることなく、スイッチングが可能な素子に適する駆動回路を提供することである。

【解決手段】 上記課題を解決する電圧制御型トランジスタの共振ゲート駆動回路は、前記型電圧制御型トランジスタのゲートあるいは前記ノーマリオン型電圧制御型トランジスタのゲートあるいは擬似ノーマリオフ素子の電圧制御端子に共振用インダクタと抵抗を直列に接続し、駆動回路には直列接続された相補的な2個のスイッチング素子を備えたことを特徴とするものである。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

パワーオンリセット回路

【課題】誤動作を起こす可能性があった。

【解決手段】電源投入初期もしくは電源電圧降下時にリセット信号を発生し初期化するパワーオンリセット回路であって、電源電圧に応じた電圧を分圧した第1の比較電圧を生成する第1の比較電圧生成部と、電源電圧に応じた第1の電圧を出力する基準電圧生成部と、電源電圧端子と第1のノードとの間に接続され、制御端子に前記第1の電圧を入力するデプレッション型の第1のトランジスタと、前記第1のノードと接地端子との間に接続され、制御端子が前記第1のノードに接続されるエンハンスメント型の第2のトランジスタと、を備え、前記第1のノードの電位に応じた電圧を第2の比較電圧として生成する第2の比較電圧生成部と、前記第1、第2の比較電圧との比較結果に応じてリセット信号を出力する比較器と、を有するパワーオンリセット回路。

(もっと読む)

ハイブリッドパワーデバイス

【課題】ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスにおいて、共振の発生を抑制しつつ、スイッチング損失を低減できるようにする。

【解決手段】ハイブリッドパワーデバイスを構成するノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とは、各FET2、4のソース及びドレインを互いに接続することによりカスコード接続されており、SiC−JFET2のゲートとSi−MOSFET4のソースはスイッチング速度調整用の抵抗10を介して接続されている。そして、この抵抗10にコンデンサ12を並列接続することにより、ハイブリッドパワーデバイスのスイッチング期間中の前半部分ではスイッチング速度を速くしてスイッチング損失を低減し、後半部分ではスイッチング速度を遅くして発振の発生を防止する。

(もっと読む)

半導体装置

【課題】高耐圧で低抵抗なダイオード及びスイッチを構成する電力用半導体装置を提供すること。

【解決手段】ソースが整流素子のアノードとなる第1のトランジスタと、第1のトランジスタより高耐圧で、ソースが第1のトランジスタのドレインに接続され、ゲートが第1のトランジスタのソースに接続され、ドレインが整流素子のカソードとなるディプレッション型の第2のトランジスタと、第1のトランジスタより高耐圧で、ドレインが第2のトランジスタと共通に接続されたディプレッション型の第3のトランジスタと、第1のトランジスタのソースの電圧と第3のトランジスタのソースの電圧とを比較し、第1のトランジスタのゲート電圧を制御する比較器と、を備える構成とする。

(もっと読む)

電圧変化検知装置

【課題】電界効果トランジスタの閾値電圧がばらついた場合にも、検知電圧のばらつきを低減でき、所望の電圧検知範囲で電圧変化を検知することができる電圧変化検知装置を提供する。

【解決手段】ドレインが電源電位に接続され且つソースが第1のノードにおいて第1の定電流源又は第1の抵抗に接続され且つゲートが固定電位に接続されている第1の電界効果トランジスタと、ドレイン及びゲートが電源電位に接続され且つソースが第2のノードにおいて第2の定電流源又は第2の抵抗に接続されている第2の電界効果トランジスタと、当該第1のノードの電位と当該第2のノードの電位との比較結果に応じて電源電位が所定の検知電位を跨いで変化したことを検知した旨の検知信号を生成する検知信号生成部と、を含む電圧変化検知装置。

(もっと読む)

半導体装置および電子機器

【課題】パワー半導体素子を駆動するためのドライバを低コストで得ることが可能な半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置101は、ハイサイド駆動部62からの駆動信号を受ける第1のスイッチング機能部と、ローサイド駆動部64からの駆動信号を受ける制御電極とを有する第2のスイッチング機能部とを備え、ハイサイド駆動部62は、ノーマリーオン型の電界効果トランジスタを含み、スイッチング制御信号の基準電圧を出力ノードの電位へシフトした駆動信号を出力し、第1のスイッチング機能部はノーマリーオン型の第1の電界効果トランジスタTr1を含み、第2のスイッチング機能部はノーマリーオン型の第2の電界効果トランジスタTr2を含み、ハイサイド駆動部62および第1の電界効果トランジスタTr1は第1の半導体チップ71に含まれている。

(もっと読む)

異常検出時急速放電回路

【課題】システムの異常時にオフする保護回路において、面積を増大させずに急速放電を実現する。

【解決手段】電源端子と出力端子の間に接続され、当該出力端子に接続される負荷に電流を出力する出力トランジスタを、システムの異常時にオフする保護回路であって、出力トランジスタの前記ゲート電極と電源端子との間に接続され、システムの異常時に、ゲート電極の電位を電源電位と等しくなるまで放電させる第1の放電部と、出力トランジスタのゲート電極とソース電極との間に接続され、システムの異常時に、ゲート電極の電位を出力電位と等しくなるまで放電させる第2の放電部とを有し、システムの異常を検出したら、出力トランジスタのゲート電極を電源電位と等しくなるまで放電させ、出力トランジスタのゲート電極の電位を出力電位と等しくなるまで放電させる。

(もっと読む)

高速整流回路

整流回路は、前記整流回路の整流信号出力ノードに接続された出力を有するデプレッション型半導体と、前記デプレッション型半導体のソースに接続されたカソードと前記デプレッション型半導体のゲートノードに接続されたアノードとを有するホットキャリア半導体ダイオードとを含む。前記整流回路は、前記ホットキャリア半導体ダイオードのアノードと前記デプレッション型半導体のゲートノードに接続され、交流電流(AC)入力信号を受信するように構成された交流電流(AC)入力ノードを含み得る。 (もっと読む)

エンハンスメントモード型およびデプレションモード型のワイドバンドギャップ半導体JFETのためのゲートドライバ

接合形電界効果トランジスタ(JFET)を駆動するための、DC接続2段ゲートドライバが提供される。JFETは、SiC JFETのようなワイドバンドギャップ接合形電界効果トランジスタ(JFET)であり得る。ドライバは、第1ターンオン回路、第2ターンオン回路及びプルダウン回路を含む。ドライバは、入力パルス幅変調(PWM)制御信号を受け入れて、JFETのゲートを駆動させるための出力ドライバ信号を発生させるように配置される。 (もっと読む)

半導体集積回路

【課題】昇圧回路がオフの際にバイパスされる電源電圧の電圧降下を抑圧可能とする。

【解決手段】動作制御スイッチ1がオフとされるに伴い昇圧回路101が動作停止状態となると、エンハンスメント型FET4はオフとなるが、デプレッション型FET3のゲートには、抵抗器5を介して昇圧用電源入力端子11に印加された電源電圧が供給されるため、デプレッション型FET3はオン状態となり、ダイオード等と比較して電圧降下が極小さなデプレッション型FET3を介して昇圧用電源入力端子11に印加された電源電圧にほぼ等しい電圧が出力端子13に得られるものとなっている。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】低電圧動作が可能でありながら、中間電源電圧の供給の有無に関わらず動作可能である表示パネルドライバを提供する。

【解決手段】データ線ドライバ3が、出力アンプ回路14と出力端子16A、16Bとを具備する。出力アンプ回路14は、電源電圧VDDと電圧VMLとの供給を受けて、正の駆動電圧を出力する正専用出力段24Aと、電源電圧と接地電圧の間の駆動電圧を出力可能な正負共用出力段28とを備えている。正専用出力段24Aのプルダウン出力トランジスタは、ディプレッション型であり、正負共用出力段28のプルダウン出力トランジスタは、エンハンスメント型である。電圧VMLがVDD/2に設定されたときは、正専用出力段24Aが正の駆動電圧を出力端子16A又は16Bに出力する。電圧VMLが接地電圧VSSに設定されたときは、正負共用出力段28が正の駆動電圧を出力端子16A又は16Bに出力する。

(もっと読む)

スイッチング回路及び電力変換回路

【課題】スイッチング回路や電力変換回路について、単アーム構造の場合でも導通制御端子電源の自給化を可能とする。

【解決手段】スイッチ素子17と制御端子電源用コンデンサ21を備え、制御端子電源用コンデンサの放電によりスイッチ素子のゲート端子に電圧を印加するようにされているスイッチング回路について、制御端子電源用コンデンサの負側端子は、主電源5の基準電圧端子18に接続するとともに、ハーフブリッジ回路22を介してゲート端子に選択的に接続できるようにし、制御端子電源用コンデンサの正側端子は、ハーフブリッジ回路24を介して主電源の正側端子15とスイッチ素子のソース端子に対して選択的に接続できるようにする。そして制御端子電源用コンデンサは、正側端子が主電源に接続することで充電がなされる一方で、負側端子がゲート端子に接続し、正側端子がソース端子に接続することで放電する。

(もっと読む)

1 - 20 / 50

[ Back to top ]