Fターム[5J055EZ37]の内容

電子的スイッチ (55,123) | 機能的回路 (8,211) | 論理素子(INVは除く) (1,593) | 加算器、減算器(演算器) (30)

Fターム[5J055EZ37]に分類される特許

1 - 20 / 30

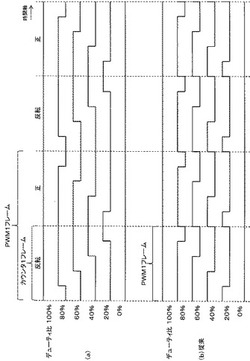

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

半導体スイッチング素子のゲート制御回路

【課題】スイッチング素子の発熱を抑制した過電圧抑制ゲート制御を確実、容易にし、さらにスイッチング素子を複数直列接続した半導体スイッチ回路における発振防止と分担電圧のバランス制御を確実、容易にする。

【解決手段】ゲートドライブ回路2によるゲート抵抗Aを通したIGBT1の主ゲート電流とは独立して、電圧補償ゲート制御回路3〜6はIGBT1のコレクタ・エミッタ間電圧Vceがしきい値を超えたときにゲート抵抗Bを通して電圧補償ゲート電流を注入し、電圧Vceがしきい値を下回ったときに電圧補償ゲート電流の注入をオフする。

ゲート抵抗Aの抵抗値に対してゲート抵抗Bの抵抗値を小さくする。電圧補償ゲート電流を注入した後にこのゲート電流の注入量とほぼ同じ電荷量分をIGBT1からゲート電流として引き抜く。

(もっと読む)

ゲートタイミング制御回路

【課題】半導体スイッチ,負荷電流,温度,主回路構成等によるサージ電圧の波形に応じて半導体スイッチの動作タイミングを調整することなく、各半導体スイッチの電圧分担を均等化させる。

【解決手段】直列接続された複数の半導体スイッチA,Bに出力されるゲート信号のタイミングを調整するゲートタイミング制御回路3において、コンパレータ4,4により、各半導体スイッチA,BのVce検出(A),(B)と、予め設定されたしきい値とを比較してVce検出における立ち上がりのタイミングを示すVce信号(A),(B)を出力する。そして、時間差制御部8において、ゲート信号に基づいて、前記各Vce信号(A),(B)の変化のタイミングが整合するように生成されたゲート出力(A),(B)をゲートドライバ2に出力する。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

MOSFETの電流判定装置

【課題】MOSFETのオン抵抗の温度特性に追随して高精度で電流レベル判定を行う。

【解決手段】MOSFET1に一体に感温素子4が設けられ、ドレイン/ソース間電圧Vdsと温度検出信号Vfを検出する。電圧Vdsは電圧検出部6に入力され、感温素子4の電圧Vfは第1および第2の補正回路8、9に入力される。MOSFET1のオン抵抗Ronの温度特性を第1および第2の温度領域のそれぞれに対応した近似直線で近似し、傾きを変えるように補正回路8、9で演算処理する。予め設定された判定電流値をRonの温度特性を考慮して判定電圧生成部11で判定電流に相当する判定電圧Vdsrefを生成する。これにより、比較器13で判定電流以上の電流がMOSFET1に流れたか否かを精度よく判定できる。

(もっと読む)

半導体スイッチング素子の駆動装置及び半導体スイッチング素子の駆動方法

【課題】PWM信号の傾きを制御する場合でも、本来意図したデューティと同じ期間だけ、半導体スイッチング素子をオンできる駆動装置を提供する。

【解決手段】ゲート駆動回路4が、入力されるPWM信号の立ち上がり及び立ち下がりにそれぞれ傾きを付与したゲート信号をNチャネルMOSFET1のゲートに出力する場合、デューティ調整部3は、NチャネルMOSFET1を介してランプ2に出力される電圧信号を検出し、入力信号の立ち上がりから電圧信号が立ち上がるまでの時間aと、PWM信号の立ち下がりから電圧信号が立ち下がるまでの時間bとを求め、デューティz=(x+a−b)に設定した駆動信号をゲート駆動回路4に出力する。

(もっと読む)

駆動装置

【課題】駆動回路やトランジスタにおいてばらつきがあっても、PWM駆動信号の駆動デューティ成分が小さい場合にも、上側トランジスタと下側トランジスタのシュート・スルー(貫通状態)を防止する。

【解決手段】入力端子の第2レベルまたは第1レベル信号に応じてスイッチングデバイスの制御端子に駆動電流をシンク出力するシンク回路と、スイッチングデバイスのオフ期間中に制御端子を経て容量性の電流をシンクする電流シンクトランジスタと、入力端子の信号に応じてソース回路の入力駆動信号と、シンク回路あるいは前記シンクトランジスタへの入力駆動信号とを生成するI/F回路と、シンク回路または前記シンクトランジスタへの入力駆動信号をシンク回路かあるいはシンクトランジスタのどちらに入力駆動信号として出力するかを選択するセレクタと、この選択動作を制御するセレクタへの選択信号を受ける入力端子とを備える。

(もっと読む)

信号処理装置、デジタルフィルタ、および、プログラム

【課題】タップ数を増やすことなく、信号通過帯域を制御する。

【解決手段】デジタルフィルタを用いて、デジタル信号を複素数の解析信号に変換する解析信号生成部と、非線形歪に応じた複素数の補償係数を用いて、解析信号を補正する補償部とを備え、デジタルフィルタは、デジタル信号のデータをn個(ただし、nは2以上の整数)のデータ系列に分割し、k番目(ただし、k=1、2、・・・、n)のデータ系列に、デジタル信号のn×L+k番目(ただし、L=0、1、・・・)のデータを割り当て、それぞれのデータ系列を、同一のフィルタ係数を用いてフィルタリングし、フィルタリングした各データ系列を合成して解析信号の虚数部分を生成する信号処理装置を提供する。

(もっと読む)

半導体回路、半導体回路の出力バッファ波形調整方法

【課題】調整回路を変更することなく出力バッファの波形の調整幅を広くすることができる半導体回路および、調整回路を変更することなく出力バッファのインピーダンス調整幅を拡大することができる半導体回路の出力インピーダンス調整方法並びに、調整回路を変更することなく出力バッファのスルーレート調整幅を拡大することができる半導体回路のスルーレート調整方法を提供する。

【解決手段】出力バッファ2のバッファ回路の並列数を調整する出力インピーダンス調整回路3の後段にNch出力バッファオフセット設定回路8とPch出力バッファオフセット設定回路9とを設けて、出力インピーダンス調整回路3が調整した並列数にNch出力バッファオフセット設定回路8とPch出力バッファオフセット設定回路9でオフセット値を加算する。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】回路の大規模化を抑えながら適正な位相補償を実現する。

【解決手段】演算増幅器OP1と、サンプルホールド回路の入力ノードNIと、接続ノードNSとの間に設けられたサンプリング用スイッチ素子SSと、接続ノードと、演算増幅器の第1の入力端子のノードであるサミングノードNEGとの間に設けられたサンプリング用キャパシタCSと、演算増幅器の出力端子とサミングノードとの間に設けられた帰還用スイッチ素子SFと、接続ノードと、演算増幅器の出力端子との間に設けられたフリップアラウンド用スイッチ素子SAと、サンプリング用キャパシタのサミングノード側の端子NCと演算増幅器の出力端子との間に設けられた位相補償用抵抗素子RPと、を含む。

(もっと読む)

容量性信号結合を用いた高電圧駆動回路及び関連する装置及び方法

【課題】ほぼ1つの面内に形成された駆動電極と感知電極とを備えた高電圧駆動回路を提供する。

【解決手段】装置は、駆動回路と感知回路との間の信号の転送を、駆動電極および感知電極を介して容量性手段によって行い、かつIGBTなどの高電圧装置を高電圧トランジスタを使用せずに駆動することが可能にされ、これにより高電圧ゲート駆動回路及びICを製造する場合、SOIなどの高価な製造工程を使用する必要がなくなる。

(もっと読む)

アナログ/ディジタル変換装置

【課題】低オフセットで高価な電圧源を不要にし、低コスト化を可能にした高精度のアナログ/ディジタル変換装置を提供する。

【解決手段】3相交流電圧または交流電流の第1〜第3のアナログ検出値にそれぞれ同一の直流量を加算する手段と、前記直流量加算後の第1〜第3のアナログ検出値を第1〜第3のディジタル検出値に変換する片極性のA/D変換器33と、第1のA/D変換値を(2×第1のディジタル検出値−第2のディジタル検出値−第3のディジタル検出値)/3により演算し、第3のA/D変換値を(2×第3のディジタル検出値−第1のディジタル検出値−第2のディジタル検出値)/3により演算し、第2のA/D変換値を(−第1のアナログ/ディジタル変換値−第3のアナログ/ディジタル変換値)により演算する手段(ソフトウェア)と、を備える。

(もっと読む)

電磁負荷装置の制御装置

【課題】電磁負荷装置の異常(断線又は短絡)を高精度に検出できる電磁負荷装置の制御装置を提供する。

【解決手段】電磁負荷装置(リニアソレノイド1)を駆動する電気回路(駆動回路108)と、該電気回路に流す目標電流値を設定する手段(目標電流値設定部101)と、該電気回路を流れる電流値をモニタする手段(電流モニタ回路4)と、前記モニタされる電流値と目標電流値との差分を算出する手段(電流偏差演算部102)と、該差分に基づいて、該モニタされる電流値が目標電流値と一致するように、前記電磁負荷装置への出力電流値を制御する制御手段と、前記モニタされる電流値と、前記目標電流値又は出力電流値と、の差分を所定時間積算する積算手段(電流偏差積算部104)と、該差分の積算値を閾値と比較することで、前記電磁負荷装置の異常を判定する異常判定手段(異常判定部105)と、を含んで構成した。

(もっと読む)

変調回路

【課題】スイッチ回路を用いた変調器では、このスイッチ回路後段の容量成分により変調波形振幅の変動を引き起こしていた。変調波形の振幅情報が重要な場合に、この振幅変動はノイズとして情報検出を阻害する大きな要因である。

【解決手段】本発明の変調回路は、スイッチ回路と加減算回路との間にフローティング抑制バッファ回路を設け、スイッチ回路の導通時に加減算回路の電流が前段回路に影響を与えるのを防ぎ、スイッチ回路の遮断時に加減算回路の入力電圧を定電圧にできる。スイッチ回路が遮断された側の加減算回路の入力電圧を定電圧にできるため、不要な直流電圧成分が加算されることのない正常な変調波形を出力できるようになり、波高値の変動を防ぐことができる。

(もっと読む)

データ出力装置及びこれを備える半導体メモリ装置

【課題】データの遷移を感知してスルー率を制御し、一定のスルー率を維持するデータ出力装置及びこれを備える半導体メモリ装置を提供すること。

【解決手段】複数のデータの遷移個数を感知してスルー率制御情報を出力するスルー率制御部と、前記スルー率制御情報を受信し、調整されたプルアップ駆動能力及びプルダウン駆動能力により、前記複数のデータをそれぞれ出力するデータドライブ部とを備えることを特徴とする。

(もっと読む)

電力変換装置の出力電圧検出回路

【課題】クロック周波数を高くする方法によらずに、電圧検出精度を向上させる。

【解決手段】被検出電圧、または、被検出電圧と第1または第2の基準電圧との加減算結果を選択して積分する積分回路203と、コンパレータ207,209と、ラッチ回路208,210と、これらの出力、クロック信号及びキャリア同期信号が入力され、積分回路203への入力電圧を選択する電圧検出制御回路206とを備え、第1キャリア周期でラッチ回路208の出力に応じて被検出電圧または被検出電圧と第1の基準電圧との加減算値を選択して積分し、第2キャリア周期でラッチ回路210の出力に応じて第1キャリア周期終了時の積分回路203の出力を初期値とし、第2の基準電圧を積分し、第1キャリア周期の積分期間のクロック信号の第1カウント値と、第2キャリア周期の積分期間のクロック信号の第2カウント値とを用いて被検出電圧を測定する。

(もっと読む)

電力変換装置および電力変換方法

【課題】所望の周波数帯域におけるノイズスペクトルを平坦化することができる電力変換装置および電力変換方法を提供することにある。

【解決手段】

インバータシステム1は、入力される電力を所望の形態に変換するスイッチング素子の開閉動作をデジタル制御する、演算装置を有する制御装置10は、スイッチング素子を開閉するための制御信号を生成する比較器8a、8b、8cに出力するキャリア信号の周波数fcを、離散的かつ周期的に時間変化させるキャリア周波数生成部9を備えている。キャリア周波数生成部9は、キャリア周波数fcの値fc11におけるm11次高調波の周波数m11×fc11と、キャリア周波数fcの他の値fc12におけるm12次高調波の周波数m12×fc12とが、演算装置のクロック周波数Fより低い周波数で重畳しないように、キャリア周波数fcの各値fc11およびfc12を選択した。

(もっと読む)

スイッチングレギュレータ

【課題】逆電流の発生を検出してから該逆電流を遮断するまでの遅延時間の短縮を図ることができ、効率を向上させることができる同期整流型スイッチングレギュレータを提供する。

【解決手段】第2のスイッチング素子M2と第3のスイッチング素子M3との接続部Lx3の電圧に基づいて、逆電流発生の兆候、又は逆電流発生を検出した場合は、コンパレータ33により第3のスイッチング素子M3をオフさせ、第2のスイッチング素子M2と接地電圧との接続を遮断するようにし、出力端子OUTから接地電圧への逆電流をなくすようにした。

(もっと読む)

1 - 20 / 30

[ Back to top ]