Fターム[5J055FX24]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 時限用コンデンサを有する (279)

Fターム[5J055FX24]の下位に属するFターム

複数の時限用コンデンサを有する (13)

定電流源で充電するもの (5)

スイッチがコンデンサに直列に接続 (112)

スイッチがコンデンサに並列に接続 (83)

Fターム[5J055FX24]に分類される特許

1 - 20 / 66

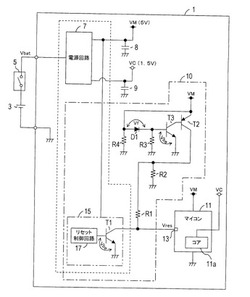

リセット回路

【課題】マイコンのリセット端子をトランジスタによってグランドに接続することによりマイコンにリセットをかけるリセット回路において、リセット動作不能な電源電圧の領域を無くす。

【解決手段】リセット回路10は、マイコン11のリセット端子13を電源電圧(以下、VM)にプルアップする抵抗R1と、VMが所定値未満のときにトランジスタT1をオンしてリセット端子13を0Vにするリセット信号出力回路15とに加え、オンすることで抵抗R1の上流側にVMを供給するトランジスタT2と、抵抗R1の上流側とグランドとの間に接続された抵抗R2と、トランジスタT1がオン可能なVMの最低値(Vbe)より高く、上記所定値よりは低い電圧(Vbe+ダイオードD1のVf)を動作閾値電圧とし、VMがその動作閾値電圧未満である場合にトランジスタT2をオフさせておいて、マイコン11のリセットを確保する回路T3,D1,R3,R4とを備える。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限がある半導体スイッチング素子を高い周波数で高速にスイッチングできる駆動回路を提供する。

【解決手段】通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させる。具体的にはダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限があるスイッチング素子を高い周波数で高速にスイッチングできる半導体スイッチング素子の駆動回路を提供する。

【解決手段】ダイオードDa1及びスイッチSa1,スイッチSa2及びダイオードDa2で正側,負側直列回路を夫々構成し、コンデンサC1,C2を正側,負側直列回路に夫々並列に接続し、スイッチSa1,Sa2によりゲート駆動用電源3とコンデンサC1,C2の間の接続形態を切替える。スイッチS1及びS2の共通接続点とFET1のゲートとの間に抵抗素子Rgを接続し、前記ゲートとゲート駆動用電源3の正側端子との間にスイッチS3を配置する。通電制御回路4は、スイッチSa1,Sa2,S1〜S3を制御してコンデンサC1,C2を充電する経路,FET1のゲートを充電する経路,ゲートの電位が電圧VGを超えようとする際にゲート駆動用電源3に還流電流を流す経路と、FET1のゲートを放電する経路を形成する。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

半導体装置

【課題】従来よりも低消費電力かつ小面積であるとともに設計性のよいパワーオンリセット回路またはスタートアップ回路を備えた半導体装置を提供する。

【解決手段】半導体装置1は、出力部10と、第1および第2の電位設定部8,9とを備える。出力部10は、電源投入時に、中間電位ノードN1の電位に応じた制御信号RSを内部回路3に出力する。第1の電位設定部8は、第1の基準電位ノードVDDと中間電位ノードN1との間に接続された第1の導電型を有するエンハンスメント型の第1のMOSトランジスタEPを含む。第2の電位設定部9は、第2の基準電位ノードGNDと中間電位ノードN1との間に直列接続された第2の導電型を有するディプレッション型の複数の第2のMOSトランジスタDN1_〜DN_nを含む。複数の第2のMOSトランジスタDN1_〜DN_nの各々において、ソースとウェルとが互いに接続される。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、消費電力を低減することの可能なインバータ回路およびそれを備えた表示装置を提供する。

【解決手段】7Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr7のゲートに接続されている。トランジスタTr7のソースには、トランジスタTr2のゲートが接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3,Tr6がオフしたときに、Vddが充電された容量素子C1によって、トランジスタTr7のゲートがVSS+Vth7以上の電圧にチャージされ、トランジスタTr7がオンし、さらにトランジスタTr2がオンする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

信号生成回路

【課題】回路に設けた容量をソフトスタート機能と共用可能でき、タイマ時間の設定の自由度が高くて精度の良いタイマ機能を実現可能な信号生成回路を提供する。

【解決手段】電流供給回路11から供給する電流Issを、回路に設けた共用する容量(Css)12に供給するとともに、差動増幅器21の比較入力としてクランプ回路20に加える。クランプ回路20は、容量(Css)12の電流供給回路11側端子電圧Vssとソフトスタート完了指示電圧Vc10を比較することにより、端子電圧Vssがソフトスタート完了電圧Vc1を上回った場合に、容量(Css)12に供給される電流Issを全て引き込むようしてクランプ機能を働かせる。クランプ回路20がクランプ作動状態に入る少し前に、差動増幅器21の出力Vo1が単相増幅器31のしきい値電圧Vtaを過ぎると、電流Issの切り替え(電流値Iss1から電流値Iss2への切り替え)が行われる。

(もっと読む)

ソースドライバ及び液晶表示装置

【課題】液晶表示パネルを駆動するソースドライバのソースアンプの振幅差偏差を向上する。

【解決手段】液晶表示パネルを駆動するソースドライバ100が、画素データDINに対応する階調電圧を出力するD/Aコンバータ23と、階調電圧に対応する駆動電圧を出力するソースアンプ25とを備えている。ソースアンプ25は、第1及び第2NMOSトランジスタMN11,MN12を含むNMOS差動対と、第1及び第2PMOSトランジスタMP11,MP12を含むPMOS差動対と、NMOS差動対とPMOS差動対に流れる電流に応じて駆動電圧を出力する出力回路部(2,3)と、第1及び第2入力レベル変換回路4、5とを備えている。第1及び第2入力レベル変換回路4、5は、ソースアンプ25に入力される階調電圧と、ソースアンプ25の入力にフィードバックされる駆動電圧とに対し、駆動電圧の極性及び/又は階調電圧に応じて入力レベル変換を行う。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

パルス発生回路

【課題】電源オフした直後に電源を再投入しても正常にパルス生成動作を再開できるようにすること。

【解決手段】このパルス発生回路は、第1のDフリップフロップ回路11のセット端子及びリセット端子をそれぞれコンデンサC11,C12を介してグラウンド又は電源に接続し、第1のDフリップフロップ回路11のQ出力端子とセット端子間及びQバー出力端子とリセット端子間にそれぞれ第1の抵抗R11,R12を接続し、前記セット端子、リセット端子、Q出力端子又はQバー出力端子のうちのいずれかの端子とグラウンド間に第2の抵抗RGを接続している。また、第1のDフリップフロップ回路11のQ出力端子を第2のDフリップフロップ回路20のクロック端子に接続し、第2のDフリップフロップ回路20のデータ端子及びセット端子を電源に接続し、第2のDフリップフロップ回路20のQバー出力端子とリセット端子間に第3の抵抗R2を接続した。

(もっと読む)

半導体集積回路

【課題】専用回路部が誤動作を起こすことを防止する半導体集積回路を提供することを目的とする。

【解決手段】電源部11と、制御回路部12と、専用回路部13を有する半導体集積回路であって、前記電源部に設けられ第1電源を生成して前記専用回路部に供給する第1電源回路11aと、前記電源部に設けられ前記第1電源より電圧の低い第2電源を生成して前記制御回路部に供給する第2電源回路11bと、前記電源部に設けられ前記第2電源が立ち上がったのちリセット解除を指示するリセット信号を生成して前記専用回路部に供給するリセット回路11cとを有し、前記制御回路部が動作を開始したのち前記専用回路部のリセットを解除する。

(もっと読む)

無電圧接点入力回路

【課題】 フォトカプラやDC−DCコンバータを用いない無電圧接点入力回路を提供する。

【解決手段】 信号入力部1に入力された無電圧接点信号が「開」か「閉」かを判断するCPU2と、入力された無電圧接点信号を、H/L信号としてCPU2に通知するためのインターフェース回路3とを有し、インターフェース回路3は、信号入力部1にコンデンサを設け、CPU2の入力ポートPiに無電圧接点信号の開/閉に対応するH/L信号を出力する出力トランジスタTr4と、コンデンサC1,C2を充電すると共に出力トランジスタTr4を起動するための起動トランジスタTr1と、コンデンサC1,C2の充電電荷を放電させるための放電トランジスタTr2とを備え、CPU2が入力ポートPiに入力される信号H/Lの状態を所定のタイミングで見ることで無電圧接点信号の開/閉を判断する。

(もっと読む)

負荷駆動装置及び負荷駆動制御装置

【課題】パワーオンリセット以外のリセットの場合に負荷を駆動し続け、パワーオンリセットの場合には、例えば負荷を駆動するための信号が与えられるまで、負荷を駆動しないようにすることが可能な負荷駆動装置、及び該負荷駆動装置を備える負荷駆動制御装置を提供する。

【解決手段】電源ラインBL側と接地電位との間に直列に接続されたコンデンサC1及び抵抗R1からなる微分器が電源ラインBLの電圧の立ち上がりを微分した微分電圧に基づいて、入力端子221,231を電源ラインBLに夫々プルアップする抵抗R4,R14の入力端子221,231側と接地電位との間にダイオードD3,D13を介して接続されたFETQ1が、少なくとも入力端子221,231に入出力ポート35,36より負荷L1,L2を駆動するための信号を与えられるまで導通する。

(もっと読む)

スイッチング出力回路およびスイッチング電源

【課題】貫通電流を防止する。

【解決手段】ハイサイドトランジスタ16およびローサイドトランジスタ18それぞれのゲート電極30、40は、異なる位置に設けられた駆動用コンタクト32(42)と検出用コンタクト34(44)を介して信号を入出力可能に構成される。ハイサイドドライバ22は、制御信号S1が第1レベルであり、かつローサイドトランジスタ18側の検出用コンタクト44の信号SLがローレベルのとき、ハイサイドトランジスタ16側の駆動用コンタクト32にローレベルを印加する。ローサイドドライバ24は、制御信号S1が第2レベルであり、かつハイサイドトランジスタ16側の検出用コンタクト34の信号SHがハイレベルのとき、ローサイドトランジスタ18側の駆動用コンタクト32にハイレベルを印加する。

(もっと読む)

半導体装置

【課題】保護回路において、所望の遅延時間を実現する。また、遅延回路の小型化を図り、消費電力を低減させる。

【解決手段】遅延回路100は、第1のインバータ101〜第3のインバータ103、第4のpチャネルMOSFET7、第4のnチャネルMOSFET8、遅延抵抗121およびキャパシタ122で構成されている。遅延抵抗121は、第1のインバータ101の出力端子と第2のインバータ102の入力端子の間に接続されている。第4のnチャネルMOSFET8のゲート端子は、遅延抵抗121と第2のインバータ102の入力端子の間のノード113に接続されている。第4のnチャネルMOSFET8のゲート端子とドレイン端子の間には、キャパシタ122が接続されている。第4のnチャネルMOSFET8の帰還容量を用いることで、キャパシタ122の容量を、キャパシタ122の物理的な静電容量よりも擬似的に大きくする。

(もっと読む)

カウンタ回路およびタイマー回路ならびにカウント方法および計時方法

【課題】最大カウント値を大きくすると、カウンタ回路の規模が増大する。

【解決手段】駆動部20は、所定のイベントが発生するごとに、所定回数、極性を交互に反転させながら強誘電体10に駆動電圧Vdrv1、Vdrv2を印加する。判定部30は、強誘電体10の分極量を測定し、イベントの発生回数を判定する。この判定部30は、電気的信号が印加されたことに起因する強誘電体10の疲労特性を利用して、経過時間が所定のしきい値を超えたか否かを判定する。

(もっと読む)

パワーオンリセット回路

【課題】リセットタイミングのバラツキを低減するとともに、通常動作時の消費電力を低減し、且つ回路面積を小さくする低電流小型のパワーオンリセット回路を提供する。

【解決手段】電源電圧を分圧する複数のトランジスタからなる分圧回路と、分圧回路で分圧された電圧に基づいて電源電圧が所定値以上か否かを検出する回路とからなる電圧検出回路と、電圧検出回路の出力信号が入力するインバータと、インバータの入力と接地との間に接続されたトランジスタと、を備えるパワーオンリセット回路である。

(もっと読む)

1 - 20 / 66

[ Back to top ]