Fターム[5J055FX28]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 時限用コンデンサを有する (279) | スイッチがコンデンサに並列に接続 (83)

Fターム[5J055FX28]に分類される特許

1 - 20 / 83

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

リセット回路

【課題】ウォッチドッグのための特殊な構成を追加することなく、マイコンラッチ時に自動的かつ確実にマイコンにリセットをかける

【解決手段】水晶振動子Xtalを用いた水晶発振回路からクロック信号を入力されるマイコン200のリセット回路100であって、マイコン200は、出力がHighとLowとで周期的に変動するGPIO端子201を備え、クロック信号の入力が停止されたときに自動的にリセット状態となる構成とされ、リセット回路100は、GPIO端子201の出力をコンデンサを用いて平滑し、平滑電圧がHighとLowの中間電位のときは水晶振動子Xtalの負性抵抗より小さい抵抗を発生して水晶振動子Xtalに印加し、平滑電圧がHighとLowのいずれかになると水晶振動子Xtalの負性抵抗以上の抵抗を発生して水晶振動子Xtalに印加する。

(もっと読む)

スイッチング回路及び半導体モジュール

【課題】スイッチング制御する制御回路の負担を軽減するスイッチング回路を提供する。

【解決手段】第1のスイッチング素子の制御電極と第1のスイッチング素子をスイッチング制御する制御回路との間に接続される抵抗と、第1のスイッチング素子の制御電極と第1のスイッチング素子の低電位側電極との間に接続される第1のコンデンサと、第1のコンデンサと直列に接続される第2のスイッチング素子とを備え、第2のスイッチング素子の高電位側電極は、第1のスイッチング素子の制御電極に電気的に接続され、第2のスイッチング素子の低電位側電極は第1のスイッチング素子の低電位側電力端子に電気的に接続され、第2のスイッチング素子の制御電極は、抵抗と制御回路の間に接続されている。

(もっと読む)

表示装置

【課題】表示装置の走査信号線の駆動回路において、走査信号線の出力波形なまりを改善し、表示品質を高めた表示装置を提供する。

【解決手段】表示装置は、複数の信号線Gnに対して、順に画素トランジスタを導通させる電位であるアクティブ電位を印加する駆動回路210を備え、前記駆動回路210は、前記複数の信号線のうちの一の信号線である出力信号線の一端に、より上位の前記出力信号線において出力されるアクティブ電位が入力されることに起因して、クロック信号を印加してアクティブ電位を出力させる主駆動回路240と、前記出力信号線の他端、及び前記クロック信号の信号線が、ソース/ドレインを介して接続されたトランジスタである補助トランジスタを含む補助駆動回路250と、を有する。

(もっと読む)

ESD保護回路

【課題】ESDパルスをもれなく検出し、かつ通常の電源投入時やスパイクノイズ印加時の誤検出を抑制する。

【解決手段】第1検出回路7はESDパルスの印加開始時から第1所定時間だけ第1検出信号を出力する。第2検出回路9は、第1検出信号を受け、かつESDパルスの印加が第2所定時間だけ持続したときに第3所定時間だけ第2検出信号を出力する。第1所定時間は電源の立ち上がり時間よりも短い。第2所定時間は第1所定時間よりも短く、かつスパイクノイズの印加時間よりも長い。第3所定時間はESDパルスの印加時間よりも長い。クランプ回路11は、第1検出信号及び第2検出信号の少なくとも一方が出力されているときはゲート端子47をGND端子3とは絶縁する。プルアップ回路13は、ゲート端子47を、第2検出信号が出力されているときは電源端子1に接続し、第2検出信号を出力されていないときは電源端子1とは絶縁する。

(もっと読む)

半導体装置

【課題】入力信号が有する2値の電位に関わらず、正常に動作させることが可能なデジタ

ル回路の提案を課題とする。

【解決手段】半導体装置の一態様は、入力端子、容量素子、スイッチ、トランジスタ、配

線、及び出力端子を有し、前記入力端子は、前記容量素子の第1の電極に電気的に接続さ

れ、前記配線は、前記スイッチを介して前記容量素子の第2の電極に電気的に接続され、

前記トランジスタのゲートは、前記容量素子の第2の電極に電気的に接続され、前記トラ

ンジスタのソース又はドレインの一方は、前記配線に電気的に接続され、前記トランジス

タのソース又はドレインの他方は、前記配線に電気的に接続されていることを特徴とする

。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

モータ駆動装置

【課題】モータ駆動装置内で駆動信号経路のオープン故障が発生した場合にも、モータ駆動回路のトランジスタを安全、確実にオフ状態とする。

【解決手段】モータ駆動回路3のトランジスタQ1〜Q6に駆動信号を供給してトランジスタをオン・オフ制御するトランジスタ駆動回路5を備えたモータ駆動装置において、トランジスタQ1〜Q6のゲート・ソース間(またはベース・エミッタ間)に、トランジスタ駆動回路5からトランジスタQ1〜Q6への駆動信号経路上にオープン故障が発生した場合に、トランジスタQ1〜Q6をオフさせるための抵抗体Rgs及び/又はコンデンサCgsを接続すると共に、抵抗体、コンデンサをトランジスタの内部に配置したもの。

(もっと読む)

半導体装置及びサンプルホールド回路

【課題】ON状態での低いオン抵抗とOFF状態での小さいオフリーク電流を持つMOSトランジスタスイッチを用いた半導体装置及びサンプルホールド回路を実現する。

【解決手段】PMOSトランジスタM11がON状態の場合には、PMOSトランジスタM12がON状態になりPMOSトランジスタM11のバックゲート端子をPMOSトランジスタM11のソース端子に接続し、PMOSトランジスタM11がOFF状態の場合には、PMOSトランジスタM13がON状態になりPMOSトランジスタM11のバックゲート端子を電源電圧端子VDD1に接続する。

(もっと読む)

保護回路

【課題】より効果的に逆起電圧の発生を抑え、過電圧による素子の破壊を防ぐことが可能な保護回路を提供する。

【解決手段】第1の実施形態の保護回路2は、抵抗値可変スイッチ10,過電流検出部20,制御電圧印加部30,容量部40,制御端子電圧変更部50および外部端子11を備える。抵抗値可変スイッチ10は、制御端子10a,第1端子10bおよび第2端子10cを有する。制御端子電圧変更部50は、抵抗値可変スイッチ10の制御端子10aと基準電位端子との間に直列的に設けられたスイッチ51および抵抗器52を含む。

(もっと読む)

遮断装置

【課題】スナバ回路を用いることなく、半導体遮断器を破損させずに電流を遮断する。

【解決手段】制御部11が、電流検出部13にて検出された電流値が所定の電流値に達すると短絡や過電流が発生したと判断し、半導体遮断器12にて電流の遮断を開始するように制御する。そして、正極線51に流れる電流を半導体遮断器12よりも直流電源80側で分岐させて、コンデンサ14に流入させて半導体遮断器12を破損させないようにしている。また、半導体遮断器12にて電と流を遮断した後も、半導体遮断器12の電気的接続状態をオフ状態から一時的にオン状態に切り替えて、コンデンサ14に充電された電荷を放電させるようにして、コンデンサ14の容量が小さくてもすむようにしている。

(もっと読む)

タイマー回路

【課題】容量素子を利用したタイマー回路において、容量素子が短絡状態になったことを検出することができるタイマー回路を提供する。

【解決手段】容量素子の充電又は放電が開始されてから、容量素子Cの電位と、グランドGDNの電位より高く電源VDDの電位より低い基準電圧VREF_Hの電位とを比較して、容量素子Cの電位が基準電圧VREF_Hの電位に到達した場合に、予め定められたタイムアップ信号を出力するコンパレータCMP1と、容量素子Cの電位が、グランドGNDの電位より高く基準電圧VREF_Hの電位より低い基準電圧VREF_Sの電位より高くなるように制御する制御部と、容量素子Cの電位と基準電圧VREF_Sの電位とを比較して、容量素子Cの電位が基準電圧VREF_Sの電位より低くなった場合に、前記容量素子の短絡状態が検出された旨を示す短絡検出信号を出力するコンパレータCMP2と、を備える。

(もっと読む)

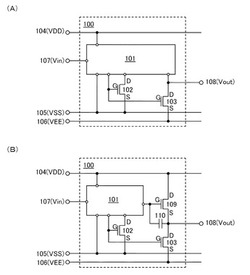

インバータ回路および表示装置

【課題】より少ない素子数で、さらなる高速化を実現することの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備える。インバータ回路20は、並列関係にあるトランジスタTr21およびトランジスタTr22と、これらのトランジスタTr21,Tr22のゲート電圧Vgの補正を行う閾値補正回路21を有する。閾値補正回路21は、トランジスタTr21のゲートに対して、トランジスタTr21の閾値電圧Vth1(図示せず)またはトランジスタTr21の閾値電圧Vth1に対応する電圧をオフセットとして設定する。閾値補正回路21は、さらに、トランジスタTr22のゲートに対して、トランジスタTr22の閾値電圧Vth2(図示せず)またはトランジスタTr22の閾値電圧Vth2に対応する電圧をオフセットとして設定する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr2のソースに接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3がオフしたときに、Vdd2が充電された容量素子C1によって、トランジスタTr2のゲートがVSS+Vth2以上の電圧にチャージされ、トランジスタTr2がオンする。

(もっと読む)

電流源回路

【課題】矩形波の信号入力に応じて出力する出力電流の波形を矩形波に近づけることが可能な電流源回路を提供する。

【解決手段】電流源回路は、電圧端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第2のMOSトランジスタと、電圧端子に一端が接続された第3のMOSトランジスタと、第3のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第4のMOSトランジスタと、を備える。この電流源回路は、第1のMOSトランジスタおよび第4のMOSトランジスタに電流が流れるように第1の入力端子にバイアス電圧が印加された状態で、第2の入力端子に印加されるスイッチ電圧に応じて、第2のMOSトランジスタおよび第3のMOSトランジスタのオン/オフを同期して制御する。

(もっと読む)

負荷駆動装置及びその制御方法

【課題】外乱等の影響を受けた場合でも、スイッチング電源のデッドタイムの最適値を誤認する可能性を低減し、これによって電力損失を低減することが可能な負荷駆動装置を提供する

【解決手段】負荷駆動装置1は、直流電圧源Vccに直列に接続された2つのスイッチング素子Q1,Q2を有するスイッチング電源回路2と、スイッチング素子Q1,Q2をオン/オフさせる駆動信号を供給するスイッチ制御回路3と、2つのスイッチング素子Q1、Q2の両方がオフとなるデッドタイムを設定するデッドタイム設定回路6とを備えており、デッドタイム設定回路6は、デッドタイムの最適値となり得る候補値を探索する最適値探索部9と、最適値探索部9から候補値を受け取って、候補値を最適値とするか否かを確率に基づいて決定する確率演算部10とを備えている。

(もっと読む)

電圧検出回路、及び電源装置

【課題】瞬停の度に電力を遮断せずともリセット用コンデンサを確実に放電可能とする。

【解決手段】スイッチング制御回路5への入力電圧の降下を検出し、当該スイッチング制御回路5に設けられたリセット用コンデンサC2を放電する放電回路55を作動させる電圧検出回路53であって、前記入力電圧の降下検出後の復電時から所定時間Ta後に電圧が復電判定値Vrに至る比較用信号を前記入力電圧から生成し、前記入力電圧の降下検出時から前記比較用信号の電圧が前記復電判定値Vrを超えるまで前記放電回路55の作動を継続して前記リセット用コンデンサC2を放電するようにした。

(もっと読む)

パワーオンクリア回路

【課題】電源電圧の立ち上がり状態の影響を受けないクリア信号を生成、出力するパワーオンクリア回路を提供する。

【課題の解決手段】パワーオンクリア回路は、電源の投入によってパルスを発生するパルス発生回路1と、発生したパルスを遅延して出力する遅延回路5と、遅延されたパルスが入力する縦続接続した2段のインバータ6,7と、遅延回路5の前段側の出力が入力する入力端子と1段目のインバータ6の出力が入力する入力端子とを有するNOR回路8とを備え、NOR回路8の出力を電源電圧の立ち上がり状態の影響を受けない第1のクリア信号とし、インバータ7の出力を電源電圧の立ち上がり状態に応じた第2のクリア信号とするものである。

(もっと読む)

時定数回路、スイッチ回路、DC/DCコンバータ及び表示装置

【課題】単調に減衰するだけの出力電圧特性に比べて、急峻に減衰した後に緩やかに減衰する出力電圧特性が得られる時定数回路等を提供する。

【解決手段】時定数回路10は、抵抗素子111と容量素子121との並列回路131,…が第一の端子14と第二の端子15との間に複数直列に接続されて成る直並列回路16と、第二の端子15に接続された第三の端子17と第四の端子18との間に接続された分圧用抵抗素子19と、を備えている。並列回路131は抵抗素子111と容量素子121とから成り、並列回路132は抵抗素子112と容量素子122とから成り、・・・、並列回路13nは抵抗素子11nと容量素子12nとから成る。nは、並列回路131〜13nの数であり、2以上の整数である。

(もっと読む)

1 - 20 / 83

[ Back to top ]