Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

201 - 220 / 1,327

同期回路

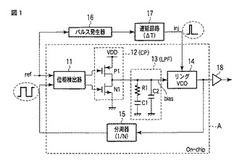

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

デューティ比自動調整コンパレータ回路

【課題】電源電圧などの回路の動作条件の変動に関わらず、デューティ比の変動を抑圧、低減する。

【解決手段】差動増幅回路1と、この差動増幅回路1において差動対を構成する2つのMOSトランジスタ21,22のソース同士の接続点における電位に基づいて閾値電圧を生成する閾値電圧生成回路2と、インバータ動作における閾値電圧を、閾値電圧生成回路2により生成された閾値電圧に設定可能に構成された閾値電圧可変インバータ回路3とが設けられることにより、インバータ動作における閾値電圧が、差動増幅回路1の出力振幅の中心電圧に設定でき、電源電圧の変動などが生じてもインバータの入出力間におけるデューティ比の変動が抑圧、低減できるものとなっている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のチップ面積とコストの増加や、電気的特性の問題を招くことなく、出力バッファ回路の出力電圧のリンギングを抑制する。

【解決手段】半導体集積回路200は、電源線10、電源抵抗11、接地線12、接地抵抗13、出力バッファ回路14,15,16、電源端子PVdd、接地端子PVss、出力端子PO1,PO2,PO3、及びリード端子17,18を含んで構成される。電源抵抗11は、電源線10と出力バッファ回路14の電源電位入力端との接続点N1と電源端子PVddとの間に接続されている。接地抵抗13は、接地線12と出力バッファ回路14の接地電位入力端との接続点N4と接地端子PVssとの間に接続されている。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減する。

【解決手段】内部回路(LK#2)の内部ノードに対応して対応の内部ノードの信号をラッチする複数のラッチ回路(F1−F7)をテストパス(302)に配置する。内部回路のMISトランジスタは、ラッチ回路のMISトランジスタよりスタンバイ状態時にゲートトンネル電流が低減される状態に設定される。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

バッファ回路およびそれを用いた半導体装置、出力回路および電子機器

【課題】高速信号を確実に伝送可能なバッファ回路を提供する。

【解決手段】電流源312は、定電流Icを生成する。第1トランジスタM1は、その一端が電流源312と接続され、その制御端子に入力信号SINが入力される。反転回路314は、入力信号SINを反転および遅延させ、反転入力信号SIN#を生成する。第2トランジスタM2は、その一端が電流源312と接続され、その制御端子に反転入力信号SIN#が入力される。バッファ回路310は、第1トランジスタM1および第2トランジスタM2の、電流源312と共通に接続された一端に生ずる信号SOUTを出力する。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

半導体装置及び情報処理システム

【課題】FETの閾値電圧の変動に起因するアンプのセンスマージンの低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、信号線(BL)に信号を出力する第1の回路(MC)と、FET(Q1、Q2、Q3)と、信号線に基準電位を与える第2の回路(Q5)を備えている。FETQ1はノードN1の電位と駆動信号SETの電位との間の電位差に応じてゲート容量が制御されるゲーテッドダイオードとして機能し、FETQ2は制御信号TGに応じて信号線とノードN1との間の接続を制御し、FETQ3はゲートがノードN1に接続されノードN1の信号電圧を増幅する。導通状態のFETQ2を非導通に制御した後、駆動信号SETの電位は第1の電位から第2の電位に遷移する。FETQ1の閾値電圧の変動量に対応して少なくとも第1の電位をオフセット制御し、FETQ3のセンス増幅時にFETQ1の閾値電圧の変動を補償する。

(もっと読む)

信号伝送装置およびその電流設定方法

【課題】素子の信頼性低下を防ぐ。

【解決手段】送信信号を出力する差動対(3、4)と、差動対の2つの出力端と送信側電源10との間にそれぞれ接続可能とされる送信側負荷抵抗(6、7)と、差動対の2つの出力端にそれぞれ接続され、差動対の2つの出力端の電位を接地電位方向に変化させうる2つの可変電流源(13、14、15、16)と、差動対の2つの出力端の電圧を比較する比較部11と、2つの可変電流源の電流値を設定する制御部12と、を備え、差動対の2つの出力端は、それぞれ受信側負荷抵抗21、22を介して送信側電源より高電位の電源端子23に接続され、制御部12は、信号伝送に先立って可変電流源(15、16)の電流を増加させていった場合に比較部11の比較結果が変化した際の可変電流源(15、16)の電流値に基づいて、信号伝送時における2つの可変電流源の電流値を設定する。

(もっと読む)

半導体装置

【課題】データストローブ信号のスルーレートを変更することなくデータストローブ信号のクロスポイントの電位を調整可能な半導体装置を提供する。

【解決手段】半導体装置は、外部クロックに基づき第1内部クロックを発生する発生回路と、第1内部クロックに基づき第2及び第3内部クロックを生成する分割回路であり第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを調整するエッジ調整回路を含む分割回路と、エッジ調整回路にエッジ調整信号を供給する調整情報保持部と、第2内部クロックに応じて第1データストローブ信号を発生し第3内部クロックに応じて第1データストローブ信号と位相が異なる第2データストローブ信号を発生する出力回路を備え、エッジ調整回路はエッジ調整信号に応じて第3内部クロックの立ち上がり及び立ち下がりの少なくとも一方のタイミングを可変に調整する。

(もっと読む)

半導体装置

【課題】出力特性の自動調整が可能で、かつ低電力で動作できる高速デジタル出力ドライバを有する半導体装置を提供する。

【解決手段】出力用ドライバ3は、参照電流Iref2の大きさに応じて、出力特性の調整が可能なスケーラブル低電圧信号方式のドライバである。出力用ドライバレプリカ4は、出力用ドライバを複製したものであり、自身の出力と基準電圧との差に基づいて、参照電流Iref2の大きさを調整して出力用ドライバ3へ出力する。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、トランジスタの閾値電圧のばらつきに起因する出力電圧のばらつきを抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】6Tr3Cで構成されるインバータ回路において、入力端子IN2に、入力端子IN1に入力されるパルス信号の位相よりも進んだ位相のパルス信号が印加される。これにより、入力端子IN1の電圧がハイからローに変化する際に、トランジスタT5のゲート−ソース間電圧から、トランジスタT5の閾値電圧の影響が取り除かれるので、その後にトランジスタT5がオンしてトランジスタT5に電流が流れたときに、その電流値Idsからも、トランジスタT5の閾値電圧の影響が取り除かれる。

(もっと読む)

半導体集積回路

【課題】 スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定し、半導体集積回路の動作速度を向上する。

【解決手段】 半導体集積回路は、第1高電圧が供給される第1高電圧線を内部電圧線に接続するために第1スイッチ制御信号の活性化に応じてオンする第1スイッチと、第1高電圧を生成するために第1電圧生成信号の活性化に応じて動作する第1電圧生成回路と、第1電圧生成信号の活性化に応じて動作し、第1高電圧と内部電圧線の電圧とを比較し、第1高電圧と内部電圧線の電圧との差が所定値になったときに第1スイッチ制御信号を活性化するレベル比較器とを備えている。第1スイッチの両端に掛かる電圧を比較し、電圧差が小さくなったときに第1スイッチをオンすることで、第1スイッチの信頼性を低下することなく、内部電圧線を所定の電圧に迅速に設定できる。

(もっと読む)

インバータ回路および表示装置

【課題】耐圧を上げることなく、消費電力を低減することの可能なインバータ回路およびそれを備えた表示装置を提供する。

【解決手段】7Tr2Cで構成されるインバータ回路において、容量素子C1がトランジスタTr5のソースに接続されるとともに、トランジスタTr4を介してトランジスタTr7のゲートに接続されている。トランジスタTr7のソースには、トランジスタTr2のゲートが接続されている。これにより、入力端子INに立下り電圧が入力され、トランジスタTr1,Tr3,Tr6がオフしたときに、Vddが充電された容量素子C1によって、トランジスタTr7のゲートがVSS+Vth7以上の電圧にチャージされ、トランジスタTr7がオンし、さらにトランジスタTr2がオンする。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr2Cで構成されるインバータ回路において、トランジスタTr2のソースと低電圧線LLとの間、トランジスタTr5のゲートと低電圧線LLとの間、さらにトランジスタTr2のゲートと低電圧線LLとの間に、入力電圧Vinと低電圧線LLの電圧VLとの電位差に応じてオンオフ動作するトランジスタTr1,Tr3,Tr4が設けられている。トランジスタTr5のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr5のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

受信回路、受信方法及び受信回路を備える通信システム

【課題】従来の受信回路では、耐ノイズ性が低い問題があった。

【解決手段】本発明の受信回路の一態様は、送信回路Txとは異なる電源系において動作する受信回路Rxであって、送信回路Rxが絶縁素子ISOを介して出力する送信信号に基づき生成される受信信号Aの信号レベルの変化に応じて受信データDrx1の論理レベルを切り替える状態保持回路10と、受信データDrx1の論理レベルが切り替わる第1のタイミングから予め設定された第1の期間が経過するまでの期間において、状態保持回路10に受信データDrx1の論理レベルの保持を指示するホールド信号Dを生成する状態保持制御回路20と、を有する。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

スイッチタイミング制御回路及び半導体装置

【課題】回路規模を大きくせずに複数のスイッチを貫通電流が流れないように確実に導通非導通のタイミングを制御するスイッチタイミング制御回路を提供する。

【解決手段】複数のデータフリップフロップが縦続接続され、縦続接続されたデータフリップフロップには共通のクロック信号が接続され、それぞれ前段のデータ出力信号が後段のデータ入力信号として接続され、初段のデータ入力信号には、最終段のデータ出力信号の論理が反転されて接続された分周回路と、複数のデータフリップフロップのうちそれぞれ複数の異なるデータフリップフロップの出力信号が入力端子に接続された複数の組み合わせ論理回路と、複数の組み合わせ論理回路の出力信号によりそれぞれ導通、非導通が制御される複数のスイッチと、を備える。

(もっと読む)

ダイナミック回路の初期化方法

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路の初期化方法は、所定の条件でダイナミックノードの初期化を開始するステップと、複数の入力信号の少なくとも一部について論理評価を行うステップと、論理評価の結果が真のとき、ダイナミックノードの初期化を停止するステップとを備えている。

(もっと読む)

201 - 220 / 1,327

[ Back to top ]