Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

121 - 140 / 1,327

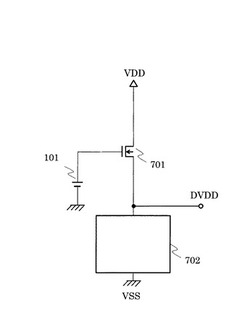

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

信号デスキュー方法および装置

【課題】超低圧VDDデジタル回路においては、クロックスキューは厳密な時間収率の劣化を招く大きな原因であるが、コンピュータによる設計の高度な自動化(EDA)手段の様々なプロセスが存在する中でのスキュー調和がとれたクロックツリーを実現する。

【解決手段】参照信号およびローカル信号を受信し、それらを比較して位相差を検出するための位相比較器、位相差の値に関連して制御信号のオン/オフを切り替えるための制御回路、およびローカル信号バッファーを有し、前記ローカル信号バッファーはnMOSトランジスタおよび/またはpMOSトランジスタを有しており、前記制御信号に応じてホットキャリアインジェクションストレスをnMOSトランジスタまたはpMOSトランジスタに掛けてnMOSトランジスタまたはpMOSトランジスタのしきい値電圧を増加させる。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

送信回路

【課題】従来の送信回路に対して、補正回路の不要、要素回路占有面積の低減の2点において有利であり、出力レベルのHigh側とLow側でエンファシス量のアンバランスを解消することができる送信回路を提供する。

【解決手段】送信回路において、ドライバ回路17は、送信データ信号の電圧値により制御される差動信号入力用のMOSトランジスタM1p,M1nにカスコード接続され、バイアス電圧の電圧値により制御され、駆動電流を流すバイアス電圧印加用のMOSトランジスタM3p,M3nを有し、ドライバ回路16,18は、送信データ信号を遅延した信号の電圧値により制御される差動信号入力用のMOSトランジスタM1p,M1nにカスコード接続されて負荷部に接続され、バイアス電圧の電圧値により制御され、駆動電流を流すバイアス電圧印加用のMOSトランジスタM3p,M3nを有する。

(もっと読む)

レベルコンバータ

【課題】ラッチ回路の初期値が確定可能であり、出力信号の立ち上がり/立ち下がり特性の対称性に優れたレベルコンバータを提供すること。

【解決手段】シフト回路12のラッチ回路31を構成する第1及び第2インバータ回路32,33の出力端子となるノードN1,N2とトランジスタTp1,Tp2との間に初期値設定用のMOSトランジスタTp3,Tp4を挿入接続した。そして、MOSトランジスタTp3のゲートをグランドに接続し、MOSトランジスタTp4のゲートを初期値設定回路34に接続した。初期値設定回路34は、第2の高電位電源VDEが所定レベル以下の場合には該MOSトランジスタTp4のゲート電位を第2の高電位電源VDEとグランドとの間の中間電位に制御し、第2の高電位電源VDEが所定レベルより高い場合には該MOSトランジスタTp4をオンするようそのゲート電位をグランドレベルに制御する。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

半導体装置

【課題】 ゲート−ソース逆バイアス駆動の動作原理を定量化し、MOSTのしきい電圧と動作電圧の関係を明らかにすることにより、逆バイアス駆動の原理を活用した複数のMOSTの組み合わせを用いて、動作電圧1V以下の高速低電圧動作を可能にする。

【解決手段】 低VtのMOSTを含む回路のリーク電流を、MOSTのゲート(G)とソース(S)を逆バイアスする各種の駆動方式によって低減する。低VtのMOSTに各種のG−S逆バイアスを加えることにより、リーク電流の少ない1V以下の高速低電圧CMOS論理回路、あるいはメモリ回路が実現される。

(もっと読む)

半導体装置

【課題】リーク電流を従来よりも抑えること。

【解決手段】本発明の半導体装置1は、外部から信号を供給可能な入力端子10と、内部回路30と、制御部40と、バッファ回路20とを具備している。制御部40は、起動時から所定時間が経過するまでの間にマスク解除信号MASK“H”を出力する。バッファ回路20は、入力端子10に供給される電圧VDD又は電圧GNDを表す信号をマスク解除信号MASK“H”に応じて内部回路30に出力する。本発明の半導体装置1では、外部から入力端子10に信号が供給されているときにノイズが発生しても、バッファ回路20が入力端子10から内部回路30への伝送を有効にする時間以外は無効にしている。このため、マスク回路26によるバッファ回路20と内部回路30との切り離しにより、内部回路30への貫通電流を防止することができる。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

レベルシフト回路および半導体集積回路装置

【課題】回路面積を大きくせずに電源投入時の貫通電流を防止するレベルシフト回路を提供する。

【解決手段】アシスト回路(200)は、第1および第2スイッチ(N21、P21)と、電圧設定回路(300)とを備える。第1および第2スイッチ(N21、P21)は、第1インバータ(101)の出力ノード(BB)と、レベルシフタ(104)の入力ノード(AA)との間に挿入され、第1電源電圧(VDD1)に応答して回路を開閉する。第2電源電圧(VDD2)に基づいて設定電圧を生成する。第1電源電圧(VDD1)が供給される前に第2電源電圧(VDD2)が供給されたときに、レベルシフタ(104)の入力ノード(AA)の電圧を設定電圧に設定する。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

レベルシフト回路およびスイッチング電源装置

【課題】 高耐圧プロセスを使用することなく、回路的に高耐圧化したレベルシフト回路を実現できるようにする。

【解決手段】 一対のCMOSインバータを有し一方のインバータの出力ノードを他方のインバータのPチャネル型MOSトランジスタのゲート端子に交差結合してなるラッチ回路(22)と、該ラッチ回路のいずれか一方の出力ノードに接続されたCMOSインバータからなる出力段(23)とを有するレベルシフト回路において、ラッチ回路を構成する一対のCMOSインバータの各Pチャネル型のMOSトランジスタ(Mp1,Mp2)とNチャネル型のMOSトランジスタ(Mn1,Mn2)との間に、ゲート端子が電源電圧と接地電位の中間の電位が印加される第3電圧端子(FGND)に接続されたPチャネル型のMOSトランジスタ(Mp4,Mp5)をそれぞれ直列形態で設けた。

(もっと読む)

半導体装置、回路基板装置及び情報処理装置

【課題】小規模な回路で送受信に応じた最適なインピーダンス調整を行う。

【解決手段】選択部15が、送信部11のインピーダンス調整時か、受信部12のインピーダンス調整時かに応じて異なる基準電圧を選択し、選択した基準電圧を基準電圧生成部14に生成させ、基準電圧生成部14が、選択部15により選択された基準電圧を生成して、インピーダンス調整部13に入力し、インピーダンス調整部13が、入力された基準電圧に応じて、送信部11または受信部12のインピーダンスを別々に調整する。

(もっと読む)

差動信号出力装置、および、携帯機器

【課題】出力信号のスルーレートをより適切に制御することが可能な差動信号出力装置を提供する。

【解決手段】差動信号出力装置は、差動信号およびコモンモード信号を重畳して出力するための第1の送信端子および第2の送信端子を備える。差動信号出力装置は、データ信号に応じて前記差動信号を生成し前記第1の送信端子および前記第2の送信端子に出力する差動信号生成回路を備える。差動信号出力装置は、クロック信号に応じて前記コモンモード信号を生成し前記第1の送信端子および前記第2の送信端子に出力し、且つ、制御信号に応じて前記コモンモード信号のスルーレートを制御するコモンモード信号生成回路を備える。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

121 - 140 / 1,327

[ Back to top ]