Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

61 - 80 / 1,327

半導体装置

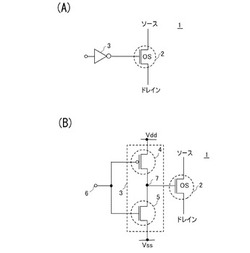

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

半導体装置

【課題】新たな構成の半導体装置を提供する。

【解決手段】半導体装置は、p型の第1のトランジスタ、n型の第2のトランジスタ、第3のトランジスタ及び第4のトランジスタを有する。第3のトランジスタのソース又はドレインの一方は、第1の電位を供給することができる機能を有する配線に接続され、他方は、第1のトランジスタのソース又はドレインの一方に接続される。第2のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と接続され、他方は、第4のトランジスタのソース又はドレインの一方に接続される。第4のトランジスタのソース又はドレインの他方は、第1の電位よりも低い第2の電位を供給することができる機能を有する配線に接続される。第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、第1及び第2の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】半導体を用いた半導体装置として、論理回路がある。論理回路にはダイナミック論理回路とスタティック論理回路とがあり、トランジスタ等を用いて構成される。ダイナミック論理回路は情報を一定期間保持することができる。そのため、ダイナミック論理回路は、スタティック論理回路と比較して、トランジスタからのリーク電流が問題となる。

【解決手段】論理回路は、オフ電流が小さい第1のトランジスタと、ゲートが電気的に接続された第2のトランジスタと、を有し、第2のトランジスタのゲートのノードには第1のトランジスタを介して電荷が供給される。ノードに対して、複数の容量を介して電荷を供給する。電荷の状態に応じて、第2のトランジスタのオン、オフが制御される。第1のトランジスタは、チャネル形成領域に酸化物半導体を有する。

(もっと読む)

半導体装置

【課題】信号転送ラインの充放電によって消費される電力を低減する。

【解決手段】フリップフロップ構成のアンプ回路AMPを含むレシーバ回路R0kと、データバスDBとレシーバ回路R0kの入力端T2との間に挿入され、データバスDBがVPERI−NVthに達するとオフするトランジスタM7を備える。本発明によれば、トランジスタM7によって入力端T2の振幅が制限されることから、データバスDBがローレベルからハイレベルに変化する際の転送速度が向上する。しかも、アンプ回路AMPがフリップフロップ構成を有していることから、フリップフロップが反転した後は貫通電流が生じない。これにより、消費電力がより一層低減される。

(もっと読む)

回路装置及び電子機器

【課題】断熱的回路動作により消費電力を抑制することができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、第1の基準電圧を基準として電圧が周期的に変化する第1の電源電圧VP、及び第2の基準電圧を基準として電圧が周期的に変化する第2の電源電圧VMが供給されて断熱的回路動作を行う断熱的回路100と、第1の直流電源電圧VDD及び第2の直流電源電圧VSSが供給されて動作する非断熱的回路120と、断熱的回路100と非断熱的回路120との間に設けられるラッチ回路210とを含む。ラッチ回路210は、断熱的回路100からの出力信号D2を、第1の電源電圧VPが極大となり第2の電源電圧VMが極小となるタイミングに対して設定された第1のラッチ期間においてラッチし、出力信号D2のラッチ信号Q2を非断熱的回路120に対して出力する。

(もっと読む)

イネーブル信号生成回路

【課題】後段のイネーブル回路を確実に制御し、また電源電圧が高くなっても消費電流が増大しないようにする。

【解決手段】制御入力端子1にゲートが接続されソースがトランジスタMN2を介して接地に接続されたトランジスタMN1と、トランジスタMN1のドレインと電源VDDとの間に接続された抵抗R2と、抵抗R2の両端にソースとドレインが接続されたトランジスタMP1と、トランジスタのMP1ゲートとソース間に接続された抵抗R3と、ソースがトランジスタMP1のゲートに接続されゲートがトランジスタMP1のドレインに接続されドレインが負荷回路3に接続されたトランジスタMP2とを備え、トランジスタMP2のゲートを制御出力端子2に接続した。

(もっと読む)

出力バッファ回路

【課題】 著しい遅延の増大を招くことなく、出力バッファ回路の貫通電流を防止する。

【解決手段】 出力段駆動部100は、出力信号VOUTを立ち下げる場合、Pチャネルトランジスタ201をOFFに遷移させ、そのドレイン電流が閾値電流Ith1を下回ったとき、Nチャネルトランジスタ202をONに遷移させ、出力信号VOUTを立ち上げる場合、Nチャネルトランジスタ202をOFFに遷移させ、そのドレイン電流が閾値電流Ith2を下回ったとき、Pチャネルトランジスタ201をONに遷移させる。閾値設定部130は、入力信号VINに出力信号VOUTを立ち下げる変化があったとき、Pチャネルトランジスタ201のドレイン電流に応じた値に閾値電流Ith1を設定し、閾値設定部140は、入力信号VINに出力信号VOUTを立ち上げる変化があったとき、Nチャネルトランジスタ202のドレイン電流に応じた値に閾値電流Ith2を設定する。

(もっと読む)

半導体装置

【課題】出力インピーダンスを切り替えた場合の出力トランジスタに対する電源配線抵抗等の見かけ上の変動を抑制し、出力インピーダンスを切り替えた際の出力インピーダンスの誤差を低減する。

【解決手段】本発明による半導体装置は、電源端子に接続された電源配線(10)と、出力端子に接続された信号配線(20)と、前記電源配線と前記信号配線との間に並列接続された複数のトランジスタ(TP1〜TP7,TN1〜TN7)と、前記複数のトランジスタのうち、特定のトランジスタ(TP4,TN4)を基準として前記電源配線および前記信号配線の長手方向において相互に対照をなす位置関係にあるトランジスタを単位として前記複数のトランジスタを選択的に活性化させる制御回路とを備える。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

記憶回路

【課題】消費電力を抑えることができる記憶回路の提供を目的の一つとする。

【解決手段】記憶回路に電源が供給されない間は、揮発性のメモリに相当する記憶部に記憶されていたデータを、不揮発性のメモリに相当する記憶部に設けられた容量素子によって保持する記憶回路である。不揮発性記憶部では、酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、容量素子に保持された信号は長期間にわたり保持することができる。こうして、記憶回路は電源の供給が停止している間も論理状態(データ信号)を保持することが可能である。また酸化物半導体層にチャネルが形成されるトランジスタのゲートに印加する電位を、電源電位を供給する配線と前記トランジスタのゲートとの間に設けられた昇圧回路によって高くすることで、1つの電源電位であっても誤動作なくデータ信号の保持を行うことが可能である。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

リンギング抑制回路

【課題】より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、NチャネルMOSFET7を接続し、制御回路14は、伝送線路3を介して伝送される差動信号のレベルがハイからローに変化したことを検出すると、NチャネルMOSFET7を一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間にNチャネルMOSFET7が導通することで信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生を確実に抑制する。

(もっと読む)

半導体装置

【課題】貫通電流を少なくできる半導体装置を提供する。

【解決手段】データを出力する出力部を各々備えた複数の半導体チップと、出力部の各々と接続された配線と、配線を介して複数の半導体チップの各々からデータを受け付ける受付部と、を含み、出力部が順番に駆動する半導体装置にて、出力部の各々は、オン状態時の抵抗値を変更可能であり、自己の駆動開始時から自己の次に駆動を開始する出力部の駆動開始時の前のタイミングまでの第1期間の間は、オン状態時の抵抗値を第1抵抗値にしてデータを配線に出力し、第1期間が経過した時点から自己の駆動終了時までの第2期間の間は、オン状態時の抵抗値を第1抵抗値よりも大きい第2抵抗値にしてデータを配線に出力する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

レベルシフト回路

【課題】更なる消費電力低減および速度向上が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路2Aは、第1PMOSトランジスタ31、第2PMOSトランジスタ32、第1NMOSトランジスタ41および第2NMOSトランジスタ42を備える他、第3NMOSトランジスタ43および第4NMOSトランジスタ44をも備える。第1PMOSトランジスタ31および第2PMOSトランジスタ32それぞれのソース端子は、第1基準電位Vddlより高い第2基準電位Vddhに接続される。第3NMOSトランジスタ43および第4NMOSトランジスタ44それぞれのドレイン端子も第2基準電位Vddhに接続される。

(もっと読む)

61 - 80 / 1,327

[ Back to top ]