Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

141 - 160 / 1,327

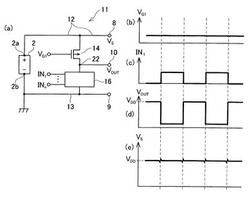

反転電圧出力回路

【課題】入力信号の変化に応じて直流電源の非接地電圧と接地電圧の間で反転する電圧を出力する回路であり、非接地端子に接続されている電源線に生じる電圧変動を抑制する。

【解決手段】電流制限素子14とスイッチング回路16が直列に接続されており、電流制限素子とスイッチング回路の中間点22の電圧を出力する。スイッチング回路の導通時にスイッチング回路を流れる電流が電流制限素子によって制限される。直流電源の非接地端子に接続されている電源線12に生じる電圧変動が抑制され、電源線12に接続されているアナログ回路等の動作が安定する。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

入出力回路

【課題】昇圧した電圧でLCDを駆動するような場合でも、その共用の入出力端子から実用的な出力データ信号の出力が可能となる。

【解決手段】入出力回路100において、スリーステート出力バッファが出力データ信号とLCD駆動信号の両方に対してそれぞれ第1、第2出力バッファ106、108として設けられ、第1出力バッファ106を構成するPチャンネルMOSトランジスタ116のソース端子に電源電圧V1が供給され、且つ出力データ信号が出力として選択されていない状態でPチャンネルMOSトランジスタ116、118のバックゲート端子に電源電圧V1から昇圧された昇圧電圧V2が供給され、更に、第2出力バッファ108を構成するPチャンネルMOSトランジスタ116のソース端子とバックゲート端子とに昇圧電圧V2が供給される。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

レベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置

【課題】向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

【解決手段】本発明のレベル変換器は、入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生する第1及び第2電圧変換回路を含み、第1及び第2電圧変換回路は同一の構造を有し、入力ノード及び出力ノードの間に並列に連結される。

(もっと読む)

二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路

【課題】単位回路の、高速動作と未使用時(注を入れる)または定常時または待機時における消費電力の減少を両立させた二重絶縁ゲート電界トランジスタを用いたMOSトランジスタ回路およびそれを用いたCMOSトランジスタ回路、SRAMセル回路、CMOS−SRAMセル回路、集積回路を提供することである。

【解決手段】四端子二重絶縁ゲート電界効果トランジスタからなるMOSトランジスタ回路において、前記四端子二重絶縁ゲート電界効果トランジスタの一方のゲートを入力端子とし、他方のゲートに抵抗の一方の端を接続し、ソースを第一の電源に接続し、ドレインを出力端子とすると供に負荷素子を通して第二の電源に接続し、前記抵抗の他端を一定電位の第三の電源に接続したことを特徴とする。

(もっと読む)

入力バッファ、及び信号入力方法

【課題】半導体集積回路に対する高周波数帯のノイズの混入を防止する。

【解決手段】本発明による入力バッファは、半導体集積回路の外部からの入力信号を反転して半導体集積回路の内部に出力する出力インバータ回路2と、出力インバータ回路2の反転動作よりも早く入力信号の電圧V1の固定動作を開始する固定回路とを具備する。

(もっと読む)

出力回路

【課題】入力信号が電源電圧の半分程度である場合に、低耐圧のトランジスタを用いながら高電圧の信号を出力する回路を提供する。

【解決手段】入力信号が電源電圧の半分程度である場合には、図1に示すような第3の第1導電型トランジスタを備える出力回路を考える。図1において、入力信号が電源電圧の半分程度まで上昇すると、第1及び第2の第2導電型トランジスタはオン状態になる。すると、出力信号は0Vに向かって低下を始める。その際に、出力信号の低下に伴って第3の第1導電型トランジスタがオン状態になり、第2の第1導電型トランジスタをオフすることができる。その結果、出力信号に対する電源電圧の影響を排除し、ロウレベルとして0Vを出力する出力回路が提供される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】伝送線路の特性インピーダンスと終端抵抗のインピーダンス整合を容易とする。

【解決手段】差動終端抵抗回路3は直列の第1と第2の素子Q1、Q2を含み、レプリカ抵抗回路4は直列の第3と第4の素子Q3、Q4を含み、制御電圧生成回路5は制御差動増幅器DA2と直列の制御素子Q8と第1と第2の電圧降下回路R7、8;R9とを含む。増幅器DA2の非反転入力と反転入力に、基準電圧Vrefと回路4の素子Q3、Q4のレプリカ抵抗電圧Vrcmがそれぞれ供給される。回路5の第1と第2のレプリカ抵抗制御電圧Vcont0、1は、回路4の素子Q3、Q4の制御入力にそれぞれ供給される。差動終端抵抗回路3の素子Q1、Q2は、第2のレプリカ抵抗制御電圧Vcont1と第2の電圧降下回路R9の電圧降下との合計電圧である差動終端抵抗制御電圧Vcont1.5に基づく制御出力電圧Voutによって制御される。

(もっと読む)

半導体集積回路およびその動作方法

【課題】多ビットの差動受信回路および差動終端抵抗を内蔵して、半導体チップ面積と消費電流の増大を軽減する。

【解決手段】複数の差動受信回路2A、B〜Nと複数の差動終端抵抗回路3A、B〜Nと複数の制御電圧供給回路6A、B〜Nに、レプリカ抵抗回路4と制御電圧生成回路5が共用される。複数の回路6A、B〜Nの各回路は、第1非反転入力と第1反転入力と出力を有する差動増幅器DA1を含む。第1供給回路6Aの第1差動増幅器の第1非反転入力と、第2供給回路6Bの第2差動増幅器の第1非反転入力と、第N供給回路6Nの第N差動増幅器の第1非反転入力とに、生成回路5から生成される差動終端抵抗制御電圧Vcont1.5が共通に供給される。第1差動増幅器の出力電圧VoutAと第2差動増幅器の力電圧VoutBと第N差動増幅器の出力電圧VoutNとは、第1と第2と第Nの差動終端抵抗回路3A、3B、3Nにそれぞれ供給される。

(もっと読む)

パワーゲーティングCMOS回路及びスーパーカットオフCMOS回路におけるチャージリサイクリング

【課題】MTCMOS回路やSCCMOS回路等のパワーゲーティングされた回路におけるモード移行時のパワー消費の低減や、ウェークアップ時間や、パワーゲーティング構成により生じるノイズを低減する。

【解決手段】第1の回路ブロックと第1のスリープトランジスタとの間の第1の仮想グラウンドノードと、第2の回路ブロックと第2のスリープトランジスタとの間の第2の仮想グラウンドノードと、第1の仮想グラウンドノードを第2の仮想グラウンドノードに接続し、第1の回路ブロックによるアクティブモードからスリープモードへの移行、及び第2の回路ブロックによるスリープモードからアクティブモードへの移行、またはその逆の間に第1の回路ブロックと第2の回路ブロックとの間のチャージリサイクリングを可能とするトランスミッションゲート(TG)またはパストランジスタとを有する回路である。

(もっと読む)

セレクタ回路、プロセッサシステム

【課題】本実施例におけるセレクタ回路は、所定ノードに対する充電と放電により入力信号の選択動作を行う前段の選択回路において余計な消費電流が生じるのを防止し、回路の消費電力を低減することを目的とする。

【解決手段】本実施例におけるセレクタ回路は、第1選択制御信号に基づいて複数の入力信号のうちの1つを選択して第1出力信号を出力する複数の第1選択回路と、第2選択制御信号に基づいて複数の第1出力信号のうちの1つを選択して出力する第2選択回路を含み、第1選択回路の各々が、第1期間に第1ノードと第1電源を電気的に接続して第1ノードを充電する充電回路と、第1ノードと第2電源の間に設けられ、第1期間の後に続く第2期間に第1選択制御信号、複数の入力信号及び第2選択制御信号に基づいて、第1ノードと第2電源を電気的に接続して、充電された第1ノードを放電させる否かを制御する放電制御回路を含むことを特徴とする。

(もっと読む)

キャリブレーション回路および半導体装置に関する。

【課題】出力バッファのI−V特性が出力バッファ用の電源電圧に応じて変化しても、出力バッファのI−V特性に対して規定を満足させることを可能にする。

【解決手段】レプリカ回路(110、120、130)は、インピーダンスが可変であり、当該インピーダンスに応じた電圧を出力する。参照電圧生成部(141、142)は、出力バッファ用の電源電圧に依存する参照電圧を出力する。比較部(151、152)は、レプリカ回路の出力電圧と参照電圧とを比較する。調整部(160、170、180、191、192、110a、120a、130a)は、比較部の比較結果に応じて、レプリカ回路のインピーダンスを調整する調整部(160、170、180、191、192、110a、120a、130a)。

(もっと読む)

入出力バッファ回路

【課題】チップ面積を削減させると共に、動作周波数をより高くする。

【解決手段】外部接続端子VIOと、ソースを電源に接続し、ドレインを外部接続端子VIOに接続し、ゲートに駆動信号が供給可能とされるPMOSトランジスタMP7と、PMOSトランジスタMP7のバックゲートと電源間に接続され、開閉が制御されるバックゲート制御回路22と、PMOSトランジスタMP7のドレイン・ゲート間に接続され、開閉が制御されるゲート制御回路23と、PMOSトランジスタMP7のゲートと駆動信号が供給される駆動端との間に接続され、開閉が制御される駆動側制御回路24と、を備え、外部接続端子VIOから駆動信号に係る信号を出力しないハイインピーダンス状態において、バックゲート制御回路22および駆動側制御回路24が開放状態とされ、ゲート制御回路23が短絡状態とされる。

(もっと読む)

レベルシフト回路及び通信回路

【課題】 入力信号の電圧振幅の最大値と同電圧を供給する電源電圧の入力を必要とせず、異なる電圧振幅の入力信号が入力された場合でも動作可能であり、貫通電流による消費電力の増大を低減できるレベルシフト回路及び通信回路を提供する。

【解決手段】 出力信号の電圧振幅の最大値と同電圧を供給する第1電圧源と内部出力ノードN1の間に設けられた負荷抵抗回路R1と、入力信号の入力電圧を受け付け、制御ノードN2の電圧値を入力信号の電圧振幅の最大値に対応する制御電圧値に保持する電圧記憶回路11と、内部出力ノードN1と入力信号の入力ノードN3の間に設けられ、制御ノードN2の電圧と入力信号の電圧の電圧差に応じてON状態とOFF状態が切り替わるように構成され、入力信号の電圧値が電圧振幅の最大値の場合にOFF状態に、入力信号の電圧値が電圧振幅の最小値の場合にON状態になる第1スイッチング回路MN1と、を備える。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

141 - 160 / 1,327

[ Back to top ]