Fターム[5J056DD13]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | FET (1,892) | MISFET、MOSFET、IGFET (1,327)

Fターム[5J056DD13]に分類される特許

101 - 120 / 1,327

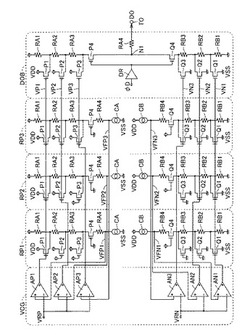

半導体装置

【課題】可変抵抗回路の抵抗値の調整可能範囲が大きな半導体装置を提供する。

【解決手段】この半導体装置は、複数組の抵抗素子RA,RBおよび複数組のトランジスタP,Qを含む出力バッファDOBと、複数のレプリカ回路RPと、複数組の演算増幅器AP,ANとを備え、出力バッファDOBの出力インピーダンスZp,Znが所定値になるように、複数組のトランジスタP,Qのドレイン電流を調整する。したがって、製造プロセスなどの変動によって抵抗素子RA,RBの抵抗値が大きく変動した場合でも、出力インピーダンスZp,Znを所定値に設定できる。

(もっと読む)

半導体集積回路の出力バッファ回路、及び半導体集積回路

【課題】半導体集積回路の出力バッファ回路において電流の流れ込みを防止し、動作を高速化し、回路規模を削減する。

【解決手段】出力バッファ回路11は、常時オンの電源VDD、オン/オフ制御される電源VDD1、電源VDD1の電位を反転した反転信号INVOUTを出力するインバータ回路41、トランジスタP1A1,PP2,PP3、トランジスタP1A1を制御するドライブ回路51を備える。トランジスタP1A1は、入出力端子E1Aに接続されたドレイン、電源VDD1に接続されたソース、電源VDDに接続されたバックゲート、ドライブ回路51に接続されたゲートを有する。トランジスタPP2,PP3のバックゲート及びトランジスタPP2のソースは電源VDDに接続され、トランジスタPP2のゲート及びトランジスタPP3のソースは電源VDD1に接続され、トランジスタPP3のゲートには反転信号INVOUTが入力される。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】7Tr3Cで構成されるインバータ回路1において、入力端子IN1から印加される電圧に応じてオンオフするトランジスタT3と、制御素子10とを介して、入力電圧Vin2がトランジスタT2のゲートに入力される。入力電圧Vin1,Vin2がともにハイレベルの電圧Vddとなっている期間においては、入力電圧Vin3がハイレベルの電圧Vddとなっているときだけ、トランジスタT1,T2の双方のゲートにオン電圧が印加される。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

判定帰還型イコライズ回路

【課題】低電圧動作及び高速動作が可能な、判定帰還型のイコライズ回路を提供すること。

【解決手段】本発明にかかる判定帰還型イコライズ回路は、ダイナミック型サンプル回路1、ラッチ回路2及びバッファ回路3を備える。ダイナミック型サンプル回路1は、入力データIN及びINB、フィードバック信号FB1〜FBn及びFBB1〜FBBnをサンプリングし、サンプリングした信号を加算したサンプル信号SS及びSSBを出力する。ラッチ回路2は、差動サンプル信号サンプル信号SS及びSSBの差電圧を増幅し、増幅した信号を保持する。なお、ラッチ回路2は、差動サンプル信号SS及びSSBが過渡状態にあるときの差電圧を増幅する。バッファ回路3は、ラッチ回路2により保持された信号を出力データOUT及びOUTBとして出力する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

半導体装置

【課題】切り替えスイッチのオンオフに伴うノイズがバイアスラインに重畳するのを防ぐ。

【解決手段】バイアス電流が流れるバイアスラインVLと、バイアス電流の量を制御信号DDに基づいて切り替える切り替えスイッチ70と、制御信号DDが供給される制御ラインとバイアスラインVLとの間の寄生容量を介して制御信号DDの変化時に生じるバイアスラインVLの電位変動を相殺する相殺回路91〜93とを備える。本発明によれば、切り替えスイッチ70のオンオフに伴ってバイアスラインVLに生じるノイズを相殺することが可能となる。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

信号伝達回路及びこれを用いたスイッチ駆動装置

【課題】入力信号をレベルシフトして出力するレベルシフト回路を有しながらも、電源の電圧変動等による誤信号の出力を抑えることが可能となる信号伝達回路を提供する。

【解決手段】第1入力信号および第2入力信号の各々をレベルシフトし、それぞれ第1シフト済み信号および第2シフト済み信号として出力する、レベルシフト回路を備え、レベルシフト回路は、第1入力信号に応じて開閉するスイッチング素子と抵抗を有する第1直列回路、および、第2入力信号に応じて開閉するスイッチング素子と抵抗を有する第2直列回路が、電源と接地端との間において互いに並列に設けられており、第1直列回路上の電圧を第1シフト済み信号として、第2直列回路上の電圧を第2シフト済み信号として、それぞれ出力するようになっており、接地端から第1直列回路および第2直列回路に向かって逆電流が流れることを防止する、逆流防止部を備えた信号伝達回路とする。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

低リーク電圧検出回路

【課題】ゲート電極駆動電圧信号が不十分な電圧のためにリーク電流が発生することのない低リーク電圧検出回路及び方法を提供する。

【解決手段】伝送ゲート202、フィードバック通路204、制御器200を備え、第1の電位によって給電された第1の装置と第2の電位によって給電された第2の装置との間に置かれた低リーク電圧検出回路である。第1の装置と第2の装置との間における電位のミスマッチは、リーク電流が第2の装置の入力段を流れることを招く可能性がある。低リーク電圧検出回路を採用することによって、第1の装置の発生した高論理レベルは、対応的にほぼ第2の電位の振幅と等しい高論理レベルに転換される。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時の貫通電流が、ロジック回路を構成するP型トランジスタとN型トランジスタの閾値電圧ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタを有し、内部電源電圧の値が、N型トランジスタの閾値電圧と、P型トランジスタの閾値電圧の絶対値の和に基づいて与えられ、前記N型トランジスタは、前記ロジック回路内部のN型トランジスタと同一の製造プロセスで形成され、前記P型トランジスタは、前記ロジック回路内部のP型トランジスタと同一の製造プロセスで形成される、内部電源電圧生成回路、とした。

(もっと読む)

出力回路

【課題】スキューの少ない出力信号を出力する回路の実現。

【解決手段】差動入力信号INN,INPを受けて、差動駆動信号を出力する駆動回路BF1,BF2;BF3,BF4と、共通の定電流源12に接続され、差動駆動信号に応じて逆相のスイッチ動作を行う2個のトランジスタMN1,MN2を有する差動出力部と、駆動回路の2個の駆動部の電源15,16の電位を、定電流源12と2個のトランジスタの接続ノードTailの電位に応じた電位にするレベル調整回路AMP1,AMP2と、を有する出力回路。

(もっと読む)

送信ドライバ回路

【課題】信号の伝送速度が速い差動通信においても、コモンモード電圧の発生を適切に抑制できる送信ドライバ回路を提供する。

【解決手段】レベルホールド回路3は、通信信号出力部2が差動信号の電圧レベルを変化させる際に伝送線路5に発生するコモンモード電圧の変化を検出し、その検出レベルをレベルホールドする。そして、信号処理回路4は、前記検出レベルを上限基準値及び下限基準値と比較し、検出レベルが上限基準値を上回るか又は下限基準値を下回ると、次回の信号送信時に発生するコモンモード電圧を低減するように、通信信号出力部2による電圧の出力状態を調整する。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S5に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。第1のトランジスタT1のゲート端子には、伝送路27の波形を整形するためのキャパシタC1の第1端が接続され、キャパシタC1の第2端はクランプ回路46に接続されている。クランプ回路46は、プルダウン用のトランジスタT1と同様に、キャパシタC1の第2端が接続されたノードNDの電位を制御する。

(もっと読む)

レベルシフト回路

【課題】入力信号のレベルが低電圧であっても、信号レベルの変換を高速かつ確実に行うことのできるレベルシフト回路を提供する。

【解決手段】 実施形態のレベルシフト回路は、厚膜のPMOSトランジスタTP1(TP2)および厚膜のNMOSトランジスタTN1(TN2)からなる一対の相補回路を有し、厚膜のNMOSトランジスタTN1(TN2)のゲートに入力された低電圧レベルの信号A(/A)を、厚膜のPMOSトランジスタTP2(TP1)を介して昇圧し、高電圧レベルの信号Z(/Z)を出力する。この一対の相補回路のそれぞれの出力端子と接地端子GNDとの間には、ブースター回路11(12)がそれぞれ接続されている。ブースター回路11(12)は、高電圧レベルの出力信号/Z(Z)の立ち下りを加速する。

(もっと読む)

101 - 120 / 1,327

[ Back to top ]